У роботі сучасних пристроїв ЦП від 80% до 90% споживання енергії та затримки часу спричинені переміщенням даних між ЦП і пам’яттю поза мікросхемою. Щоб зменшити цю проблему щодо продуктивності, розробники додають додаткову вбудовану пам’ять до своїх процесорів. Традиційно SRAM була найпоширенішим типом вбудованої пам'яті процесора. На жаль, розмір SRAM наразі обмежений сотнями мегабайт. Це обмеження вбудованої пам’яті може бути недостатнім для передових програм.

Майбутні додатки ЦП, такі як програмування мовної моделі штучного інтелекту та обробка зображень для відео 8K UHD, вимагатимуть пропускної здатності доступу до пам’яті вводу/виводу в діапазоні 10 терабайт/с. Щоб задовольнити ці вимоги до пропускної здатності, об’єм внутрішньої пам’яті центрального процесора повинен перевищувати 1 терабайт. Можливо, знадобиться альтернатива SRAM, щоб задовольнити ці майбутні вимоги до пам’яті на кристалі. Одним із можливих рішень цієї проблеми було б використання резистивної оперативної пам’яті (ReRAM). [1,2,3]

Пристрій ReRAM — це енергонезалежна комірка пам’яті, яка містить матеріали мемристора. Ці матеріали виконують роль діелектричного ізолятора. При застосуванні досить високої напруги утворюється шлях провідності. Типові матеріали пам'яті, що використовуються як мемристори, включають HfO2, Та2O5, і TiO2. [4] Резистивний стан комірки пам'яті можна зчитувати за допомогою електронних схем, щоб визначити, чи комірка пам'яті запрограмована чи стерта, таким чином ідентифікуючи стан біта пам'яті. Комірки пам’яті ReRAM можна складати вертикально, як архітектура 3D-NAND, щоб збільшити щільність зберігання.

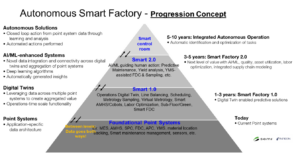

У цій статті, Віртуальне виготовлення SEMulator3D використовуватиметься для пошуку шляхів процесу та візуалізації потенційних архітектур 3D ReRAM. Ми оцінимо опір комірки як функцію форми комірки пам’яті разом із продуктивністю Id-Vg вбудованого канального транзистора в пристрої ReRAM.

3D-модель ReRAM показана на малюнку 1. Пристрій має 64 шари словесних рядків (WL) зі стовпами, розміщеними в гексагональному масиві. Лінії сформовані з чергуванням шарів металевих провідників і оксидного діелектрика. Стовпи витравлюються через WL, а потім на бічні стінки стовпів наноситься тонкий шар матеріалу пам’яті. Матеріал пам’яті видаляється з нижньої та верхньої частин стовпів, залишаючи лише матеріал на бічних стінках стовпа. Потім опори заповнюються тугоплавким металом і вольфрамом.

Під шарами масиву розташовані контакти та металеве з’єднання з витоком, стоком і затворами польових транзисторів із затвором (GAA FET). Стік транзистора з’єднується зі стовпом масиву пам’яті та об’єднується зі схемою WL, щоб забезпечити функціонування кожної комірки пам’яті.

Осередок пам'яті складається з двох металевих електродів: металевого провідника та тугоплавкого металевого електрода (рис. 2). Під час віртуального моделювання процесу цього пристрою ми будемо використовувати змінні процесу для налаштування та скидання мемристора. Навмисно прикладена напруга створить мікроскопічні провідні шляхи, які називаються провідними нитками. Коли застосовуються електричні сигнали різної полярності, заряджені іони всередині мемристора рухаються, утворюючи (встановлюючи) або розчиняючи (скидаючи) провідну нитку.

Опір провідної нитки змінюється при різних напругах програми. Стан низького опору знаходиться в діапазоні 10 кОм (встановлено), а стан високого опору в діапазоні 1 М Ом (скидання). [5] Ми розробили віртуальну модель, щоб продемонструвати опори перемикання пристрою 3D ReRAM, результати відображені на малюнку 3. Стан мемристора з високим опором приблизно в 100 разів перевищує опір, ніж стан із низьким опором.

Потім було виконано віртуальний план експериментів (DOE), щоб краще зрозуміти кореляцію між коефіцієнтом опору комірки пам’яті та розміром і формою комірки пам’яті. Змінними експерименту були опори CD, товщина WL і товщина мемристора. Аналіз результатів DOE показує, що опора CD і товщина мемристора спричинили найбільш значний відгук. На рисунку 4 зображено контурний графік співвідношення опору комірки пам’яті в залежності від цих двох змінних. Відбулася 3-кратна зміна опору комірки пам’яті для високих значень радіуса опори та товщини мемристора. Відмінності у формі комірки пам’яті в досліджуваному діапазоні не вплинуть на здатність зчитувати стани пам’яті мемристора, але можуть вплинути на здатність розпізнавати стани програми в багатобітовому пристрої на комірку.

Мемристор можна запрограмувати за допомогою струму < 0.10 мкА та напруги < 0.5 В. Ці налаштування напруги та струму дозволять легко інтегрувати мемристори (пам’ять ReRAM) як вбудовану пам’ять у передові логічні пристрої. Симуляція пристроїв SEMulator3D раніше продемонструвала, що транзистор GAA FET під матрицею повинен бути в змозі керувати напругою та струмом, необхідними для встановлення та скидання станів мемристорної комірки пам’яті. [6]

Двома основними проблемами сучасних пристроїв ЦП є споживання енергії та час затримки, спричинені переміщенням даних між ЦП і зовнішньою пам’яттю. Збільшення розміру вбудованої пам'яті може вирішити ці проблеми. У цьому дослідженні ми використали SEMulator3D, щоб дослідити інтеграцію альтернативи SRAM (ReRAM) для ЦП для вбудованої пам’яті. Ми використали віртуальну модель, щоб краще зрозуміти кроки процесу та потенційні проблеми з компонуванням окремих комірок мемристора. Ми також виконали дослідження, щоб перевірити стани встановлення та скидання мемристора та вплив розмірів пристрою (форми та розміру комірки пам’яті) на опір лінії зв’язку. Ми підкреслили, що вбудовану пам’ять ReRAM можна інтегрувати з розширеною логікою за допомогою електричного виходу транзистора GAA pFET для налаштування та скидання осередків мемристора. Ці результати підтверджують, що резистивна пам’ять з довільним доступом (ReRAM) є багатообіцяючою альтернативою вбудованій пам’яті SRAM для майбутніх логічних додатків з високою пропускною здатністю.

посилання

- Ланца, Маріо (2014). «Огляд резистивного перемикання в діелектриках з високим k-м: нанорозмірна точка зору за допомогою провідного атомно-силового мікроскопа». Матеріали, вип. 7, випуск 3, стор. 2155-2182, doi:10.3390/ma7032155.

- N. Sedghi та інші, «Роль легування азотом у ALD Ta2O5 та його вплив на багаторівневе перемикання клітинок у RRAM», березень 2017 р., Applied Physics Letters, DOI:10.1063/1.4978033

- Y. Bai, та інші, «Дослідження багаторівневих характеристик тривимірної пам’яті з вертикальним резистивним перемиканням», наукові звіти, том 3, номер статті: 4 (5780)

- Чен, Ю.К., Саркар, С., Гіббс, Дж.Г., Хуанг, Ю., Лі, Дж.К., Лін, Ч.І., і Лін, Ч. (2022). «Наноспіральна подвійна функціональна резистивна пам’ять для застосування в масиві поперечних планок малої потужності», ACS Applied Engineering Materials, 1(1), 252-257.

- Y. Wu та ін., «HfOx RRAM нанометрового масштабу», IEEE Electron Device Letters, Том: 34, Випуск: 8, серпень 2013), doi: 10.1109/LED.2013.2265404

- В. Срінівасулу та ін., «Аналіз схем та оптимізація GAA Nanowire FET Towards Low Power and High Switching», 11 листопада 2021 р., Computer Science, doi:10.1007/s12633-022-01777-6.

Бретт Лоу

Бретт Лоу є менеджером у групі процесів напівпровідників та інтеграції в Coventor, дослідницькій компанії Lam. Він працював у розробці напівпровідникових технологій понад 35 років. Він розпочав свою кар’єру в Philips Semiconductors, де працював у виробництві та розробці процесів як інженер-технолог у сферах фотолітографії, сухого травлення та мокрого процесу. Потім він провів вісім років у Zilog, працюючи над розробкою процесів установки. Пізніше Бретт приєднався до Micron Technology, де працював над розробкою та інтеграцією процесів DRAM і 3D NAND. У Coventor він зосереджується на підтримці клієнтів компанії в їх 3D моделюванні напівпровідникових процесів і вимогах до розробки технологій.

- Розповсюдження контенту та PR на основі SEO. Отримайте посилення сьогодні.

- PlatoData.Network Vertical Generative Ai. Додайте собі сили. Доступ тут.

- PlatoAiStream. Web3 Intelligence. Розширення знань. Доступ тут.

- ПлатонЕСГ. вуглець, CleanTech, Енергія, Навколишнє середовище, Сонячна, Поводження з відходами. Доступ тут.

- PlatoHealth. Розвідка про біотехнології та клінічні випробування. Доступ тут.

- джерело: https://semiengineering.com/developing-reram-as-next-generation-on-chip-memory-for-machine-learning-image-processing-and-other-advanced-cpu-applications/

- : має

- :є

- : ні

- :де

- 1

- 10

- 100

- 10K

- 11

- 16

- 1M

- 2013

- 2014

- 2017

- 2021

- 2022

- 35%

- 3d

- 400

- 7

- 75

- 8

- 8k

- a

- здатність

- Здатний

- доступ

- через

- Діяти

- додати

- Додатковий

- просунутий

- впливати

- AI

- AL

- ВСІ

- Всі повідомлення

- полегшувати

- дозволяти

- по

- Також

- альтернатива

- an

- аналіз

- та

- додаток

- застосування

- прикладної

- приблизно

- архітектура

- ЕСТЬ

- області

- масив

- стаття

- AS

- At

- атомний

- Серпня

- b

- ширина смуги

- BE

- було

- почалася

- Краще

- між

- Біт

- Black

- дно

- коричневий

- Пакет

- але

- by

- званий

- CAN

- кар'єра

- викликаний

- CD

- осередок

- Клітини

- Центр

- зміна

- Канал

- характеристика

- стягується

- комбінати

- компанія

- Компанії

- порівняний

- комп'ютер

- Інформатика

- Занепокоєння

- диригент

- підтвердити

- з'єднує

- складається

- споживання

- Наші контакти

- містить

- Кореляція

- може

- центральний процесор

- створювати

- створений

- Перетинати

- Поточний

- В даний час

- Клієнти

- темно

- дані

- затримка

- затримки

- демонструвати

- продемонстрований

- Щільність

- депонований

- дизайн

- Дизайнери

- Визначати

- розвиненою

- розвивається

- розробка

- пристрій

- прилади

- різниця

- Відмінності

- різний

- розміри

- розрізнення

- displayed

- дисплеїв

- DOE

- виснажувати

- малювання

- управляти

- висушити

- під час

- E&T

- кожен

- легко

- край

- ефект

- вісім

- Electronic

- вбудований

- енергія

- Енергоспоживання

- інженер

- Машинобудування

- оцінити

- Ефір (ETH)

- досліджувати

- виконано

- експеримент

- Експерименти

- FET

- поле

- Рисунок

- заповнений

- Сфокусувати

- для

- Примусово

- форма

- сформований

- форми

- знайдений

- від

- функція

- майбутнє

- ворота

- Гейтс

- покоління

- графік

- великий

- зелений

- Мати

- he

- Високий

- вище

- Виділено

- його

- HTTPS

- хуан

- Сотні

- ID

- ідентифікує

- IEEE

- if

- зображення

- in

- включати

- Augmenter

- зростаючий

- вказувати

- індивідуальний

- вплив

- всередині

- інтегрувати

- інтегрований

- інтеграція

- в

- дослідити

- питання

- ЙОГО

- приєднався

- Тікати

- мова

- пізніше

- шар

- шарів

- макет

- провідний

- вивчення

- догляд

- Подветренний

- залишити

- як

- обмеженою

- лін

- логіка

- низький

- машина

- навчання за допомогою машини

- основний

- менеджер

- виробництво

- березня

- Маріо

- матеріал

- Матеріали

- макс-ширина

- Може..

- Зустрічатися

- пам'ять

- метал

- micron

- модель

- моделювання

- сучасний

- більше

- найбільш

- рухатися

- руху

- Необхідність

- необхідний

- наступний

- Листопад

- номер

- of

- ОМ

- on

- ONE

- тільки

- операція

- оптимізація

- or

- Інше

- вихід

- шлях

- стежки

- для

- продуктивність

- Philips

- Фізика

- стовп

- стовпи

- рожевий

- розміщений

- plato

- Інформація про дані Платона

- PlatoData

- точка

- Точка зору

- це можливо

- Пости

- потенціал

- влада

- раніше

- Проблема

- проблеми

- процес

- обробка

- програма

- запрограмований

- Програмування

- перспективний

- забезпечувати

- випадковий

- діапазон

- співвідношення

- Читати

- червоний

- Вилучено

- Звіти

- вимагати

- вимагається

- Вимога

- дослідження

- Опір

- відповідь

- результати

- огляд

- право

- Роль

- s

- наука

- науковий

- розділ

- напівпровідник

- Напівпровідникові прилади

- комплект

- налаштування

- Форма

- Повинен

- показаний

- сторона

- сигнали

- значний

- моделювання

- Розмір

- рішення

- ВИРІШИТИ

- Source

- відпрацьований

- укладені

- стан

- Штати

- заходи

- зберігання

- навчався

- Дослідження

- Вивчення

- такі

- Підтримуючий

- команда

- Технологія

- Розвиток технологій

- ніж

- Що

- Команда

- Графік

- Джерело

- Держава

- їх

- потім

- Там.

- Ці

- це

- через

- Таким чином

- час

- times

- синхронізація

- до

- топ

- до

- традиційно

- два

- тип

- типовий

- при

- розуміти

- на жаль

- блок

- використання

- використовуваний

- використання

- Цінності

- різний

- Проти

- вертикальний

- вертикально

- Відео

- вид

- Віртуальний

- візуалізації

- Напруга

- обсяг

- vs

- було

- we

- webp

- були

- коли

- в той час як

- білий

- широко

- волі

- з

- працював

- робочий

- б

- wu

- років

- зефірнет