З моменту свого дебюту в 1980-х роках зі спільними локальними мережами 10 Мбіт/с через коаксіальні кабелі Ethernet зазнав послідовних успіхів, тепер з потенціалом підтримки швидкості до 1.6 Тбіт/с. Цей розвиток дозволив Ethernet обслуговувати більш широкий спектр додатків, таких як прямі трансляції, мережі радіодоступу та промислове керування, підкреслюючи важливість надійної передачі пакетів і якості обслуговування. Оскільки поточна пропускна здатність Інтернету становить ~500 Тбіт/с, зростає попит на покращену обробку внутрішнього трафіку центру обробки даних. Хоча окремі сервери ще не працюють на рівнях терабіт за секунду, загальний трафік центру обробки даних наближається до цього масштабу, що спонукає групу IEEE 802.3dj до стандартизації та потребує надійних контролерів Ethernet і SerDes для керування потоком даних, що розширюється. На цьому тлі ескалації вимог міжпроцесорний зв’язок уже досягає таких швидкостей.

Міжпроцесорний зв’язок є ініціатором потреби в швидкості 1.6 Т з мінімальною затримкою. У той час як окремі пристрої обмежені властивою їм потужністю обробки та розміром мікросхеми, об’єднання мікросхем може значно розширити ці потужності. Очікується, що після першого покоління додатків з’являться з’єднання між комутаторами всередині центру обробки даних, що дозволить об’єднувати високопродуктивні процесори та пам’ять, підвищуючи масштабованість і ефективність хмарних обчислень.

Ініціатива IEEE 802.3dj: вдосконалення стандартів Ethernet для сумісності 1.6 Тбіт/с

Відповідність стандартизації, що розвивається, є ключовою для бездоганної взаємодії екосистем. Група IEEE 802.3dj знаходиться в процесі формулювання майбутнього стандарту Ethernet, який охоплює фізичні рівні та параметри керування для швидкостей від 200G до 1.6 терабіт на секунду. Метою групи є швидкість передачі даних Ethernet MAC 1.6 Тбіт/с, прагнучи до максимальної частоти бітових помилок не більше 10-13 на рівні MAC. Інші положення включають додаткові 16- та 8-канальні інтерфейси блоків підключення (AUI), придатні для різних додатків чіпів, що використовують 112G і 224G SerDes. Фізично специфікація 1.6 Тбіт/с передбачає передачу через 8 пар мідних кабелів твінакс довжиною до одного метра та 8 пар волокон на відстані від 500 метрів до 2 км. Хоча повна ратифікація стандарту очікується до весни 2026 року, основний набір функцій планується завершити у 2024 році.

Накладні витрати на смугу пропускання та виправлення помилок у підсистемах Ethernet 1.6T

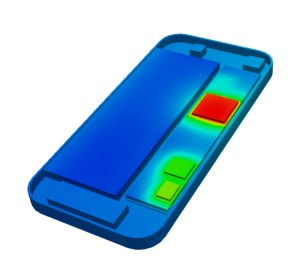

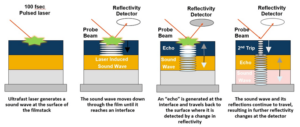

Рис. 1: Схема компонентів підсистеми Ethernet 1.6T.

У попередніх ітераціях Ethernet PCS головним чином зосереджувався на кодуванні даних для надійного виявлення пакетів. Однак із підвищенням швидкості Ethernet до 1.6 Т стає очевидною потреба у прямому виправленні помилок (FEC), особливо для протидії погіршенню сигналу навіть на коротких з’єднаннях. Для цього 1.6T Ethernet продовжує використовувати FEC Ріда-Соломона. Цей підхід створює кодове слово, що містить 514 10-бітних символів, закодованих у блок із 544 символів, що призводить до 6% накладних витрат на пропускну здатність. Ці кодові слова FEC розподіляються по фізичних каналах AUI, тому кожне фізичне посилання (8 для 1.6T Ethernet) не передає ціле кодове слово. Цей метод не тільки надає додатковий захист від спалахів помилок, але й уможливлює розпаралелювання на дальньому кінці декодера, тим самим зменшуючи затримку.

Physical Medium Attachment (PMA), що включає редуктор і SerDes, передає сигнал Ethernet на канали, що передаються. Для 1.6T Ethernet це передбачає 8 каналів, кожен із яких працює зі швидкістю 212 Гбіт/с, що становить 6% накладних витрат FEC. Застосовується техніка модуляції 4-рівневої амплітудної імпульсної модуляції (PAM-4), яка кодує два біти даних для кожного символу передачі, таким чином ефективно подвоюючи смугу пропускання в порівнянні з традиційним підходом без зворотного нуля (NRZ). Механізм передачі базується на цифро-аналоговому перетворенні, тоді як на приймальному кінці аналого-цифрове перетворення в поєднанні з DSP забезпечує точне виділення сигналу.

Крім того, важливо відзначити, що Ethernet PCS представляє «зовнішній FEC», який охоплює наскрізне з’єднання Ethernet. Щоб збільшити доступність каналів, розробляється додатковий рівень виправлення помилок для окремих фізичних ліній, імовірно, із застосуванням коду Хеммінга FEC. Очікується, що ця корекція знайде своє основне застосування в модулях оптичних приймачів, де така корекція є обов’язковою.

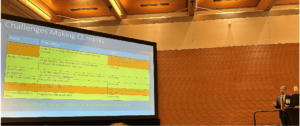

Рис. 2: Діаграма, що демонструє додаткові накладні витрати, додані при використанні конкатенованого FEC для розширеного охоплення.

У прикладі системи, зображеній на малюнку 2, MAC і PCS з’єднані через оптичний модуль і волоконну розтяжку. PCS має коефіцієнт бітових помилок 10-5 на каналі оптичного модуля, а також помилки самого оптичного каналу. Використання єдиного наскрізного RS-FEC буде недостатнім для досягнення 10-13 Стандарт Ethernet, що робить зв’язок ненадійним. Варіантом може бути потрійна реалізація окремого RS FEC на кожному стрибку, що значно збільшить витрати та затримку. Більш ефективним рішенням є інтеграція конкатенованого коду Хеммінга FEC спеціально для оптичного каналу зв’язку, що обслуговує типові випадкові помилки оптичних з’єднань. Цей внутрішній рівень FEC створює додаткове розширення лінійної швидкості з 212 Гбіт/с до 226 Гбіт/с, тому дуже важливо, щоб SerDes підтримував цю лінійну швидкість.

Проблеми затримки в системах Ethernet 1.6T

Рис. 3: Шлях затримки для підсистеми Ethernet 1.6T.

Різні компоненти впливають на затримку Ethernet: черга передачі, тривалість передачі, середній час проходження, а також кілька разів обробки та отримання. Щоб наочно це уявити, розглянемо малюнок 3, на якому зображено комплексну підсистему Ethernet 1.6T. Хоча на затримку може впливати час реакції віддаленої програми, цей фактор є зовнішнім щодо Ethernet і тому часто виключається під час аналізу затримки. Зведення до мінімуму затримки в інтерфейсі Ethernet вимагає розуміння конкретних обставин. Наприклад, затримка може не бути основною проблемою для магістральних з’єднань між комутаторами через властиві затримки на повільніших клієнтських з’єднаннях. Відстань також відіграє роль; більша довжина вводить більшу затримку. Звичайно, це не означає, що ми повинні ігнорувати затримку в інших сценаріях, скорочення затримки завжди є метою.

Затримка передавання безпосередньо пов’язана зі швидкістю Ethernet і розміром кадру. Зокрема, для системи Ethernet 1.6 Т для передачі пакету мінімального розміру потрібно 0.4 нс – по суті, один кадр Ethernet за такт тактової частоти 2.5 ГГц. З іншого боку, передача стандартного кадру максимального розміру займає 8 нс, а для Jumbo Frames — до 48 нс. Вибране середовище додатково визначає затримку. Наприклад, оптичне волокно зазвичай має затримку 5 нс на метр, тоді як мідний кабель трохи швидший – 4 нс на метр.

Значна частина загальної затримки пов’язана з контролером приймача. Декодер RS FEC за своєю суттю вводить затримку. Щоб ініціювати виправлення помилок, система повинна отримати 4 кодові слова, що при 1.6 Тбіт/с становить 12.8 нс. Подальші дії, включаючи виправлення помилок і буферизацію, збільшують цю затримку. Хоча тривалість зберігання кодового слова FEC залишається постійною, затримка під час отримання повідомлення залежить від конкретної реалізації. Тим не менш, затримку можна оптимізувати, використовуючи ретельні стратегії цифрового дизайну.

По суті, існує невід’ємна, неминуча затримка через механізм FEC і фізичну відстань або довжину кабелю. Окрім цих факторів, досвід проектування відіграє ключову роль у мінімізації затримки контролера Ethernet. Використання повного рішення, яке інтегрує та оптимізує MAC, PCS і PHY, прокладає шлях до найефективнішої реалізації з низькою затримкою.

Підсумки

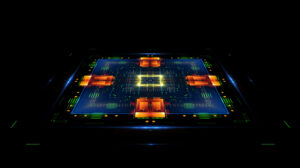

Рис. 4: Успіх кремнію першого проходу для Synopsys 224G Ethernet PHY IP за 3-нм процесом, що демонструє високолінійні очі PAM-4.

1.6 Тбіт/с Ethernet створено для програм, які потребують найбільшої пропускної здатності та чутливі до затримок. З появою технології 224G SerDes у поєднанні з досягненнями в MAC і PCS IP тепер доступні комплексні рішення, які постійно відповідають стандартам 1.6T Ethernet, що розвиваються. Крім того, через затримку, притаманну протоколу та методам виправлення помилок, цифровий і аналоговий дизайн IP повинні бути ретельно розроблені експертами-проектувальниками, щоб уникнути введення непотрібної затримки в тракт даних.

Досягнення найвищої продуктивності для дизайну SoC 1.6T вимагає ефективно оптимізованої архітектури та ретельного проектування для кожного компонента мікросхеми. Це підкреслює енергозбереження та мінімізує кремнієвий слід, завдяки чому швидкість передачі даних 1.6 Т стає реальністю. Перевірений Synopsys 224G Ethernet PHY IP заклав основу для контролера 1.6T MAC і PCS. Використовуючи передові технології проектування, аналізу, моделювання та вимірювання, Synopsys продовжує забезпечувати виняткову цілісність сигналу та продуктивність джиттера з повне рішення Ethernet, включаючи MAC+PCS+PHY.

- Розповсюдження контенту та PR на основі SEO. Отримайте посилення сьогодні.

- PlatoData.Network Vertical Generative Ai. Додайте собі сили. Доступ тут.

- PlatoAiStream. Web3 Intelligence. Розширення знань. Доступ тут.

- ПлатонЕСГ. вуглець, CleanTech, Енергія, Навколишнє середовище, Сонячна, Поводження з відходами. Доступ тут.

- PlatoHealth. Розвідка про біотехнології та клінічні випробування. Доступ тут.

- джерело: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- : має

- :є

- : ні

- :де

- $UP

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- доступ

- доступною

- бухгалтерський облік

- точний

- Achieve

- через

- діяльності

- доданий

- Додатковий

- Додатково

- Прийняття

- досягнення

- просування

- проти

- прицілювання

- дозволено

- вже

- Також

- хоча

- завжди

- посеред

- суми

- посилюватися

- an

- аналіз

- та

- Очікуваний

- додаток

- застосування

- підхід

- архітектура

- ЕСТЬ

- AS

- At

- уникнути

- Back-end

- задник

- ширина смуги

- BE

- стає

- між

- За

- Біт

- Блокувати

- підсилювач

- підвищення

- Приносить

- Будує

- але

- by

- кабель

- Кабелі

- CAN

- потужності

- нести

- проблеми

- канали

- чіп

- Чіпси

- вибраний

- обставин

- клієнт

- годинник

- хмара

- хмарних обчислень

- код

- комбінований

- об'єднання

- Комунікація

- повний

- завершення

- компонент

- Компоненти

- всеосяжний

- що включає

- обчислення

- Занепокоєння

- зв'язок

- підключений

- Зв'язки

- ЗБЕРЕЖЕННЯ

- Вважати

- міркування

- послідовний

- триває

- постійно

- сприяти

- контроль

- контролер

- Перетворення

- Мідь

- Core

- витрати

- протидіяти

- курс

- створений

- створює

- Поточний

- дані

- Дата-центр

- дебют

- затримки

- доставляти

- Попит

- вимогливий

- запити

- із зображенням

- дизайн

- Дизайнери

- конструкцій

- Виявлення

- прилади

- диктує

- різний

- цифровий

- старанно

- дисплеїв

- відстань

- розподілений

- Ні

- подвоєння

- два

- тривалість

- під час

- кожен

- Раніше

- екосистема

- Ефективний

- фактично

- ефективність

- ефективний

- продуктивно

- зусилля

- поява

- підкреслює

- підкреслюючи

- працевлаштований

- наймаючи

- дозволяє

- дозволяє

- охоплює

- кінець

- кінець в кінець

- гарантує

- Весь

- помилка

- помилки

- ескалація

- сутність

- істотний

- по суті

- Ефір (ETH)

- Навіть

- Кожен

- очевидний

- еволюціонує

- приклад

- винятковий

- виключений

- розширюється

- розширення

- очікуваний

- експерт

- експертиза

- продовжити

- розширення

- зовнішній

- видобуток

- очі

- фактор

- фактори

- далеко

- швидше

- риси

- Показуючи

- Рисунок

- знайти

- Перший

- Перше покоління

- потік

- увагу

- потім

- Слід

- для

- формулювання

- Вперед

- FRAME

- від

- далі

- покоління

- дає

- великий

- Group

- Групи

- Зростання

- рука

- Обробка

- Високий

- висока продуктивність

- дуже

- Однак

- HTML

- HTTPS

- імператив

- реалізація

- значення

- важливо

- поліпшений

- in

- В інших

- включати

- У тому числі

- зростаючий

- індивідуальний

- промислові

- під впливом

- притаманне

- за своєю суттю

- ініціювати

- Ініціатива

- екземпляр

- Інтеграція

- інтеграція

- цілісність

- інтерфейс

- Інтерфейси

- інтернет

- Взаємодія

- в

- сутнісний

- вводити

- Вводить

- введення

- включає в себе

- IP

- IT

- ітерації

- ЙОГО

- сам

- JPG

- Lane

- Затримка

- шар

- шарів

- довжина

- рівні

- використання

- Ймовірно

- Лінія

- ліній

- LINK

- зв'язку

- жити

- довше

- низький

- макінтош

- Робить

- управляти

- управління

- макс-ширина

- максимальний

- Може..

- значити

- вимір

- механізм

- середа

- пам'ять

- повідомлення

- метод

- методика

- педантичний

- мінімальний

- мінімізувати

- мінімізує

- мінімізація

- Модулі

- Модулі

- більше

- найбільш

- повинен

- наближається

- Необхідність

- мереж

- проте

- немає

- увагу

- зараз

- мета

- of

- часто

- on

- ONE

- тільки

- операційний

- оптимізований

- Оптимізує

- варіант

- or

- Інше

- над

- загальний

- пар

- параметри

- особливо

- шлях

- ПК

- для

- продуктивність

- виступи

- фізичний

- Фізично

- трубопровід

- основний

- plato

- Інформація про дані Платона

- PlatoData

- відіграє

- плюс

- потенціал

- влада

- практики

- в першу чергу

- первинний

- процес

- обробка

- процесори

- прогресія

- прогнозовані

- захист

- протокол

- пульс

- мета

- Натискання

- якість

- радіо

- випадковий

- діапазон

- ставка

- ставки

- досягати

- досягнення

- реакція

- Реальність

- отримати

- отримання

- прийом

- зниження

- надійний

- залишається

- надання

- Вимагається

- обмежений

- в результаті

- міцний

- Роль

- Коріння

- біг

- масштабованість

- шкала

- сценарії

- безшовні

- другий

- бачив

- сегмент

- чутливий

- окремий

- служити

- обслуговування

- комплект

- кілька

- загальні

- Короткий

- Повинен

- демонстрація

- Сигнал

- істотно

- Кремній

- моделювання

- Розмір

- So

- рішення

- Рішення

- прольоти

- очолює

- конкретний

- конкретно

- специфікація

- швидкість

- весна

- Стажування

- standard

- стандартизація

- стандартів

- зберігання

- стратегії

- потоковий

- наступні

- істотний

- успіх

- такі

- підходящий

- підтримка

- символ

- система

- з урахуванням

- приймає

- техніка

- методи

- Технологія

- ніж

- Що

- Команда

- їх

- Там.

- тим самим

- отже

- Ці

- це

- через

- Таким чином

- тик

- Зв'язаний

- час

- times

- до

- топ

- традиційний

- трафік

- переклад

- передавати

- Потрійний

- два

- типовий

- типово

- неминучий

- розуміння

- вживати

- блок

- Майбутні

- на

- використання

- використовувати

- через

- візуалізувати

- шлях..

- we

- коли

- який

- в той час як

- ширше

- з

- в

- б

- ще

- зефірнет

- нуль