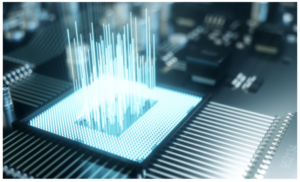

Chiplets tasarımın bir alanını basitleştirirken, pandora'nın kutusunu başka bir cephede açtı. Her birinin simülasyon karmaşıklığı yonga daha düşük ancak artık chiplet-chiplet ara bağlantısı karmaşık hale geldi. İnsanlar farklı ara bağlantı protokolleri, UCIe çeşitleri, UCIe ayarlarını değiştirme, arayüz hızları, fiziksel katman sayısı vb. ile deneyler yapıyor. Şimdi karışıma AXI gibi eski standartları, PICe6.0 gibi yeni protokolleri ve önbellek tutarlılığını ekleyin.

Sonuç olarak, bu tamamen yeni bir dizi deney yaratıyor. Geleneksel öykünmenin ve RTL modellemenin işe yaramayacağı bir durum. Öncelikle sadece bileşenlerin seçiminde değil, mimari denge üzerinde de çaba harcamanız gerekiyor. Bu, trafik analizi, uygulama bölümleme, sistem boyutlandırma ve farklı fiziksel katman türlerinin etkisini yürütmeniz gerektiği anlamına gelecektir. Ayrıca uygulamaya bağlı olarak kıyaslama çok farklı olacaktır.

UCIe spesifikasyonu yenidir ve net bir kriter yoktur. Ayrıca UCIe spesifikasyonu yalnızca gecikme ve güç konusunda rehberlik sağlar. Her ikisi de katı gereksinimlerdir. Bu, Güç-Performans Alanı çalışmasının kaçınılmaz olduğu anlamına gelir. PCIe 6.0'dan UCIe'ye ve AXI'ye gibi protokol-protokol-protokol dönüşümünüz olduğundan, modelleme kurulumu karmaşıktır.

Bir çözüm, sistem modellemeye bakmaktır. GörselSim itibaren mirabilis Tasarım. Yakın zamanda UCIe Sistem düzeyinde bir IP modeli başlattılar ve ara bağlantının bir dizi kullanım durumunu gösterecekler. Chiplet Zirvesi. Tasarımcılara yol göstermek amacıyla pek çok kullanım senaryosunu, beklenen güç performansı sonuçlarını ve optimizasyon seçeneklerini içeren bir kılavuz yayınladılar. Zirvede hem bildiri sunumu hem de stantları var. Seni orada görmeyi umuyorum!

Ayrıca, milletin alabileceği bir makalenin bağlantısı da burada: UCIe Ara Bağlantı Mimarisini temel alan heterojen bir bilgi işlem sisteminin performans modellemesi

Özet:

Günümüzün öncü düğümlerdeki karmaşık çip tasarımları genellikle birden fazla kalıptan (veya yongalardan) oluşur. Bu yaklaşım, farklı üreticilere veya işlemlere ait kalıpların yanı sıra yeniden kullanılabilir IP'ye de olanak tanır. Tasarımcıların bu tür karmaşık durumların farklı uygulamalarını değerlendirmek için sistem düzeyinde bir modele ihtiyacı vardır.

Örnek bir sistem, Universal Chiplet Interconnect Express (UCIe) standardı kullanılarak birbirine bağlanan bir G/Ç yongası, düşük güçlü çekirdek yongası, yüksek performanslı çekirdek yongası, ses-video yongası ve analog yongadan oluşur.

Ekibimiz, gelişmiş ve standart paketler, çeşitli trafik profilleri ve kaynakları ile erişimi genişletmek ve zaman aşımındaki olayları değerlendirmek için bir yeniden zamanlayıcı dahil olmak üzere çeşitli senaryoları ve yapılandırmaları değerlendirdi. Görev uygulamaları için UCIe ara bağlantısının güçlü ve zayıf yönlerini belirlemek, her alt sistem için performans, güç ve işlevsel gereksinimleri karşılayacak en uygun konfigürasyonu elde etmemize yardımcı oldu.

Mirabilis Tasarım A.Ş. Hakkında

Mirabilis Design, ürün spesifikasyonundaki riski tanımlamak ve ortadan kaldırmak, ürünü geliştirmek için gereken insan ve zaman kaynaklarını doğru bir şekilde tahmin etmek ve çeşitli mühendislikler arasındaki iletişimi geliştirmek için yazılım ve eğitim çözümleri sağlayan bir Silikon Vadisi yazılım şirketidir.

takım.

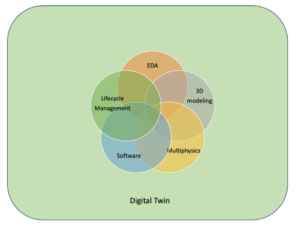

VisualSim Architect, model oluşturma, simülasyon, analiz ve RTL doğrulamasını önemli ölçüde geliştirmek için Fikri Mülkiyet, sistem düzeyinde modelleme, simülasyon, ortam analizi ve uygulama şablonlarını birleştirir. Ortam, tasarımcıların birbirine bağlı çeşitli zaman ve güç gereksinimlerini karşılayan bir tasarıma hızlı bir şekilde yaklaşmasını sağlar. Tasarım sürecinin çok erken aşamalarında, yazılı spesifikasyona paralel olarak (ve ona yardımcı olarak) ve ürünün uygulanmasından (örneğin, RTL, yazılım kodu veya şematik) önce kullanılır.

Ayrıca Oku:

WEBİNAR: Mimari Keşif Sırasında %95+ Doğru Güç Ölçümü Nasıl Elde Edilir?

SysML'yi Donanım Mimarisine Eşleme

Öğrencilere Yönelik Model Tabanlı Tasarım Kursları

Bu gönderiyi şu yolla paylaş:

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- PlatoData.Network Dikey Üretken Yapay Zeka. Kendine güç ver. Buradan Erişin.

- PlatoAiStream. Web3 Zekası. Bilgi Genişletildi. Buradan Erişin.

- PlatoESG. karbon, temiz teknoloji, Enerji, Çevre, Güneş, Atık Yönetimi. Buradan Erişin.

- PlatoSağlık. Biyoteknoloji ve Klinik Araştırmalar Zekası. Buradan Erişin.

- Kaynak: https://semiwiki.com/ip/mirabilis-design-ip/341339-chiplets-open-pandoras-box/

- :vardır

- :dır-dir

- :olumsuzluk

- a

- doğru

- tam olarak

- Başarmak

- eklemek

- ileri

- Yardım

- veriyor

- boyunca

- Ayrıca

- an

- analiz

- ve

- Başka

- Uygulama

- uygulamaları

- yaklaşım

- mimari

- ARE

- ALAN

- AS

- At

- merkezli

- BE

- müşterimiz

- önce

- kıyaslama

- kriterler

- arasında

- her ikisi de

- kutu

- fakat

- önbellek

- CAN

- Alabilirsin

- durumlarda

- yonga

- açık

- kod

- biçerdöverler

- Yakın İletişim

- şirket

- tamamen

- karmaşık

- karmaşıklık

- bileşenler

- bilgisayar

- Davranış

- yapılandırma

- kabul

- oluşur

- kas kütlesi inşasında ve

- yakınsamak

- Dönüştürme

- çekirdek

- dersler

- oluşturur

- tasviridir

- bağlı

- Dizayn

- dizayn süreci

- tasarımcıları

- tasarımlar

- geliştirmek

- farklı

- çeşitli

- sırasında

- her

- Erken

- çaba

- gidermek

- öykünme

- sağlar

- çevre

- değerlendirmek

- olaylar

- örnek

- beklenen

- deneme

- deneyler

- ekspres

- uzatmak

- Ad

- İçin

- itibaren

- ön

- fonksiyonel

- genellikle

- almak

- rehberlik

- rehberlik

- donanım

- Var

- yardım

- okuyun

- yüksek performans

- umut

- Ne kadar

- Nasıl Yapılır

- HTTPS

- insan

- i

- belirlemek

- belirlenmesi

- darbe

- uygulama

- uygulamaları

- iyileştirmek

- in

- Dahil olmak üzere

- entellektüel

- fikri mülkiyet

- birbirine bağlı

- arayüzey

- IP

- IT

- jpg

- sadece

- Gecikme

- başlattı

- tabaka

- katmanları

- miras

- seviye

- sevmek

- LINK

- Bakın

- bir sürü

- Düşük

- alt

- Üreticiler

- maksimum genişlik

- ortalama

- anlamına geliyor

- ölçüm

- Neden

- Toplandı

- Misyonumuz

- karıştırmak

- model

- Modelleme

- modelleme

- çoklu

- gerek

- yeni

- yok hayır

- düğümler

- şimdi

- numara

- elde etmek

- of

- on

- ONE

- bir tek

- açık

- açıldı

- optimum

- optimizasyon

- Opsiyonlar

- or

- paketler

- kâğıt

- Paralel

- performans

- fiziksel

- Platon

- Plato Veri Zekası

- PlatoVeri

- Çivi

- güç kelimesini seçerim

- tahmin

- sunum

- süreç

- Süreçler

- PLATFORM

- Profiller

- özellik

- protokolleri

- sağlar

- sağlama

- yayınlanan

- hızla

- ulaşmak

- Okumak

- geçenlerde

- gereklidir

- Yer Alan Kurallar

- Kaynaklar

- Sonuçlar

- yeniden kullanılabilir

- Risk

- senaryolar

- görmek

- seçme

- set

- ayarlar

- kurulum

- birkaç

- önemli ölçüde

- Silikon

- Silikon Vadisi

- basitleştirilmiş

- simülasyon

- durumlar

- So

- Yazılım

- çözüm

- Çözümler

- şartname

- hızları

- geçirmek

- standart

- standartlar

- güçlü

- sıkı

- Ders çalışma

- böyle

- Zirve

- sistem

- takım

- şablonları

- o

- The

- Orada.

- onlar

- Re-Tweet

- zaman

- için

- geleneksel

- trafik

- Eğitim

- türleri

- Evrensel

- us

- kullanım

- Kullanılmış

- kullanma

- Vadi

- varyasyonlar

- Doğrulama

- çok

- üzerinden

- zayıf

- İYİ

- hangi

- irade

- ile

- İş

- yazılı

- sen

- zefirnet