Banias Labs, yeni nesil iletişim için altyapı çözümleri geliştiren bir yarı iletken şirketidir. Hedef pazarı, ortaya çıkan yüksek performanslı bilgi işlem tasarımları için hiper ölçekli veri merkezi, ağ iletişimi, yapay zeka, optik modül ve Ethernet anahtarı SoC'lerini içeren yüksek performanslı bilgi işlem altyapısı pazarıdır. Bu SoC'ler, daha yüksek sistem performansı sağlamak ve pazara çıkış süresini hızlandırmak için yüksek hızlı Ethernet tasarımları ve düşük gecikme süreli çözümler gerektirir. Şirket, bu pazarın gereksinimlerini karşılamak için 5nm proses teknolojisine dayalı bir optik DSP SoC geliştirdi.

![]()

Optik DSP SoC, yüksek hızlı optik iletişim sistemlerinde kullanılmak üzere tasarlanmış özel bir çip üzerinde sistem (SoC) türüdür. Optik DSP SoC, DSP'ye ek olarak genellikle Ethernet PHY IP, PCIe IP ve DDR bellek denetleyicileri gibi yüksek hızlı arayüz IP bloklarını içerir. Bu tür SoC'ler, gerçek zamanlı sinyal işleme için düşük gecikmelerle yüksek hızlı veri aktarımına olanak tanır. Ayrıca güç tüketimini en aza indirecek şekilde tasarlanmışlardır; bu da onları, azaltılmış termal sorunlarla verimli çalışma gerektiren uygulamalar için ideal kılar. Avantajlarla birlikte zorluklar da geliyor. Optik iletişim sistemlerinin özel gereksinimleri, bir optik DSP SoC tasarlamayı normal bir SoC tasarlamaktan daha zor hale getirir.

Uygulama Zorlukları

Zorluklar tasarımın karmaşıklığı, sıkı güç ve performans gereksinimleri ve çeşitli endüstri standartlarını karşılama ihtiyacı etrafında dönüyor. DSP işlemcisi, Ethernet PHY IP ve diğer özel bloklar dahil olmak üzere birden fazla IP bloğunun entegrasyonu dikkatli bir tasarım ve doğrulama gerektirir. PCIe ve DDR gibi ek yüksek hızlı arayüzler tasarımın karmaşıklığını daha da artırır. Sistemdeki yüksek hızlı arayüzler ve çoklu IP blokları, sistem performansını ve güvenilirliğini etkileyebilecek sinyal bozulması, karışma ve elektromanyetik girişim oluşturabilir. Sistemin performans ve güvenilirlik gereksinimlerini karşılayabilmesini sağlamak için sinyal ve güç bütünlüğü analizi ve optimizasyonu tasarım döngüsünün başlarında gerçekleştirilmelidir. Son olarak, pazara çıkış süresi gereksinimlerini karşılamak zor olabilir. Yüksek performanslı bilgi işlem altyapısı pazarı hızla gelişiyor ve SoC geliştirme ekiplerinin rekabette öne geçebilmek için tasarımlarını hızlı bir şekilde sunması gerekiyor.

İlk Geçiş Silikon Başarısına Ulaşmak

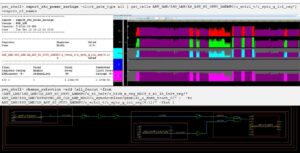

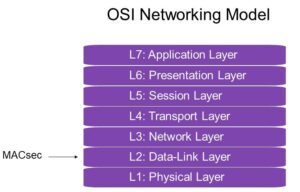

Yukarıda belirtilen zorlukların üstesinden gelmek kapsamlı bir yaklaşım gerektirir. Yüksek performanslı, düşük gecikme süreli çözümlerin kritik bileşenlerinden biri Ethernet PHY IP'dir. Ethernet PHY IP, SoC ile Ethernet ağı arasındaki fiziksel katman arayüzünden sorumludur. IP, 10G, 25G, 40G, 50G, 100G, 200G, 400G ve 800G dahil olmak üzere yüksek hızlı Ethernet arayüzlerini desteklemeli ve düşük gecikme ve düşük güç tüketimi sağlamalıdır. Ayrıca IP'nin, IEEE 802.3 ve Ethernet Alliance dahil olmak üzere çeşitli standartları desteklemesi gerekir. Bir diğer önemli bileşen ise EDA tasarım paketidir. EDA tasarım paketi, güç optimizasyonu, performans analizi, alan optimizasyonu ve verim analizi dahil olmak üzere SoC'nin tasarlanması ve doğrulanması için kapsamlı bir çözüm sağlamalıdır. EDA tasarım paketi, bir dereceye kadar yapay zeka (AI) ve makine öğrenimi (ML) gibi gelişmiş özellikleri içerir; bu, üretkenliği artırmak ve pazara sunma süresini kısaltmak için daha iyidir.

Synopsys İlk Geçiş Silikonunun Başarısını Hızlandırıyor

Synopsys, yüksek performanslı bilgi işlem altyapısı pazarı için SoC geliştirmenin benzersiz zorluklarını gideren çözümler sunar. Şirket, yönlendirme fizibilite çalışmasını, ambalajlama alt tabaka yönergelerini, sinyal ve güç bütünlüğü modellerini ve kapsamlı çapraz karışma analizini içeren kapsamlı bir IP çözümü sağlar. Bu, bir optik DSP SoC geliştirirken karşılaşılan sinyal ve güç bütünlüğü zorluklarını ele almak için zorunludur. Synopsys'in 112G Ethernet PHY IP'si, 5nm proses teknolojisinde düşük gecikme süresi, esnek erişim uzunlukları ve olgunluk sunarak onu hiper ölçekli veri merkezi, ağ iletişimi, yapay zeka, optik modül ve Ethernet anahtarı SoC'leri için ideal bir çözüm haline getiriyor. Ayrıca Synopsys, optimize edilmiş güç, performans, alan ve verim ile yüksek kaliteli sonuçlar sunan bir EDA Tasarım Paketi sunar. Synopsys'in yapay zeka destekli EDA Tasarım Paketi, sistem performansını artırmak ve pazara çıkış süresini hızlandırmak için çözümler sunarak, onu yüksek performanslı bilgi işlem altyapısı pazarı için başarılı bir çözümün önemli bir bileşeni haline getiriyor.

Özet

Synopsys, gelişmiş Ethernet anahtarı ve ağ SoC'lerinin gelişimini hızlandıran yüksek performanslı, düşük gecikme süreli çözümler sunar. Synopsys'in kapsamlı IP çözümleri, kapsamlı EDA Tasarım Paketi ve Yapay Zekayla Geliştirilmiş EDA Paketi hakkında daha fazla bilgi edinmek için aşağıdaki sayfaları ziyaret edin.

Synopsys'in kapsamlı IP çözümleri

Synopsys'in kapsamlı EDA Paketi

Synopsys'in yapay zeka odaklı EDA Tasarım Paketi

Ayrıca Oku:

Multi-Die Systems: Yıllardır Bilişimde En Büyük Bozulma

Hızlı, Mimari Odaklı, PPA Optimizasyonu ile Kendi RISC-V İşlemcinizi Geliştirme Riskinden Kurtulmak

Artan Bant Genişliği Açlığını Yüksek Hızlı Ethernet ile Beslemek

Bu gönderiyi şu yolla paylaş:

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- Plato blok zinciri. Web3 Metaverse Zekası. Bilgi Güçlendirildi. Buradan Erişin.

- Adryenn Ashley ile Geleceği Basmak. Buradan Erişin.

- Kaynak: https://semiwiki.com/ip/327703-synopsys-accelerates-first-pass-silicon-success-for-banias-labs-networking-soc/

- :vardır

- :dır-dir

- a

- Hakkımızda

- yukarıdaki

- hızlandırmak

- hızlandırır

- ilave

- Ek

- Ayrıca

- adres

- ileri

- avantajları

- önde

- AI

- Ittifak

- Ayrıca

- an

- analiz

- ve

- Başka

- uygulamaları

- yaklaşım

- ARE

- ALAN

- etrafında

- yapay

- yapay zeka

- Yapay zeka (AI)

- AS

- At

- Bant genişliği

- BE

- Daha iyi

- arasında

- Biggest

- Blokları

- artırmak

- CAN

- dikkatli

- Merkez

- zorluklar

- zor

- nasıl

- Yakın İletişim

- İletişim

- şirket

- rekabet

- karmaşıklık

- bileşen

- bileşenler

- kapsamlı

- bilgisayar

- tüketim

- yaratmak

- kritik

- görenek

- devir

- veri

- Veri Merkezi

- teslim etmek

- sağlıyor

- Dizayn

- tasarlanmış

- tasarım

- tasarımlar

- gelişmiş

- gelişen

- gelişme

- geliştirir

- Bozulma

- Erken

- verimli

- ortaya çıkan

- etkinleştirmek

- gelişmiş

- sağlamak

- gerekli

- gelişen

- yüzlü

- HIZLI

- Özellikler

- Nihayet

- Ad

- esnek

- takip etme

- İçin

- itibaren

- daha fazla

- Büyüyen

- kuralları yenileyerek

- yüksek performans

- Yüksek kaliteli

- HTML

- HTTPS

- açlık

- ideal

- IEEE

- görüntü

- darbe

- zorunlu

- önemli

- in

- içerir

- Dahil olmak üzere

- artmış

- sanayi

- Endüstri standartları

- Altyapı

- bütünleşme

- bütünlük

- İstihbarat

- arayüzey

- arayüzler

- IP

- sorunlar

- IT

- ONUN

- Labs

- Gecikme

- tabaka

- ÖĞRENİN

- öğrenme

- Düşük

- makine

- makine öğrenme

- yapmak

- Yapımı

- pazar

- olgunluk

- maksimum genişlik

- Neden

- toplantı

- Bellek

- adı geçen

- ML

- modelleri

- modül

- Daha

- çoklu

- gerek

- ağ

- ağ

- gelecek nesil

- of

- Teklifler

- on

- ONE

- operasyon

- optimizasyon

- optimize

- Diğer

- kendi

- ambalaj

- geçmek

- performans

- fiziksel

- Platon

- Plato Veri Zekası

- PlatoVeri

- Çivi

- güç kelimesini seçerim

- süreç

- işleme

- İşlemci

- verimlilik

- sağlamak

- sağlar

- hızla

- hızla

- ulaşmak

- Okumak

- gerçek zaman

- Indirimli

- düzenli

- güvenilirlik

- gerektirir

- Yer Alan Kurallar

- gerektirir

- sorumlu

- Sonuçlar

- Risk

- yarıiletken

- işaret

- Silikon

- çözüm

- Çözümler

- özel

- standartlar

- kalmak

- Ders çalışma

- başarı

- başarılı

- böyle

- süit

- destek

- anahtar

- sistem

- Sistemler

- Hedef

- takım

- Teknoloji

- göre

- o

- The

- ve bazı Asya

- Onları

- termal

- Bunlar

- onlar

- Re-Tweet

- için

- çok

- transferler

- türleri

- tipik

- benzersiz

- kullanım

- onaylama

- çeşitli

- doğrulama

- üzerinden

- Türkiye Dental Sosyal Medya Hesaplarından bizi takip edebilirsiniz.

- hangi

- ile

- Yol ver

- zefirnet