2010'lu yıllarda Moore yasasının yararları azalmaya başladı. Moore yasası, transistör yoğunluğunun her iki yılda bir ikiye katlandığını ve hesaplama maliyetinin buna karşılık gelen %50 oranında azalacağını belirtiyordu. Moore yasasındaki değişiklik, transistör yapısının düzlemsel cihazlardan Finfet'lere doğru evrimi sırasında tasarım karmaşıklığının artmasından kaynaklanmaktadır. Finfet'lerin, cihaz boyutlarını 20 nm'nin altındaki düğümlere ulaştırmak için litografi için çoklu desenlere ihtiyacı vardır.

Bu on yılın başında, çoğunlukla veri merkezlerinin çoğalması ve üretilen ve işlenen veri miktarı nedeniyle bilgi işlem ihtiyaçlarında patlama yaşandı. Aslında Yapay Zekanın (AI) benimsenmesi ve Makine Öğrenimi (ML) gibi teknikler artık sürekli artan verileri işlemek için kullanılıyor ve sunucuların bilgi işlem kapasitelerini önemli ölçüde artırmasına yol açtı.

Sunucular çok daha fazla CPU çekirdeği ekledi, yalnızca makine öğrenimi için kullanılan, artık grafikler için kullanılmayan daha büyük GPU'ları entegre etti ve yerleşik özel ASIC AI hızlandırıcılara veya tamamlayıcı, FPGA tabanlı AI işlemeye sahip. İlk AI çip tasarımları, daha büyük monolitik SoC'ler kullanılarak uygulandı; bunlardan bazıları, retikülün dayattığı boyut sınırına (yaklaşık 700 mm) ulaştı.2.

Bu noktada, daha küçük bir SoC'ye ve çeşitli hesaplama ve IO yongalarına ayrıştırmak doğru çözüm gibi görünüyor. Intel, AMD veya Xilinx gibi birçok yonga üreticisi, üretime girecek ürünler için bu seçeneği seçmiştir. The Linley Group'un "Chiplet'ler Hızlı Benimseme Kazanıyor: Neden Büyük Cipsler Küçük Oluyor" başlıklı mükemmel teknik incelemesinde, bu seçeneğin, daha büyük olanın verim etkisi nedeniyle monolitik SoC'lere kıyasla daha iyi maliyetlere yol açtığı gösterildi.

Bu eğilimin IP satıcıları üzerindeki en büyük etkisi çoğunlukla SoC'leri ve yongaları birbirine bağlamak için kullanılan ara bağlantı işlevleri üzerindedir. Bu noktada (3'in 2021. Çeyreği), endüstrinin birçoğu için resmileştirilmiş standartlar oluşturmaya çalıştığı çeşitli protokoller kullanılıyor.

Mevcut önde gelen D2D standartları şunları içerir: i) Başlangıçta Intel tarafından tanımlanan ve şimdi telifsiz kullanım sunan Gelişmiş Arayüz Veri Yolu (AIB, AIB2), ii) DRAM kalıplarının silikon bir aracının üzerinde üst üste istiflendiği Yüksek Bant Genişlikli Bellek (HBM). ve TSV'ler kullanılarak bağlanır, iii) Bir endüstri grubu olan Açık Etki Alanına Özel Mimari (ODSA) alt grubu, Bunch of Wires (BoW) ve OpenHBI olmak üzere iki arayüz daha tanımlamıştır.

Heterojen çiplet tasarımı, sistemin geri kalanını değiştirmeden korurken yalnızca ilgili çipletleri değiştirerek veya ekleyerek farklı uygulamaları veya pazar segmentlerini hedeflememize olanak tanır. Yeniden tasarım yalnızca yongaları barındıran paket alt katmanını etkileyeceğinden, önemli ölçüde daha düşük yatırımla yeni gelişmeler pazara daha hızlı sunulabilir.

Örneğin, bilgi işlem yongası, sistemin geri kalanını değiştirmeden korurken, daha büyük L5 önbellek veya daha yüksek performanslı CPU çekirdeklerini entegre etmek için TSMC 3nm'den TSMC 1nm'ye yeniden tasarlanabilir. Spektrumun diğer ucunda, daha iyi pazar konumlandırması için daha fazla IO bant genişliği sunan yeni süreç düğümlerinde daha hızlı oranlar için yalnızca SerDes'i entegre eden yonga seti yeniden tasarlanabilir.

Intel PVC, aynı chip üreticisinin çeşitli chiplet bileşenlerine (bellek aygıtları hariç) sahip olduğu dikey entegrasyon diyebileceğimiz heterojen entegrasyonun (çeşitli fonksiyonel chiplet, CPU, anahtar vb.) mükemmel bir örneğidir.

HPC, veri merkezi, yapay zeka veya ağ oluşturma gibi üst düzey uygulamalar için SoC'ler geliştiren çip üreticilerinin chiplet mimarilerini ilk benimseyenler olması muhtemeldir. Daha büyük L3 önbellek için SRAM'ler veya AI hızlandırıcılar gibi belirli işlevler, Ethernet, PCIe veya CXL standartları, chiplet tasarımları için ilk arayüz adayı olmalıdır.

Bu ilk benimseyenler, birden fazla farklı iş modelinden yararlanan heterojen çipletlerin geçerliliğini ve tabii ki test ve paketleme için üretim fizibilitesini gösterdiğinde, bu yeni teknolojiyi desteklemek için kritik öneme sahip bir ekosistem yaratılmış olacak. Bu noktada, yalnızca yüksek performanslı uygulamalar için değil, daha geniş bir pazarda benimsenmesini bekleyebiliriz.

Bir çip üreticisi, bilgi işlem ve IO işlevselliğini hedefleyen çeşitli çiplerden oluşan bir sistemi piyasaya sürerse, heterojen ürünlerin daha da ileri gidebileceğini hayal edebiliriz. Bu yaklaşım, şirket içi D2D protokolüne sahip çipletler sunan bir IP satıcısının sektör için çekici olmaması nedeniyle D2D protokolünde yakınsamayı zorunlu hale getiriyor.

Buna bir benzetme, yarı iletken şirketlerinin farklı kaynaklardan gelen çeşitli tasarım IP'lerini entegre etmeye geçiş yaptığı 2000'li yıllardaki SoC binasıdır. 2000'li yılların IP satıcıları kaçınılmaz olarak 2020'lerin chiplet satıcıları haline gelecektir. Gelişmiş SerDe'ler veya PCIe, Ethernet veya CXL gibi karmaşık protokoller gibi belirli işlevler için, IP satıcıları bunu silikon üzerinde uygulayacak en iyi teknik bilgiye sahiptir.

Karmaşık Tasarım IP'si için, simülasyon doğrulaması müşterilere gönderilmeden önce çalıştırılmış olsa bile, satıcıların performansı garanti etmek için IP'yi silikon üzerinde doğrulaması gerekir. Dijital IP için işlev FPGA'de uygulanabilir çünkü test çipi yapmaktan daha hızlı ve çok daha ucuzdur. SerDes tabanlı PHY gibi karışık sinyal IP'si için satıcılar, müşteriye göndermeden önce silikondaki IP'yi karakterize etmelerine olanak tanıyan Test Çipi (TC) seçeneğini seçerler.

Bir chiplet basit bir TC olmasa da, sahada kullanılmadan önce kapsamlı bir şekilde test edilip onaylanacağından, satıcı tarafından bir üretim chiplet'i geliştirmek için yapılması gereken artımlı çalışma miktarı çok daha azdır. Başka bir deyişle, IP satıcısı, kendi IP'sinden oluşturulmuş bir yongayı hızlı bir şekilde piyasaya sürmek, mümkün olan en iyi TTM'yi sunmak ve riski en aza indirmek için en iyi konumdadır.

Heterojen entegrasyona yönelik iş modeli, ilgili IP satıcısı tarafından yapılan çeşitli yongaların (örneğin, ARM tabanlı CPU yongaları için ARM, Risc-V tabanlı bilgi işlem yongaları için Si-Five ve yüksek hızlı SerDes yongaları için Alphawave) lehinedir. Tasarım IP'sinin sahibidirler.

Bunların hiçbiri çip üreticilerinin kendi çipletlerini tasarlamalarını ve benzersiz mimarilerini korumak veya ev yapımı ara bağlantıları uygulamak için karmaşık tasarım IP'lerini kaynaklamalarını engellemez. 2000'li yıllardaki SoC Design IP'ye benzer şekilde, çipletler için satın alma veya verme kararı, temel yetkinlik koruması ve farklılaşmayan işlevlerin kaynaklanması arasında ağırlıklandırılacaktır.

2000'li yıllardan bu yana tarihi ve modern Tasarım Fikri Mülkiyet işindeki büyümenin sürekli olarak dış kaynak kullanımının benimsenmesiyle sürdürüldüğünü gördük. Her iki model de bir arada var olacak (chiplet şirket içinde veya bir IP satıcısı tarafından tasarlandı) ancak tarih, satın alma kararının eninde sonunda ön plana çıktığını gösterdi.

Artık endüstride, Moore yasasını gerçekleştirmeye çılgınca odaklanmanın ileri teknoloji düğümleri için artık geçerli olmadığı konusunda fikir birliği var. 7nm ve altı. Her yeni teknoloji noktasında mmXNUMX başına daha fazla transistörün eklenmesiyle çip entegrasyonu hâlâ devam ediyor. Ancak transistör başına maliyet de her yeni düğümde artıyor.

Chiplet teknolojisi, diğer işlevler için eski düğümleri kullanırken ana SoC için daha fazla entegrasyonu teşvik eden önemli bir girişimdir. Bu hibrit strateji, diğer Tasarım IP'lerinin doğrudan ana SoC'ye entegrasyonuyla ilişkili hem maliyeti hem de tasarım riskini azaltır.

IPnest, bu eğilimin arayüz IP işinde iki ana etkisi olacağına inanıyor; biri yakın zamanda (2-2021) D2025D IP gelirlerinin güçlü bir şekilde büyümesi olacak, diğeri ise üst düzey silikon pazarını artırmak için heterojen chiplet pazarının yaratılması olacak. IP pazarı.

Bu pazarın PCIe, CXL veya Ethernet gibi karmaşık protokol işlevlerinden oluşması bekleniyor. G/Ç SoC'lerine (USB, HDMI, DP, MIPI, vb.) entegre arayüz IP'si sunan IP satıcıları bunun yerine G/Ç yongaları sunmaya karar verebilir.

Bu devrimden etkilenen diğer IP kategorileri, L3 önbellek için SRAM bellek derleyici IP satıcıları olacaktır. Doğası gereği önbellek boyutunun işlemciye bağlı olarak değişmesi beklenir. Bununla birlikte, L3 önbellek yongasının tasarlanması, IP satıcısının yeni bir ürün türü sunarak Tasarım IP gelirlerini artırmasının bir yolu olabilir.

Ayrıca, NVM IP'si artık gelişmiş süreç düğümleri üzerinde tasarlanan SoC'lere entegre edilmediğinden NVM IP kategorisi de olumlu etkilenebilir. Bu, NVM IP satıcılarının çipletler sunarak yeni işler yaratmasının bir yolu olacaktır.

FPGA ve AI hızlandırıcı çipletlerin ASSP çip üreticileri için yeni bir gelir kaynağı olacağını düşünüyoruz, ancak bunların tam anlamıyla IP satıcıları olarak sıralanabileceklerini düşünmüyoruz.

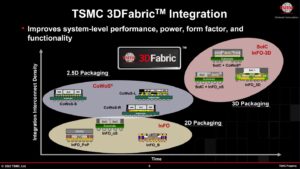

Arayüz IP satıcıları bu silikon devriminde önemli aktörler olacaksa, TSMC ve Samsung gibi en gelişmiş düğümlere hitap eden silikon dökümhaneleri de önemli bir rol oynayacak. Dökümhanelerin chiplet tasarlayacağını düşünmüyoruz, ancak IP satıcılarını destekleme kararı alabilirler ve onları, bugün üst düzey SerDes'lerini pazarlamak için gelişmiş IP satıcılarını desteklerken yaptıkları gibi, 3 nm'de SoC'lerle kullanılacak chipletler tasarlamaya zorlayabilirler. 7nm ve 5nm'de sabit IP olarak.

Intel'in yakın zamanda 3'e geçişird parti dökümhanelerinin aynı zamanda üçüncü parti IP'lerden ve yarı iletken ağır sikletlerin heterojen chiplet benimsemesinden de yararlanması bekleniyor. Bu durumda hiç şüphe yok ki Microsoft, Amazon ve Google gibi Hyperscalar'lar da chiplet mimarilerini benimseyecekler… tabii chiplet'in benimsenmesinde Intel'in önüne geçmezlerse.

By Eric Esteve (Doktora) Analist, Sahip IPnest

Bu gönderiyi şu yolla paylaş: Kaynak: https://semiwiki.com/semiconductor-services/ipnest/303790-chiplet-are-you-ready-for-next-semiconductor-revolution/

- 2021

- hızlandırıcı

- hızlandırıcılar

- Benimseme

- İleri Teknoloji

- AI

- Izin

- Amazon

- AMD

- analist

- uygulamaları

- mimari

- ARM

- yapay zeka

- Yapay zeka (AI)

- Te

- İYİ

- inşa etmek

- bina

- Demet

- otobüs

- iş

- iş modeli

- satın almak

- çağrı

- Kapasite

- değişiklik

- yonga

- cips

- gelecek

- Şirketler

- hesaplamak

- bilgisayar

- Fikir birliği

- maliyetler

- Müşteriler

- veri

- teslim

- Dizayn

- geliştirmek

- Cihaz

- dijital

- Erken

- erken evlat edinmek

- ekosistem

- vb

- evrim

- Ad

- odak

- fpga

- Ücretsiz

- işlev

- GPU'lar

- grup

- Büyüyen

- Büyüme

- Yüksek

- tarih

- ev

- HTTPS

- melez

- darbe

- Artırmak

- sanayi

- Girişim

- bütünleşme

- Intel

- İstihbarat

- yatırım

- IP

- IT

- koruma

- anahtar

- başlatmak

- Kanun

- önemli

- öğrenme

- Led

- Kaldıraç

- LINK

- makine öğrenme

- büyük

- yapıcı

- Yapımı

- üretim

- pazar

- Microsoft

- ML

- model

- ağ

- yeni ürün

- düğümler

- teklif

- teklif

- açık

- seçenek

- Diğer

- sahip

- ambalaj

- kâğıt

- performans

- PLATFORM

- üretim

- Ürünler

- korumak

- koruma

- oranlar

- yeniden tasarlamak

- DİNLENME

- Risk

- koşmak

- Samsung

- yarıiletken

- Kargo

- simülasyon

- beden

- standartlar

- Stratejileri

- destek

- anahtar

- sistem

- Hedef

- teknikleri

- Teknoloji

- test

- üst

- us

- usb

- satıcıları

- Doğrulama

- Beyaz kağıt

- sözler

- İş

- yıl

- Yol ver