Synopsys, SolvNet sitesinde Intel Graphics'ten Dr. Theo Drane tarafından yapılan büyüleyici bir konuşmayı yayınladı. Konu, veri yolu denklik denetimidir. Başka bir Synopsys VC Resmi DPV onayı gibi gelebilir ama yine de izlemelisiniz. Bu, resmi kullanımlar ve dikkate alınması gerekenler hakkında zihin açıcı bir tartışmadır ve sizi rutin kullanım kılavuzu türünün ötesine geçerek daha büyüleyici alanlara götürür.

Örnek teste karşı entelektüel anlama

Tüm biçimleriyle test odaklı simülasyon mükemmeldir ve genellikle bir tasarım spesifikasyonunun veya uygulamasının doğruluğunu doğrulamada yeri doldurulamaz. Başlamak da kolaydır. Sadece bir test programı yazın ve simülasyona başlayın. Ancak bu basitliğin diğer tarafı, buna ihtiyacımız olmamasıdır. tamamen Başlamak için neyi test ettiğimizi anlayın. Spesifikasyonları dikkatlice okuduğumuza ve tüm köşe durumlarını anladığımıza kendimizi ikna ediyoruz, ancak anlayışımızı alt etmek için çok fazla bileşik karmaşıklık gerekmiyor.

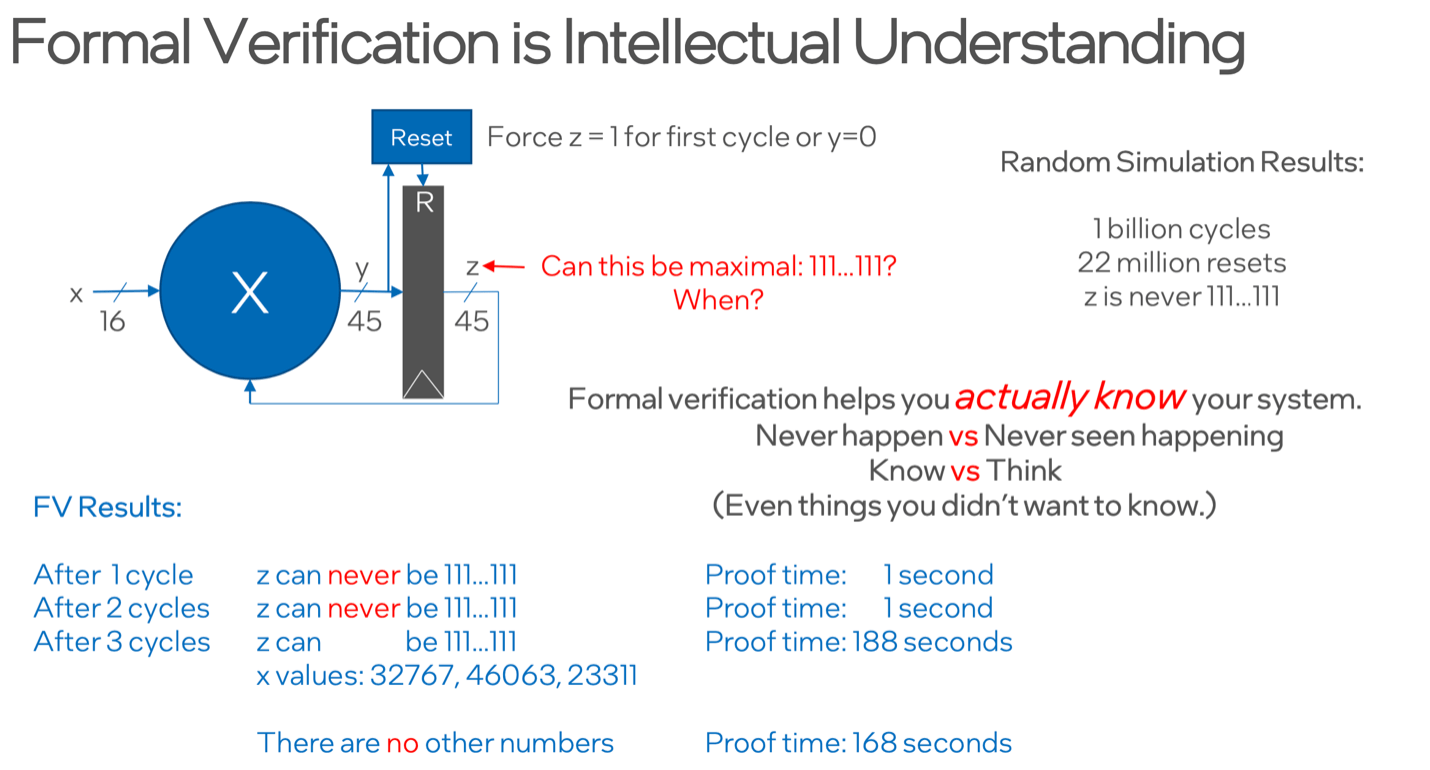

Formal, işlevselliği derinlemesine anlamanız için sizi teşvik eder (en azından değerli bir sonuç elde etmek istiyorsanız). Yukarıdaki örnekte, basit bir soru – z hiç 1'in tamamı olabilir mi – bir simülatörde bir milyar döngüde bir örnek gösteremez. Şaşırtıcı değil, çünkü bu aşırı bir köşe davası. Resmi bir test, 188 saniyede spesifik ve çok açık olmayan bir örnek sağlar ve bunun böyle tek durum olduğunu biraz daha kısa sürede kanıtlayabilir.

Tamam resmi, dinamik testin yapamadığı şeyi yaptı, ancak daha da önemlisi, simülatörün size asla söylememiş olabileceği bir şey öğrendiniz. Bu koşulun meydana gelebileceği tek bir olası durum olduğunu. Biçimsel, tasarımı yalnızca sınırlı sayıda test senaryosunda olasılıksal bir özet olarak değil, entelektüel düzeyde daha iyi anlamanıza yardımcı oldu.

Spesifikasyon sorunları

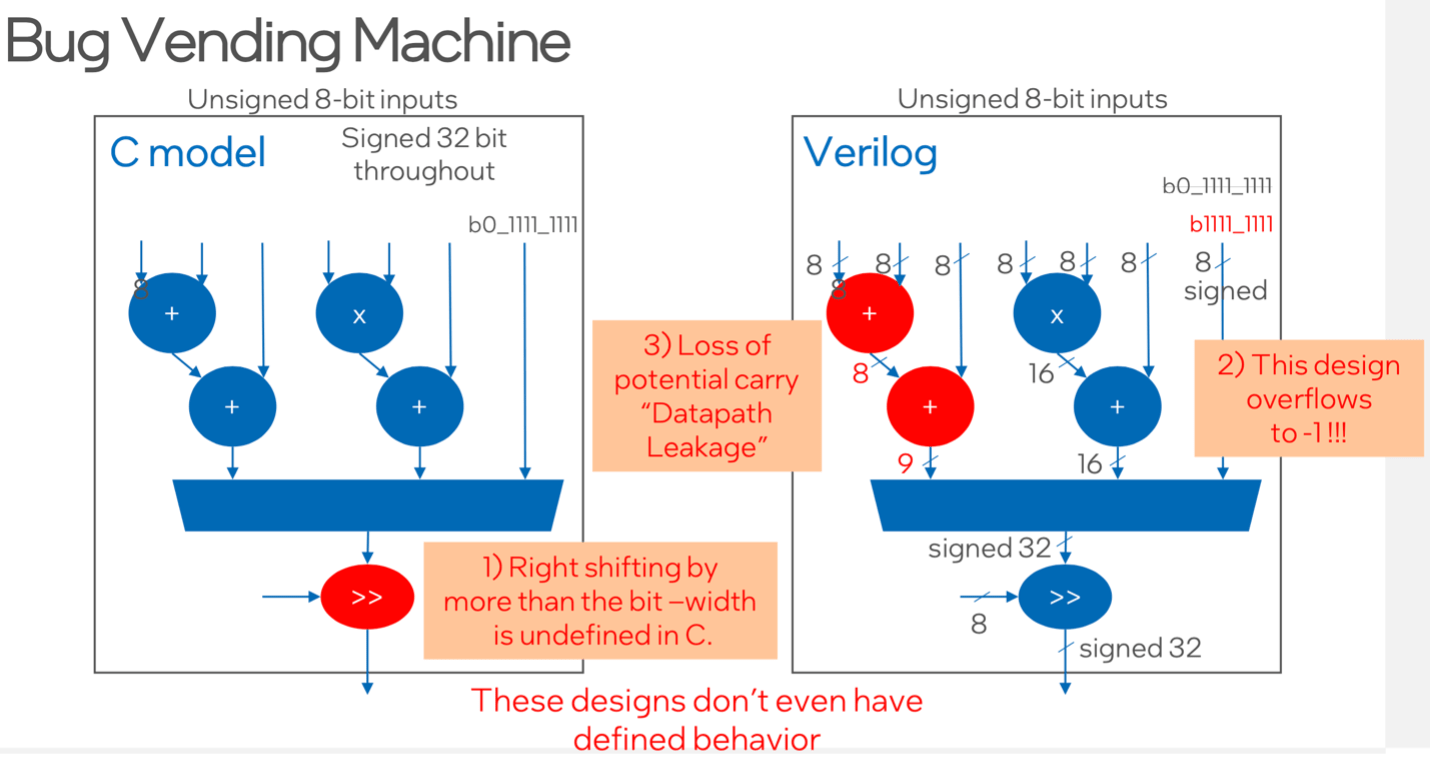

Theo'nun bir sonraki örneği, bir böcek otomatı üzerine kuruludur (bir düğmeye bastığınızda bir hata aldığınız için böyle adlandırılır). Bu oldukça basit bir C'den RTL'ye denklik kontrol problemi gibi görünüyor, solda C modeli, sağda RTL modeli. Resmi olarak ilk günlerinde Theo için bir sürpriz, gcc makul davranacak olsa da, C-modelindeki sağa kaydırma davranışının C standardında tam olarak tanımlanmamış olmasıydı. Ancak DPV, olması gerektiği gibi, RTL ile karşılaştırmada bir uyumsuzluktan şikayet edecektir. Tanımlanmamış davranış, güvenmek için tehlikeli bir şeydir.

C ve RTL arasındaki özellik karşılaştırması, özellikle bit genişlikleri çevresinde başka tehlikelerle birlikte gelir. Bir ara sinyaldeki (yukarıdaki 3 numaralı) taşıma bitinin kesilmesi veya kaybı iyi örneklerdir. Bunlar spesifikasyon sorunları mı? Spesifikasyon ve uygulama seçenekleri arasında gri bir alan olabilir.

denklik kontrolünün ötesinde

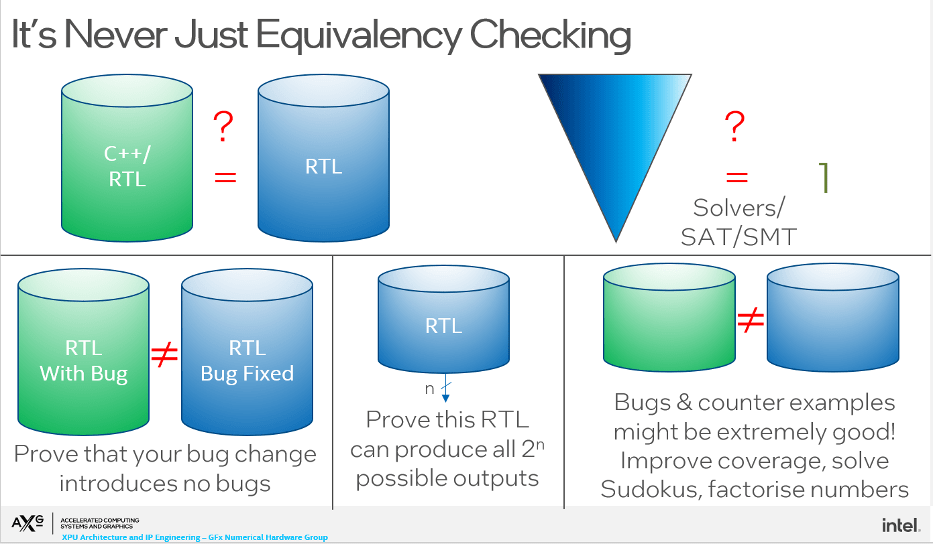

Görünüşe göre DPV'nin birincil amacı, bir C veya RTL referansı ile bir RTL uygulaması arasındaki eşdeğerliği kontrol etmektir. Ancak bu ihtiyaç nispeten nadirdir ve bu tür bir teknolojinin, kutudan biraz çıkmışsa uygulanabileceği başka yararlı yollar da vardır. İlk olarak uygulama dünyasında bir klasik - Bir değişiklik yaptım, bir hatayı düzelttim - sonuç olarak herhangi bir yeni hata getirdim mi? Saat geçişi ekledikten sonra SEQ kontrolü gibi biraz. Blok çıktılarında erişilebilirlik analizi, bazı durumlarda başka bir yararlı uygulama olabilir.

Theo daha da yaratıcı hale geliyor ve kursiyerlerden tasarımı daha iyi anlamak için karşı örnekleri kullanmalarını istiyor. Sudoku çözmek or tamsayıları çarpanlara ayırma. DPV'nin bu tür sorunlara yaklaşmanın tuhaf bir yolu olduğunu kabul ediyor, ancak amacının DPV'nin yalnızca denklik kontrolü için olduğu yanılsamasını kırmak olduğuna dikkat çekiyor. İlginç bir fikir ve kesinlikle bu tür zorluklar üzerinde düşünmek için beyin jimnastiği. (İtiraf etmeliyim ki Sudoku probleminden bahsettiği anda hemen düşünmeye başladım.)

Sarmak

Theo, üretim kullanımında önemli olan metodolojiler, kısıtlamalar, gerilemeler ve eski RTL modelleriyle karşılaştırmalar hakkında bir tartışma ile sonlandırıyor. Ayrıca, kontrol ettiğiniz şeyin gerçekten üst düzey doğal dil belirtimiyle eşleşip eşleşmediğini bilmenin zorlukları da vardır.

Çok enerji verici bir konuşma izlemeye değer burada SolvNet'te!

Bu gönderiyi şu yolla paylaş:

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- Plato blok zinciri. Web3 Metaverse Zekası. Bilgi Güçlendirildi. Buradan Erişin.

- Kaynak: https://semiwiki.com/eda/325878-intel-keynote-on-formal-a-mind-stretcher/

- :dır-dir

- a

- Hakkımızda

- yukarıdaki

- karşısında

- aslında

- Sonra

- Türkiye

- analiz

- ve

- Başka

- Uygulama

- uygulamalı

- yaklaşım

- ARE

- ALAN

- etrafında

- AS

- At

- merkezli

- BE

- Çünkü

- Daha iyi

- arasında

- Ötesinde

- Milyar

- Bit

- Engellemek

- kutu

- mola

- Böcek

- böcek

- düğmesine tıklayın

- by

- denilen

- CAN

- dikkatlice

- taşımak

- dava

- durumlarda

- kesinlikle

- zorluklar

- değişiklik

- Kontrol

- denetleme

- choices

- klasik

- saat

- karşılaştırma

- tamamen

- karmaşıklık

- koşul

- hususlar

- kısıtlamaları

- ikna etmek

- Köşe

- olabilir

- sayaç

- Yaratıcı

- döngüleri

- Tehlikeli

- Günler

- derin

- tanımlı

- teslim etmek

- göstermek

- Dizayn

- DID

- tartışma

- Değil

- Dont

- dinamik

- Erken

- teşvik

- özellikle

- Hatta

- hİÇ

- örnek

- örnekler

- mükemmel

- aşırı

- başarısız

- büyüleyici

- Ad

- sabit

- Fiske

- İçin

- resmi

- formlar

- işlevsellik

- GCC

- almak

- verilmiş

- Tercih Etmenizin

- grafik

- gri

- gri alan

- olmak

- Var

- yardım

- Ancak

- HTTPS

- i

- Fikir

- hemen

- uygulama

- önemli

- in

- Intel

- entellektüel

- niyet

- ilginç

- Orta seviye

- tanıtmak

- sorunlar

- IT

- ONUN

- Konuşmacı

- Nezaket.

- bilme

- dil

- öğrendim

- miras

- seviye

- sevmek

- küçük

- GÖRÜNÜYOR

- kayıp

- makine

- yapılmış

- yapmak

- maksimum genişlik

- adı geçen

- metodolojiler

- olabilir

- model

- modelleri

- Daha

- Doğal (Madenden)

- Doğal lisan

- gerek

- yeni

- sonraki

- of

- on

- ONE

- Diğer

- Zift

- Platon

- Plato Veri Zekası

- PlatoVeri

- noktaları

- mümkün

- Çivi

- posted

- basın

- güzel

- birincil

- Sorun

- sorunlar

- üretim

- Programı

- Kanıtlamak

- sağlar

- amaç

- soru

- Okumak

- Nispeten

- sonuç

- saniye

- set

- meli

- işaret

- Basit

- basitlik

- simülasyon

- simülatör

- beri

- yer

- So

- biraz

- bir şey

- Yakında

- Ses

- özel

- şartname

- standart

- başlama

- başladı

- basit

- böyle

- ÖZET

- sürpriz

- şaşırtıcı

- Bizi daha iyi tanımak için

- Konuşmak

- Teknoloji

- test

- Test yapmak

- o

- The

- Bunlar

- şey

- Düşünme

- İçinden

- zaman

- için

- Üst düzey

- konu

- kesme

- anlamak

- anlayış

- kullanım

- kullanım

- Değerli

- VC

- doğrulama

- Karşı

- üzerinden

- İzle

- izlerken

- Yol..

- yolları

- İYİ

- Ne

- olup olmadığını

- hangi

- irade

- ile

- Dünya

- değer

- olur

- yazmak

- zefirnet