Evrensel Doğrulama Metodolojisi (UVM), SystemVerilog tasarımlarını doğrulamaya yardımcı olan popüler bir yoldur ve şunları içerir: konfigürasyon sistemi maalesef bazı hız ve kullanım sorunları var. Siemens EDA'dan Rich Edelman, bu sorunların nasıl önlenebileceği konusunda 20 sayfalık ayrıntılı bir makale yazdı. Ben de sizin için önemli noktaları özetlemek amacıyla bu makaleyi inceledim. Doğrulama mühendisleri, değerleri ayarlamak ve daha sonra UVM testlerinde değerleri almak için bir UVM konfigürasyon veritabanını kullanır. 'T' değerini ayarlamanın ve almanın bir örneği:

uvm_config#(T)::set(kapsam, örnek_yol_adı, alan_adı, değer); uvm_config#(T)::get(kapsam, örnek_yol_adı, alan_adı, değer);

UVM test ortamının test altındaki cihaza bağlanması, sanal arayüzleri geçirmek için konfigürasyon veritabanını kullanır. UVM yapılandırmasını kullanmanın üç sorunu vardır:

- Büyük kod, yaklaşık 2,600 satırlık kod

- Tam tür eşleşmesi gerektirdiğinden 'int' ve 'bit' aynı değildir

- Yavaş kod

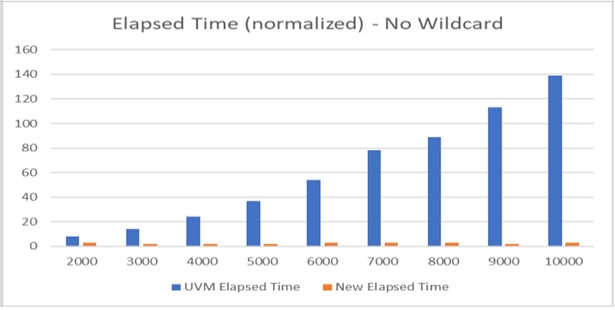

Yavaş kod durumunu düşünün, çünkü set()'e yapılan binlerce çağrıda joker karakterlerin kullanıldığı adların 'set' ve 'get' aşamasını tamamlaması 30 dakikaya kadar sürebilir.

Rich, UVM konfigürasyonlarına kıyasla çok daha yüksek hızlara sahip, yalnızca birkaç saniye süren yeni bir çözüm öneriyor.

UVM kodunuz joker karakter kullanmaktan kaçınıyorsa ve az sayıda 'set' komutu içeriyorsa, kodunuz daha hızlı çalışacaktır.

UVM yapılandırma sorunlarına olası çözümler şunlardır:

- Bunun yerine global bir değişken kullanın

- Bir set() ile UVM yapılandırmasını kullanın

- Birkaç set() ile UVM yapılandırmasını kullanın

- Yapılandırma ağacı kullanma

- Farklı bir şeyler dene

Farklı bir şey denemeye yönelik bu son yaklaşım, yeni çözümdür ve set() ve get() API'sini kullanmaya devam eder, ardından konfigürasyonların parametrelendirmesini kaldırarak basitleştirir, önceliği kaldırır ve arama algoritması değişikliğini ortadan kaldırır. Bu yeni yaklaşımın sonuçları yüksek hızlardır.

Yeni konfigürasyon öğeniz, 'config_item'den türetilmiş sınıfta tanımlanır ve aşağıdaki örnek, ayarlanmakta olan özellik olarak 'int value'yu gösterir. Hata ayıklama amacıyla güzel yazdırma işlevini eklersiniz.

my_special_config_item sınıfı config_item'i genişletir; function new(string name = "my_special_config_item"); süper.yeni(isim); son işlev int değeri; sanal işlev dizesi Convert2string(); return $sformatf("%s - value=%0d <%s>", get_name(), value, super.convert2string()); son işlev son sınıfı

'config_item'in bir ad özelliği vardır ve bu ad artı örnek adı aranır. Yapılandırma nesnesi ayrıca adı döndürmek için bir get_name() işlevine sahiptir. Herhangi bir "örnek_adı.alan_adı" bulmak için yapılandırma veritabanı, hızlı arama ve oluşturma hızları sağlayan ilişkisel bir dizi kullanır.

İzlenebilirlik açısından get'i kimin ayarladığını veya kimin çağırdığını öğrenebilirsiniz, çünkü dosya adı ve satır numarası set() ve get() işlev çağrılarındaki alanlardır.

set(null, "top.ab*", "SPEED", my_speed_config, `__FILE__, `__LINE__) get(null, "top.abcdmonitor1", "SPEED", speedconfig, `__FILE__, `__LINE__)

Erişimci kuyruğu, set() ve get()'ı kimin çağırdığını görmek için hata ayıklama sırasında yazdırılabilir.

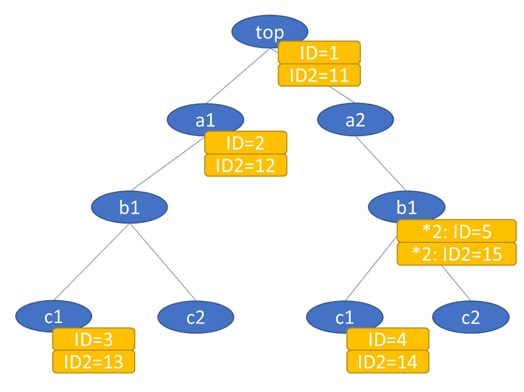

Joker karakterleri desteklemek için kapları kullanan bir arama mekanizması eklenmesi gerekiyordu. 'Top.abcd*_0' örnek adını düşünün.

Örnek adının joker karakter kısmı, ilişkisel dizi yerine kap ağacı kullanılarak işlenir.

Özet

Bir UVM test ortamında modül/örnek ile sınıf tabanlı dünya arasında veri paylaşımı, UVM yapılandırma veritabanı kullanılarak yapılabilir; yalnızca hız yavaşlamalarına dikkat edin. Metodolojiniz çok sayıda konfigürasyon kullanıyorsa, UVM konfigürasyon veritabanı dosyasındaki 300 satırlık kod yerine yaklaşık 2,600 satırlık kod kullanan bir pakete sahip olan yeni yaklaşımı kullanmayı düşünün.

20 sayfalık makalenin tamamını okuyun, Yapılandırma Çılgınlığını Önlemenin Kolay Yolu Siemens EDA'da.

İlgili Bloglar

Bu gönderiyi şu yolla paylaş:

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- PlatoData.Network Dikey Üretken Yapay Zeka. Kendine güç ver. Buradan Erişin.

- PlatoAiStream. Web3 Zekası. Bilgi Genişletildi. Buradan Erişin.

- PlatoESG. karbon, temiz teknoloji, Enerji, Çevre, Güneş, Atık Yönetimi. Buradan Erişin.

- PlatoSağlık. Biyoteknoloji ve Klinik Araştırmalar Zekası. Buradan Erişin.

- Kaynak: https://semiwiki.com/eda/339885-making-uvm-faster-through-a-new-configuration-system/

- :vardır

- :dır-dir

- :olumsuzluk

- $UP

- 30

- 300

- 600

- a

- Hakkımızda

- eklemek

- ekleme

- algoritma

- Ayrıca

- an

- ve

- herhangi

- api

- yaklaşım

- ARE

- Dizi

- AS

- At

- önlemek

- farkında

- b

- BE

- Çünkü

- olmak

- altında

- arasında

- by

- denilen

- aramalar

- CAN

- dava

- değişiklik

- sınıf

- kod

- karşılaştırma

- tamamlamak

- yapılandırma

- Düşünmek

- Konteyner

- Konteynerler

- devam ediyor

- oluşturma

- veri

- veritabanı

- tanımlı

- Türetilmiş

- tasarımlar

- detaylı

- cihaz

- farklı

- yapılmış

- sırasında

- kolay

- Mühendisler

- Eter (ETH)

- örnek

- uzanır

- HIZLI

- Daha hızlı

- az

- Alanlar

- fileto

- bulmak

- İçin

- itibaren

- tam

- işlev

- almak

- alma

- Küresel

- gitmiş

- yardım et

- özeti

- Ne kadar

- Nasıl Yapılır

- HTTPS

- if

- in

- içerir

- örnek

- yerine

- arayüzler

- tanıttı

- sorunlar

- IT

- jpg

- sadece

- Soyad

- sonra

- çizgi

- hatları

- baktı

- arama

- bir sürü

- Yapımı

- uygun

- maksimum genişlik

- mekanizma

- metodoloji

- dk

- dakika

- çok

- isim

- isimleri

- yeni

- yeni çözüm

- numara

- nesne

- of

- on

- ONE

- bir tek

- or

- dışarı

- paket

- kâğıt

- Bölüm

- geçmek

- faz

- Platon

- Plato Veri Zekası

- PlatoVeri

- artı

- Popüler

- Çivi

- öncelik

- sorunlar

- özellik

- önermektedir

- amaçlı

- kaldırır

- kaldırma

- gereklidir

- Sonuçlar

- dönüş

- Zengin

- koşmak

- kapsam

- saniye

- görmek

- set

- ayar

- Gösteriler

- iletkenlik birimi

- basitleştirir

- yavaş

- yavaşlamalar

- So

- çözüm

- Çözümler

- biraz

- bir şey

- hız

- hızları

- dizi

- özetlemek

- harika

- destek

- sistem

- T

- Bizi daha iyi tanımak için

- alma

- test

- o

- The

- ve bazı Asya

- sonra

- Orada.

- Bunlar

- Re-Tweet

- Binlerce

- üç

- İçinden

- zaman

- için

- üst

- konu

- İzlenebilirlik

- ağaç

- çalışıyor

- tip

- altında

- ne yazık ki

- Evrensel

- kullanım

- kullanım

- kullanım

- kullanma

- değer

- Değerler

- değişken

- Doğrulama

- doğrulamak

- üzerinden

- Sanal

- Yol..

- hangi

- DSÖ

- irade

- ile

- Dünya

- yazdı

- sen

- zefirnet