นับตั้งแต่เปิดตัวในช่วงปี 1980 ด้วย LAN ที่ใช้ร่วมกันความเร็ว 10Mbps ผ่านสายโคแอกเซียล อีเธอร์เน็ตได้เห็นความก้าวหน้าอย่างต่อเนื่อง ซึ่งขณะนี้มีศักยภาพที่จะรองรับความเร็วสูงสุด 1.6Tbps ความก้าวหน้านี้ทำให้อีเธอร์เน็ตสามารถให้บริการแอพพลิเคชั่นที่หลากหลายมากขึ้น เช่น การสตรีมสด เครือข่ายการเข้าถึงวิทยุ และการควบคุมทางอุตสาหกรรม โดยเน้นย้ำถึงความสำคัญของการถ่ายโอนแพ็กเก็ตที่เชื่อถือได้และคุณภาพของการบริการ เนื่องจากแบนด์วิธอินเทอร์เน็ตในปัจจุบันสูงถึง ~500 Tbps จึงมีความต้องการเพิ่มขึ้นสำหรับการจัดการการรับส่งข้อมูลภายในศูนย์ข้อมูลแบ็คเอนด์ที่ได้รับการปรับปรุง แม้ว่าแต่ละเซิร์ฟเวอร์จะยังไม่ได้ทำงานที่ระดับเทราบิตต่อวินาที แต่ปริมาณการใช้งานศูนย์ข้อมูลโดยรวมก็เข้าใกล้ระดับนี้ ส่งผลให้กลุ่ม 802.3dj ของ IEEE ดำเนินการสร้างมาตรฐานและจำเป็นต้องมีตัวควบคุมอีเทอร์เน็ตที่แข็งแกร่งและ SerDes เพื่อจัดการกระแสข้อมูลที่ขยายตัว ท่ามกลางความต้องการที่เพิ่มมากขึ้น การสื่อสารระหว่างโปรเซสเซอร์ได้เพิ่มความเร็วดังกล่าวแล้ว

การสื่อสารระหว่างโปรเซสเซอร์เป็นหัวหอกในความต้องการอัตรา 1.6T โดยมีเวลาแฝงน้อยที่สุด แม้ว่าอุปกรณ์แต่ละชิ้นจะถูกจำกัดด้วยความสามารถในการประมวลผลและขนาดชิปที่มีอยู่เดิม แต่การรวมชิปจะช่วยเพิ่มขีดความสามารถเหล่านี้ได้อย่างมาก คาดว่าแอปพลิเคชันรุ่นแรกจะตามมาด้วยการเชื่อมต่อแบบสวิตช์ต่อสวิตช์ภายในศูนย์ข้อมูล ช่วยให้สามารถรวมโปรเซสเซอร์และหน่วยความจำประสิทธิภาพสูง เพิ่มความสามารถในการขยายขนาดและประสิทธิภาพภายในการประมวลผลแบบคลาวด์

ความคิดริเริ่ม 802.3dj ของ IEEE: พัฒนามาตรฐานอีเธอร์เน็ตสำหรับการทำงานร่วมกัน 1.6 Tbps

การปฏิบัติตามความพยายามในการมาตรฐานที่เปลี่ยนแปลงไปเป็นสิ่งสำคัญสำหรับการทำงานร่วมกันของระบบนิเวศที่ราบรื่น กลุ่ม 802.3dj ของ IEEE อยู่ในขั้นตอนการกำหนดมาตรฐานอีเทอร์เน็ตที่กำลังจะมาถึง ซึ่งประกอบด้วยเลเยอร์ทางกายภาพและพารามิเตอร์การจัดการสำหรับความเร็วตั้งแต่ 200G ถึง 1.6 เทราบิตต่อวินาที วัตถุประสงค์ของกลุ่มคืออัตราข้อมูล Ethernet MAC 1.6 Tbps โดยมีเป้าหมายเพื่อให้อัตราข้อผิดพลาดบิตสูงสุดไม่เกิน 10-13 ที่เลเยอร์ MAC ข้อกำหนดเพิ่มเติมรวมถึงอินเทอร์เฟซหน่วยแนบ (AUI) 16 และ 8 เลนที่เหมาะสำหรับการใช้งานชิปที่แตกต่างกัน โดยใช้ประโยชน์จาก SerDes 112G และ 224G ตามทางกายภาพ ข้อกำหนด 1.6Tbps เกี่ยวข้องกับการส่งผ่านสาย copper twinax 8 คู่ สูงสุด 8 เมตร และไฟเบอร์ 500 คู่สำหรับระยะทางระหว่าง 2 เมตร ถึง 2026 กม. แม้ว่าจะมีการให้สัตยาบันโดยสมบูรณ์ของมาตรฐานภายในฤดูใบไม้ผลิปี 2024 แต่ชุดคุณลักษณะหลักก็คาดว่าจะแล้วเสร็จในปี XNUMX

โอเวอร์เฮดแบนด์วิธและการแก้ไขข้อผิดพลาดในระบบย่อยอีเทอร์เน็ต 1.6T

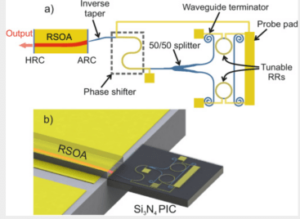

รูปที่ 1: แผนภาพแสดงส่วนประกอบของระบบย่อยอีเธอร์เน็ต 1.6T

ในการทำซ้ำอีเธอร์เน็ตก่อนหน้านี้ PCS มุ่งเน้นไปที่การเข้ารหัสข้อมูลเป็นหลักเพื่อการตรวจจับแพ็กเก็ตที่เชื่อถือได้ อย่างไรก็ตาม ด้วยความเร็วอีเทอร์เน็ตที่เพิ่มขึ้นเป็น 1.6T ความจำเป็นในการแก้ไขข้อผิดพลาดข้างหน้า (FEC) จึงปรากฏชัดขึ้น โดยเฉพาะอย่างยิ่งเพื่อรับมือกับการลดทอนสัญญาณบนแม้แต่ลิงก์สั้น ๆ เพื่อจุดประสงค์นี้ 1.6T Ethernet ยังคงใช้ Reed-Solomon FEC ต่อไป วิธีการนี้จะสร้างคำรหัสที่ประกอบด้วยสัญลักษณ์ 514 บิต 10 ตัวที่เข้ารหัสลงในบล็อกสัญลักษณ์ 544 ส่งผลให้โอเวอร์เฮดแบนด์วิธ 6% โค้ดเวิร์ด FEC เหล่านี้กระจายไปทั่วลิงก์ทางกายภาพของ AUI เพื่อให้แต่ละลิงก์ทางกายภาพ (8 สำหรับอีเธอร์เน็ต 1.6T) ไม่ได้มีโค้ดเวิร์ดทั้งหมด วิธีการนี้ไม่เพียงแต่ให้การป้องกันเพิ่มเติมต่อการระเบิดข้อผิดพลาดเท่านั้น แต่ยังช่วยให้สามารถใช้งานแบบขนานที่ตัวถอดรหัสระยะไกลได้ ซึ่งช่วยลดเวลาแฝงอีกด้วย

Physical Medium Attachment (PMA) ซึ่งมีกระปุกเกียร์และ SerDes จะนำสัญญาณอีเทอร์เน็ตไปยังช่องสัญญาณที่ส่ง สำหรับอีเธอร์เน็ต 1.6T สิ่งนี้เกี่ยวข้องกับ 8 แชนเนลแต่ละแชนเนลทำงานที่ 212Gbps ซึ่งคิดเป็นค่าใช้จ่าย 6% FEC เทคนิคการมอดูเลชั่นที่ใช้คือ 4-Level Pulse Amplitude Modulation (PAM-4) ซึ่งเข้ารหัสบิตข้อมูลสองบิตสำหรับแต่ละสัญลักษณ์การส่งสัญญาณ จึงเพิ่มแบนด์วิดท์ได้อย่างมีประสิทธิภาพเป็นสองเท่าเมื่อวางคู่กับแนวทาง Non-Return Zero (NRZ) แบบดั้งเดิม กลไกการส่งสัญญาณอาศัยการแปลงดิจิตอลเป็นอนาล็อก ในขณะที่ฝั่งรับ การแปลงอนาล็อกเป็นดิจิตอลรวมกับ DSP ช่วยให้มั่นใจได้ว่าการแยกสัญญาณมีความแม่นยำ

นอกจากนี้ สิ่งสำคัญที่ควรทราบคือ Ethernet PCS แนะนำ "FEC ภายนอก" ที่ครอบคลุมตั้งแต่ต้นทางถึงปลายทางบนลิงก์ Ethernet เพื่อสนับสนุนช่องทางการเข้าถึงที่ยาวขึ้น จึงมีชั้นการแก้ไขข้อผิดพลาดเพิ่มเติมสำหรับสายทางกายภาพแต่ละเส้นอยู่ในไปป์ไลน์ ซึ่งมีแนวโน้มว่าจะใช้รหัส hamming FEC การแก้ไขนี้คาดว่าจะพบการใช้งานหลักในโมดูลตัวรับส่งสัญญาณแสงซึ่งการแก้ไขดังกล่าวมีความจำเป็น

รูปที่ 2: แผนภาพแสดงค่าใช้จ่ายเพิ่มเติมที่เพิ่มเข้ามาเมื่อใช้ FEC ที่ต่อกันเพื่อการขยายการเข้าถึง

ในระบบตัวอย่างที่แสดงในรูปที่ 2 MAC และ PCS เชื่อมต่อผ่านโมดูลออปติคัลและการยืดไฟเบอร์ PCS มีอัตราข้อผิดพลาดบิตอยู่ที่ 10-5 ที่ลิงก์โมดูลออปติคัล รวมถึงข้อผิดพลาดจากลิงก์ออปติคัลเอง การใช้ RS-FEC แบบ end-to-end เพียงอย่างเดียวนั้นไม่เพียงพอที่จะบรรลุ 10-13 มาตรฐานอีเทอร์เน็ต ทำให้ลิงก์ไม่น่าเชื่อถือ ตัวเลือกหนึ่งคือการใช้งาน RS FEC แยกกันสามครั้งในทุก ๆ การกระโดด ซึ่งจะเพิ่มต้นทุนและเวลาแฝงอย่างมาก วิธีแก้ปัญหาที่มีประสิทธิภาพมากกว่าคือการบูรณาการ Hamming Code FEC ที่ต่อกันโดยเฉพาะสำหรับการเชื่อมต่อแบบออปติคัล เพื่อรองรับข้อผิดพลาดแบบสุ่มทั่วไปของการเชื่อมต่อแบบออปติก เลเยอร์ FEC ภายในนี้สร้างการขยายอัตราสายเพิ่มเติมจาก 212 Gbps เป็น 226 Gbps ดังนั้นจึงจำเป็นอย่างยิ่งที่ SerDes จะสามารถรองรับอัตราสายนี้ได้

ความท้าทายด้านความหน่วงในระบบอีเธอร์เน็ต 1.6T

รูปที่ 3: เส้นทางแฝงสำหรับระบบย่อยอีเธอร์เน็ต 1.6T

ส่วนประกอบต่างๆ มีส่วนทำให้เกิดเวลาแฝงของอีเธอร์เน็ต: คิวการส่งข้อมูล ระยะเวลาการส่งข้อมูล เวลาการเคลื่อนที่ปานกลาง และเวลาประมวลผลและการรับหลายครั้ง หากต้องการเห็นภาพนี้ ให้พิจารณารูปที่ 3 ซึ่งแสดงระบบย่อยอีเทอร์เน็ต 1.6T ที่ครอบคลุม แม้ว่าเวลาแฝงอาจได้รับอิทธิพลจากเวลาตอบสนองของแอปพลิเคชันระยะไกล แต่ปัจจัยนี้อยู่ภายนอกอีเธอร์เน็ต และมักจะถูกแยกออกในระหว่างการวิเคราะห์เวลาแฝง การลดเวลาแฝงที่อินเทอร์เฟซอีเทอร์เน็ตต้องอาศัยความเข้าใจในสถานการณ์เฉพาะ ตัวอย่างเช่น เวลาแฝงอาจไม่เป็นปัญหาหลักสำหรับการเชื่อมต่อหลักระหว่างสวิตช์ เนื่องจากความล่าช้าโดยธรรมชาติในลิงก์ไคลเอนต์ที่ช้ากว่า ระยะทางก็มีบทบาทเช่นกัน ความยาวที่มากขึ้นทำให้เกิดเวลาแฝงมากขึ้น แน่นอนว่า นี่ไม่ได้หมายความว่าเราควรมองข้ามเวลาแฝงในสถานการณ์อื่นๆ การลดเวลาแฝงนั้นเป็นเป้าหมายเสมอ

เวลาแฝงในการส่งข้อมูลจะเชื่อมโยงกับอัตราอีเธอร์เน็ตและขนาดเฟรมโดยธรรมชาติ โดยเฉพาะสำหรับระบบอีเทอร์เน็ต 1.6T การส่งแพ็กเก็ตขนาดต่ำสุดจำเป็นต้องใช้ 0.4ns โดยพื้นฐานแล้วคือหนึ่งเฟรมอีเทอร์เน็ตต่อสัญญาณนาฬิกา 2.5 GHz ในทางกลับกัน การส่งเฟรมขนาดสูงสุดมาตรฐานจะใช้เวลา 8ns และขยายเป็น 48ns สำหรับ Jumbo Frames สื่อที่เลือกจะกำหนดเวลาในการตอบสนองเพิ่มเติม ตัวอย่างเช่น โดยทั่วไปแล้ว ใยแก้วนำแสงจะมีค่าความหน่วงอยู่ที่ 5ns ต่อเมตร ในขณะที่สายเคเบิลทองแดงจะเร็วกว่าเล็กน้อยที่ 4ns ต่อเมตร

ส่วนสำคัญของเวลาแฝงโดยรวมนั้นฝังอยู่ในตัวควบคุมตัวรับ ตัวถอดรหัส RS FEC มักแนะนำเวลาแฝง เพื่อเริ่มต้นการแก้ไขข้อผิดพลาด ระบบจะต้องได้รับโค้ดเวิร์ด 4 คำ ซึ่งที่ 1.6Tbps มีค่าเท่ากับ 12.8ns กิจกรรมที่ตามมา รวมถึงการแก้ไขข้อผิดพลาดและการบัฟเฟอร์ จะขยายเวลาแฝงนี้ แม้ว่าระยะเวลาการจัดเก็บโค้ดเวิร์ดของ FEC จะคงที่ แต่เวลาแฝงระหว่างการรับข้อความจะขึ้นอยู่กับการใช้งานเฉพาะ อย่างไรก็ตาม สามารถปรับเวลาแฝงให้เหมาะสมได้โดยใช้กลยุทธ์การออกแบบดิจิทัลที่พิถีพิถัน

โดยพื้นฐานแล้ว มีความหน่วงโดยธรรมชาติและหลีกเลี่ยงไม่ได้เนื่องจากกลไก FEC และระยะห่างทางกายภาพหรือความยาวของสายเคเบิล นอกเหนือจากปัจจัยเหล่านี้แล้ว ความเชี่ยวชาญด้านการออกแบบยังมีบทบาทสำคัญในการลดเวลาแฝงของตัวควบคุมอีเธอร์เน็ต การใช้ประโยชน์จากโซลูชันที่สมบูรณ์ซึ่งผสานรวมและเพิ่มประสิทธิภาพ MAC, PCS และ PHY ปูทางไปสู่การใช้งานที่มีประสิทธิภาพสูงสุดและมีความหน่วงต่ำ

สรุป

รูปที่ 4: ความสำเร็จของซิลิคอนในการผ่านครั้งแรกสำหรับ Synopsys 224G Ethernet PHY IP ในกระบวนการ 3 นาโนเมตร ซึ่งจัดแสดงดวงตา PAM-4 เชิงเส้นสูง

อีเธอร์เน็ต 1.6 Tbps ได้รับการปรับแต่งสำหรับแอปพลิเคชันที่ต้องการแบนด์วิดธ์และมีความหน่วงแฝงมากที่สุด ด้วยการเกิดขึ้นของเทคโนโลยี 224G SerDes ร่วมกับความก้าวหน้าใน MAC และ PCS IP ทำให้สามารถเข้าถึงโซลูชันที่ครอบคลุมซึ่งสอดคล้องกับมาตรฐานอีเธอร์เน็ต 1.6T ที่พัฒนาอย่างต่อเนื่อง นอกจากนี้ เนื่องจากเวลาแฝงภายในโปรโตคอลและวิธีการแก้ไขข้อผิดพลาด การออกแบบ IP ดิจิทัลและแอนะล็อกจึงต้องได้รับการออกแบบอย่างขยันขันแข็งโดยนักออกแบบผู้เชี่ยวชาญ เพื่อหลีกเลี่ยงการนำเวลาแฝงที่ไม่จำเป็นเข้าสู่ดาต้าพาธ

การบรรลุประสิทธิภาพสูงสุดสำหรับการออกแบบ SoC 1.6T จำเป็นต้องมีสถาปัตยกรรมที่ได้รับการปรับให้เหมาะสมอย่างมีประสิทธิภาพและแนวทางปฏิบัติในการออกแบบที่พิถีพิถันสำหรับส่วนประกอบชิปทุกตัว สิ่งนี้เน้นการอนุรักษ์พลังงานและลดการปล่อยซิลิคอนให้เหลือน้อยที่สุด ทำให้อัตราข้อมูล 1.6T เป็นจริง Synopsys 224G Ethernet PHY IP ที่ได้รับการพิสูจน์แล้วจากซิลิคอน ได้วางรากฐานสำหรับคอนโทรลเลอร์ 1.6T MAC และ PCS ด้วยการใช้การออกแบบ การวิเคราะห์ การจำลอง และเทคนิคการวัดระดับแนวหน้า Synopsys ยังคงให้ความสมบูรณ์ของสัญญาณที่ยอดเยี่ยมและประสิทธิภาพการกระวนกระวายใจ พร้อมด้วย โซลูชันอีเธอร์เน็ตที่สมบูรณ์ รวมถึง MAC+PCS+PHY.

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- PlatoData.Network Vertical Generative Ai เพิ่มพลังให้กับตัวเอง เข้าถึงได้ที่นี่.

- เพลโตไอสตรีม. Web3 อัจฉริยะ ขยายความรู้ เข้าถึงได้ที่นี่.

- เพลโตESG. คาร์บอน, คลีนเทค, พลังงาน, สิ่งแวดล้อม แสงอาทิตย์, การจัดการของเสีย. เข้าถึงได้ที่นี่.

- เพลโตสุขภาพ เทคโนโลยีชีวภาพและข่าวกรองการทดลองทางคลินิก เข้าถึงได้ที่นี่.

- ที่มา: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :มี

- :เป็น

- :ไม่

- :ที่ไหน

- $ ขึ้น

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- เข้า

- สามารถเข้าถึงได้

- การบัญชี

- ถูกต้อง

- บรรลุ

- ข้าม

- กิจกรรม

- ที่เพิ่ม

- เพิ่มเติม

- นอกจากนี้

- การนำ

- ความก้าวหน้า

- advancing

- กับ

- การเล็ง

- อนุญาตให้

- แล้ว

- ด้วย

- แม้ว่า

- เสมอ

- ท่ามกลาง

- จำนวน

- ขยาย

- an

- การวิเคราะห์

- และ

- ที่คาดว่าจะ

- การใช้งาน

- การใช้งาน

- เข้าใกล้

- สถาปัตยกรรม

- เป็น

- AS

- At

- หลีกเลี่ยง

- Back-end

- ฉากหลัง

- แบนด์วิดธ์

- BE

- จะกลายเป็น

- ระหว่าง

- เกิน

- บิต

- ปิดกั้น

- หนุน

- การส่งเสริม

- นำ

- สร้าง

- แต่

- by

- สายเคเบิล

- สายเคเบิ้ล

- CAN

- ความจุ

- พกพา

- ความท้าทาย

- ช่อง

- ชิป

- ชิป

- เลือก

- สถานการณ์

- ไคลเอนต์

- นาฬิกา

- เมฆ

- คอมพิวเตอร์เมฆ

- รหัส

- รวม

- การรวมกัน

- การสื่อสาร

- สมบูรณ์

- เสร็จสิ้น

- ส่วนประกอบ

- ส่วนประกอบ

- ครอบคลุม

- ประกอบไปด้วย

- การคำนวณ

- กังวล

- ร่วม

- งานที่เชื่อมต่อ

- การเชื่อมต่อ

- การอนุรักษ์

- พิจารณา

- การพิจารณา

- คงเส้นคงวา

- อย่างต่อเนื่อง

- อย่างต่อเนื่อง

- สนับสนุน

- ควบคุม

- ตัวควบคุม

- การแปลง

- ทองแดง

- แกน

- ค่าใช้จ่าย

- ตอบโต้

- หลักสูตร

- ที่สร้างขึ้น

- สร้าง

- ปัจจุบัน

- ข้อมูล

- ศูนย์ข้อมูล

- เปิดตัว

- ความล่าช้า

- ส่งมอบ

- ความต้องการ

- เรียกร้อง

- ความต้องการ

- ภาพวาด

- ออกแบบ

- นักออกแบบ

- การออกแบบ

- การตรวจพบ

- อุปกรณ์

- บงการ

- ต่าง

- ดิจิตอล

- ขันแข็ง

- แสดง

- ระยะทาง

- กระจาย

- ไม่

- การเสแสร้ง

- สอง

- ระยะเวลา

- ในระหว่าง

- แต่ละ

- ก่อน

- ระบบนิเวศ

- มีประสิทธิภาพ

- มีประสิทธิภาพ

- อย่างมีประสิทธิภาพ

- ที่มีประสิทธิภาพ

- อย่างมีประสิทธิภาพ

- ความพยายาม

- ภาวะฉุกเฉิน

- เน้น

- เน้น

- การจ้างงาน

- จ้าง

- ช่วยให้

- การเปิดใช้งาน

- ครอบคลุม

- ปลาย

- จบสิ้น

- เพื่อให้แน่ใจ

- ทั้งหมด

- ความผิดพลาด

- ข้อผิดพลาด

- การเพิ่ม

- แก่นแท้

- จำเป็น

- เป็นหลัก

- อีเธอร์ (ETH)

- แม้

- ทุกๆ

- ชัดเจน

- การพัฒนา

- ตัวอย่าง

- เป็นพิเศษ

- การยกเว้น

- ที่ขยาย

- การขยายตัว

- ที่คาดหวัง

- ชำนาญ

- ความชำนาญ

- ขยายออก

- การขยาย

- ภายนอก

- การสกัด

- Eyes

- ปัจจัย

- ปัจจัย

- ไกล

- เร็วขึ้น

- คุณสมบัติ

- ที่มีคุณสมบัติ

- รูป

- หา

- ชื่อจริง

- รุ่นแรก

- ไหล

- มุ่งเน้น

- ตาม

- รอยพระบาท

- สำหรับ

- การกำหนด

- ข้างหน้า

- FRAME

- ราคาเริ่มต้นที่

- ต่อไป

- รุ่น

- จะช่วยให้

- มากขึ้น

- บัญชีกลุ่ม

- กลุ่ม

- การเจริญเติบโต

- มือ

- การจัดการ

- จุดสูง

- ประสิทธิภาพสูง

- อย่างสูง

- อย่างไรก็ตาม

- HTML

- HTTPS

- ความจำเป็น

- การดำเนินงาน

- ความสำคัญ

- สำคัญ

- การปรับปรุง

- in

- ในอื่น ๆ

- ประกอบด้วย

- รวมทั้ง

- ที่เพิ่มขึ้น

- เป็นรายบุคคล

- อุตสาหกรรม

- อิทธิพล

- โดยธรรมชาติ

- อย่างโดยเนื้อแท้

- เริ่มต้น

- Initiative

- ตัวอย่าง

- รวม

- บูรณาการ

- ความสมบูรณ์

- อินเตอร์เฟซ

- อินเตอร์เฟซ

- อินเทอร์เน็ต

- การทำงานร่วมกัน

- เข้าไป

- แท้จริง

- แนะนำ

- เปิดตัว

- แนะนำ

- ที่เกี่ยวข้องกับการ

- IP

- IT

- ซ้ำ

- ITS

- ตัวเอง

- jpg

- เลน

- ความแอบแฝง

- ชั้น

- ชั้น

- ความยาว

- ระดับ

- การใช้ประโยชน์

- น่าจะ

- Line

- เส้น

- LINK

- การเชื่อมโยง

- สด

- อีกต่อไป

- ต่ำ

- Mac

- การทำ

- จัดการ

- การจัดการ

- ความกว้างสูงสุด

- สูงสุด

- อาจ..

- หมายความ

- การวัด

- กลไก

- กลาง

- หน่วยความจำ

- ข่าวสาร

- วิธี

- วิธีการ

- พิถีพิถัน

- ต่ำสุด

- ลด

- ย่อขนาด

- การลด

- โมดูล

- โมดูล

- ข้อมูลเพิ่มเติม

- มากที่สุด

- ต้อง

- ใกล้

- จำเป็นต้อง

- เครือข่าย

- แต่

- ไม่

- หมายเหตุ

- ตอนนี้

- วัตถุประสงค์

- of

- มักจะ

- on

- ONE

- เพียง

- การดำเนินงาน

- การปรับให้เหมาะสม

- เพิ่มประสิทธิภาพ

- ตัวเลือกเสริม (Option)

- or

- อื่นๆ

- เกิน

- ทั้งหมด

- คู่

- พารามิเตอร์

- โดยเฉพาะ

- เส้นทาง

- เครื่องคอมพิวเตอร์

- ต่อ

- การปฏิบัติ

- การแสดง

- กายภาพ

- ทางร่างกาย

- ท่อ

- เป็นจุดสำคัญ

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- เล่น

- บวก

- ที่มีศักยภาพ

- อำนาจ

- การปฏิบัติ

- ส่วนใหญ่

- ประถม

- กระบวนการ

- การประมวลผล

- โปรเซสเซอร์

- ในอาชีพ

- ที่คาดการณ์

- การป้องกัน

- โปรโตคอล

- ชีพจร

- วัตถุประสงค์

- ใจเร่งเร้า

- คุณภาพ

- วิทยุ

- สุ่ม

- พิสัย

- คะแนน

- ราคา

- มาถึง

- ถึง

- ปฏิกิริยา

- ความจริง

- รับ

- การได้รับ

- การต้อนรับ

- ลด

- น่าเชื่อถือ

- ซากศพ

- การแสดงผล

- ต้อง

- หวงห้าม

- ส่งผลให้

- แข็งแรง

- บทบาท

- ซึ่งได้หยั่งราก

- วิ่ง

- scalability

- ขนาด

- สถานการณ์

- ไร้รอยต่อ

- ที่สอง

- เห็น

- ส่วน

- มีความละเอียดอ่อน

- แยก

- ให้บริการ

- บริการ

- ชุด

- หลาย

- ที่ใช้ร่วมกัน

- สั้น

- น่า

- การจัดแสดง

- สัญญาณ

- อย่างมีความหมาย

- ซิลิคอน

- จำลอง

- ขนาด

- So

- ทางออก

- โซลูชัน

- ครอบคลุม

- หัวหอก

- โดยเฉพาะ

- เฉพาะ

- สเปค

- ความเร็ว

- ฤดูใบไม้ผลิ

- ระยะ

- มาตรฐาน

- มาตรฐาน

- มาตรฐาน

- การเก็บรักษา

- กลยุทธ์

- ที่พริ้ว

- ภายหลัง

- เป็นกอบเป็นกำ

- ความสำเร็จ

- อย่างเช่น

- เหมาะสม

- สนับสนุน

- เครื่องหมาย

- ระบบ

- ปรับปรุง

- ใช้เวลา

- เทคนิค

- เทคนิค

- เทคโนโลยี

- กว่า

- ที่

- พื้นที่

- ของพวกเขา

- ที่นั่น

- ดังนั้น

- ดังนั้น

- ล้อยางขัดเหล่านี้ติดตั้งบนแกน XNUMX (มม.) ผลิตภัณฑ์นี้ถูกผลิตในหลายรูปทรง และหลากหลายเบอร์ความแน่นหนาของปริมาณอนุภาคขัดของมัน จะทำให้ท่านได้รับประสิทธิภาพสูงในการขัดและการใช้งานที่ยาวนาน

- นี้

- ตลอด

- ดังนั้น

- เห็บ

- ผูก

- เวลา

- ครั้ง

- ไปยัง

- ด้านบน

- แบบดั้งเดิม

- การจราจร

- โอน

- ส่งผ่าน

- ทริปเปิ

- สอง

- ตามแบบฉบับ

- เป็นปกติ

- หลีกไม่ได้

- ความเข้าใจ

- รับหน้าที่

- หน่วย

- ที่กำลังมา

- เมื่อ

- การใช้

- นำไปใช้

- ผ่านทาง

- เห็นภาพ

- ทาง..

- we

- เมื่อ

- ที่

- ในขณะที่

- กว้าง

- กับ

- ภายใน

- จะ

- ยัง

- ลมทะเล

- เป็นศูนย์