ความต้านทานของทองแดงขึ้นอยู่กับโครงสร้างผลึก ปริมาตรโมฆะ ขอบเขตของเกรน และส่วนต่อประสานของวัสดุที่ไม่ตรงกัน ซึ่งจะมีความสำคัญมากขึ้นในสเกลที่เล็กลง การก่อตัวของลวดทองแดง (Cu) แบบดั้งเดิมทำได้โดยการสลักลวดลายร่องลึกก้นสมุทรในซิลิคอนไดออกไซด์ที่มีค่า k ต่ำโดยใช้กระบวนการกัดร่องลึก และต่อมาเติม Cu ด้วยการไหลดามัสซีน น่าเสียดายที่วิธีนี้สร้างโครงสร้างผลึกหลายชั้นที่มีขอบเขตและช่องว่างของเกรนอย่างมีนัยสำคัญ ซึ่งจะเพิ่มความต้านทานของลวด Cu วัสดุซับ TaN ที่มีความต้านทานสูงยังถูกนำมาใช้ในกระบวนการนี้เพื่อป้องกันการแพร่กระจายของ Cu ในระหว่างกระบวนการหลอมดามาซีน

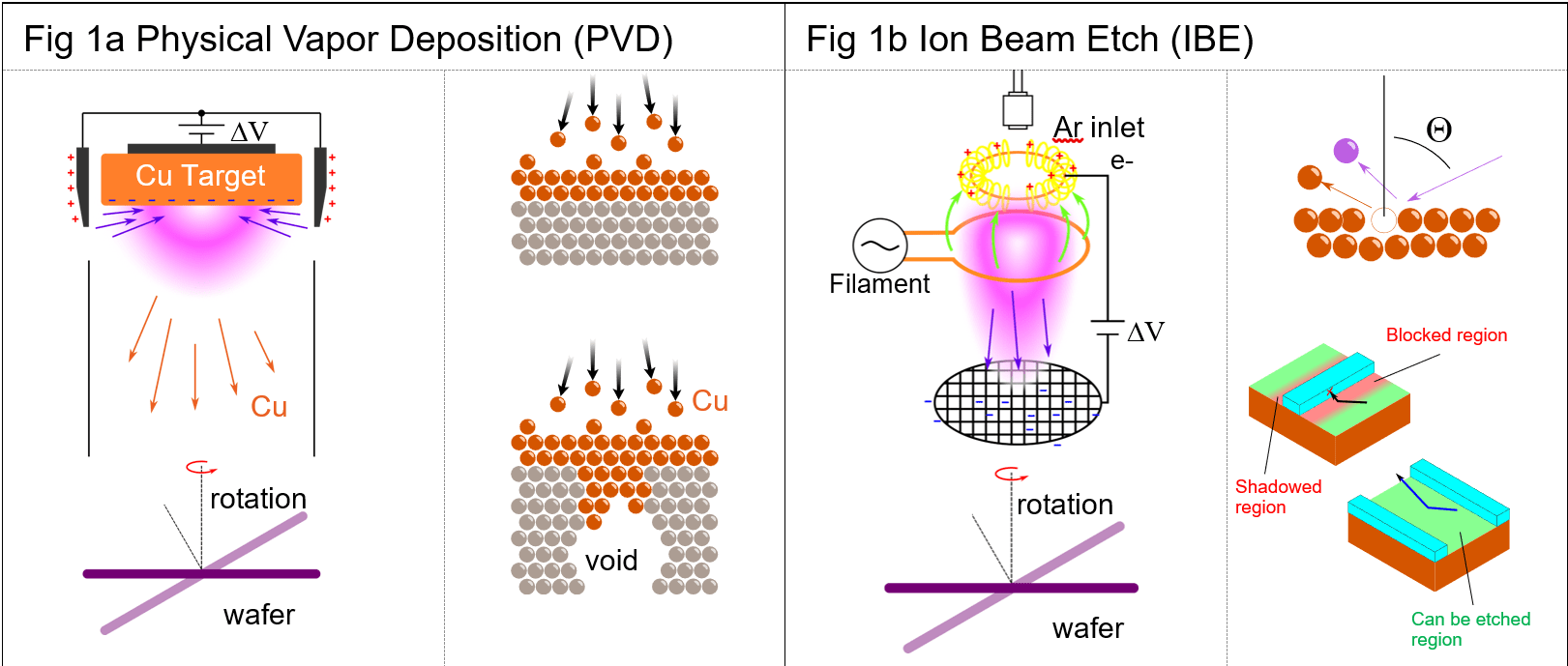

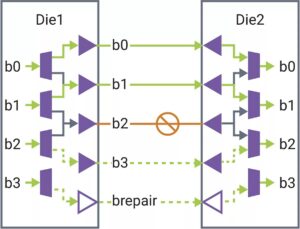

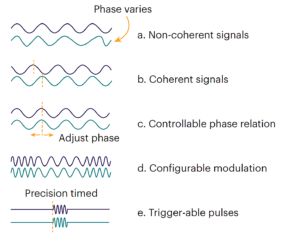

การสะสมไอทางกายภาพ (PVD) สามารถใช้ในการสะสมทองแดงด้วยพลังงานจลน์สูง (ระหว่าง 10 ถึง 100 eV) ทำให้เกิดความต้านทานต่ำ โครงสร้างผลึกเดี่ยวหนาแน่น ข้อเสียเปรียบของ PVD ก็คือการสะสมของ PVD มีแนวการมองเห็นและสามารถสะสมบนพื้นผิวเรียบได้อย่างสม่ำเสมอเท่านั้น ไม่สามารถใช้อุดหลุมลึกหรือร่องลึกได้ (รูปที่ 1a) ในการสร้างรูปร่างลวดที่แยกได้นั้น ชั้น Cu สม่ำเสมอจะต้องถูกวางบนพื้นผิวเรียบ จากนั้นจึงกัดด้วยลำแสงไอออน Cu ไม่มีสารประกอบระเหยที่มีก๊าซที่เกิดปฏิกิริยา ดังนั้นจึงไม่สามารถใช้กระบวนการกัดกรดปฏิกิริยาได้ ไอออน Ar เร่งที่สร้างขึ้นระหว่างการกัดลำแสงไอออน (IBE) สามารถกำจัด Cu ออกได้หากมุมตกกระทบสูงมาก ขออภัย พื้นที่ที่แกะสลักได้จะถูกจำกัดเนื่องจากเอฟเฟกต์เงาของหน้ากาก รูปที่ 1b แสดงบริเวณ (สีแดง) ซึ่งไม่สามารถแกะสลักวัสดุได้เมื่อหน้ากากตั้งฉากกับลำแสงไอออนที่เข้ามา ความล้มเหลวในการกัดนี้เกิดขึ้นเนื่องจากการแชโดว์หรือการอุดตันของเส้นทางของอะตอมที่ถูกดีดออกมา เมื่อมาส์กขนานกับเส้นทางของไอออน บริเวณที่ไม่ถูกมาส์กทั้งหมดสามารถแกะสลักได้ ดังนั้นการแกะสลักลำแสงไอออนจึงจำกัดอยู่เพียงการแกะสลักมาสก์รูปทรงเส้นที่มีความยาวตามใจชอบ

![]()

รูปที่ 1: (1a) การสะสมไอทางกายภาพ (PVD); (1b) ไอออนบีมกัด (IBE)

ขั้นตอนกระบวนการและกระบวนการผลิตเสมือนจริง

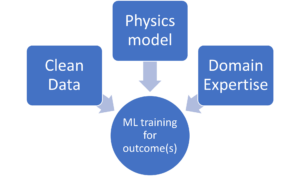

เพื่อให้เข้าใจถึงผลกระทบของการสะสมและการกัดต่อความต้านทานของเส้น ตอนนี้เราสร้างแบบจำลองกระบวนการกัด PVD และ IBE โดยใช้ฟังก์ชันการสะสมและการกัดการมองเห็น SEMulator3D PVD ได้รับการทำซ้ำโดยใช้กระบวนการสะสมที่มองเห็นการแพร่กระจายเชิงมุม 30 องศาใน SEMulator3D ซึ่งจำลองลักษณะสุ่มของอะตอม Cu ที่ถูกดีดออกมาอย่างแม่นยำในระหว่างการระดมยิงด้วยไอออน AR IBE ได้รับการทำซ้ำในแบบจำลองโดยใช้การกัดการมองเห็นด้วยการแพร่กระจายเชิงมุม 2 องศาและการเอียงมุมเชิงขั้ว 60 องศา เพื่อสะท้อนพฤติกรรมของไอออนเร่งกริดที่มีความแตกต่างของลำแสงต่ำ เวเฟอร์ทั้งสองจะถือว่ามีการหมุนอย่างอิสระ ขั้นตอนกระบวนการอื่นๆ ได้รับการปรับเปลี่ยนในกระบวนการผลิตเสมือนจริงเพื่อรองรับข้อจำกัดของ IBE และ PVD รูปที่ 2 แสดงโครงสร้างเดียวกันที่สร้างขึ้นโดยใช้ทั้งการเติม damascene Cu (รูปที่ 2a) และกระบวนการ PVD/IBE (รูปที่ 2b) ขั้นตอนกระบวนการเพิ่มเติมถูกรวมไว้เพื่อรวมข้อจำกัดบางประการของ PVD/IBE และสร้างรูปร่างที่เทียบเท่าสำหรับโครงสร้างส่วนปลายที่เราต้องการ

![]()

รูปที่ 2: (2a) Damascene เติมลวด Cu; (2b) การผลิตลวด PVD/IBE Cu

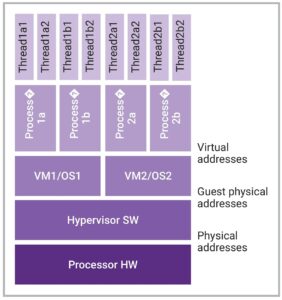

จากนั้นเราจะแสดงให้เห็นว่าสามารถประดิษฐ์เซลล์วงจร SRAM ขนาด 16 นาโนเมตรที่เทียบเท่ากันด้วยสายไฟ PVD/IBE ในขณะที่ปฏิบัติตามข้อจำกัดเหล่านี้ เนื่องจากชั้นโลหะทั้งหมดที่อยู่เหนือปลายตรงกลางของเส้นถูกสร้างขึ้นจากพื้นผิวเรียบ จึงทำให้เป็นตัวเลือกแนวคิดสำหรับสายไฟ PVD/IBE ซึ่งแตกต่างจากโทโพโลยีการเชื่อมต่อระหว่างกันที่ซับซ้อนที่เห็นในอุปกรณ์ finFET รูปที่ 3 แสดงโครงสร้างแบบแยกส่วนของแต่ละชั้นโลหะ และขั้นตอนที่จำเป็นในการสร้างโครงสร้าง finFET ชั้นโลหะสามชั้นโดยใช้ PVD/IBE

![]()

รูปที่ 3: (3a) FinFET MEOL ขนาด 16 นาโนเมตร และชั้นโลหะ 3 ชั้น (3b) การสร้างชั้นโลหะทีละขั้นตอนผ่าน PVD/IBE

ผลการต่อต้านและข้อสรุป

จากนั้น เราจะวัดความต้านทานไฟฟ้าของสายไฟจากชั้นโลหะบนสุดไปจนถึงจุดผ่านของช่อง finFET P และ N สำหรับทั้งการไหลดามัสกัสและการสะสมไอทางกายภาพ รูปที่ 4 แสดงจุดเริ่มต้นและจุดสิ้นสุดของการวัดความต้านทานที่ช่อง P และ N (วัสดุฉนวนอื่นๆ ทั้งหมดมีความโปร่งใส) เพื่อชดเชยความต้านทานส่วนต่อประสานระหว่างซับ TaN และลวดทองแดง ความต้านทานของทองแดงจึงเพิ่มขึ้นโดยใช้ค่าคงที่การสลายตัวแบบเอ็กซ์โพเนนเชียลที่ 1 นาโนเมตรเป็นฟังก์ชันของระยะห่างที่ใกล้ที่สุดกับส่วนต่อประสาน TaN เนื่องจากการทับถม Cu ของ damascene ไม่คาดว่าจะกลายเป็นผลึกอย่างสมบูรณ์ ความต้านทานของ Cu จึงเพิ่มขึ้น 50% กระบวนการทองแดง PVD/IBE ไม่ได้ใช้ซับ TaN ดังนั้นจึงไม่มีการใช้ฟังก์ชันการสลายตัวแบบเอ็กซ์โปเนนเชียล และใช้ความต้านทานรวมของทองแดงในแบบจำลองนี้ ตารางความต้านทานเปรียบเทียบการไหล Damascene กับ PVD รวมอยู่ในรูปที่ 4

![]()

รูปที่ 4: จุดเริ่มต้นและจุดสิ้นสุดของการวัดความต้านทานที่ช่อง P และ N

ค่าความต้านทานที่คำนวณจากแบบจำลองของเราระบุว่าเราสามารถบรรลุความต้านทานลดลง 67% โดยใช้วิธีการผลิต IBE/PVD เมื่อเปรียบเทียบกับการสลักร่องลึกแบบธรรมดาตามด้วยการสะสมของดามัสกัส สิ่งนี้เกิดขึ้นเนื่องจากไม่จำเป็นต้องใช้ไลเนอร์ TaN ใน IBE/PVD และมีความต้านทาน CU ต่ำกว่าในระหว่างกระบวนการนี้ ผลลัพธ์ของเราระบุว่าการปรับปรุงความต้านทานสามารถทำได้โดยใช้ IBE/PVD เมื่อเปรียบเทียบกับการเติม damascene ในระหว่างการสร้างเส้นโลหะ โดยมีต้นทุนของกระบวนการผลิตที่ซับซ้อนมากขึ้น

ทิโมธี หยาง

(ทุกกระทู้)

Timothy Yang เป็นวิศวกรแอพพลิเคชั่นซอฟต์แวร์ที่ Coventor ซึ่งเป็นบริษัท Lam Research เขาทำงานในด้านการพัฒนากระบวนการ การบูรณาการ และการปรับปรุงประสิทธิภาพการทำงาน โดยมีความเชี่ยวชาญในด้านเทคโนโลยีหน่วยความจำ ก่อนมาทำงานที่ Coventor Yang เคยทำงานที่ Tokyo Electron ในการพัฒนารูปแบบการกัดกรด เทคนิคการปรับปรุงรูปแบบการพิมพ์หินหลังการพิมพ์ การควบคุมการไหลของกระบวนการสำหรับแอปพลิเคชันการสร้างลวดลาย SADP และ SAQP และ EUV และเทคโนโลยีโฟโตรีซิสต์การพิมพ์หินแบบแช่ Yang สำเร็จการศึกษาระดับปริญญาตรีสาขาฟิสิกส์จาก UCLA ปริญญาโทสาขาวิทยาศาสตร์วัสดุจาก Chiba Institute of Technology และปริญญาเอก ปริญญาสาขาวัสดุศาสตร์จากมหาวิทยาลัยโทโฮกุ

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- เพลโตบล็อคเชน Web3 Metaverse ข่าวกรอง ขยายความรู้. เข้าถึงได้ที่นี่.

- การสร้างอนาคตโดย Adryenn Ashley เข้าถึงได้ที่นี่.

- ที่มา: https://semiengineering.com/a-deposition-and-etch-technique-to-lower-resistance-of-semiconductor-metal-lines/

- :มี

- :เป็น

- ][หน้า

- 1

- 10

- 100

- a

- ข้างบน

- เร่ง

- อำนวยความสะดวก

- แม่นยำ

- บรรลุ

- ประสบความสำเร็จ

- เพิ่มเติม

- ปรับ

- ทั้งหมด

- โพสต์ทั้งหมด

- และ

- เชิงมุม

- การใช้งาน

- ประยุกต์

- AR

- เป็น

- AS

- สันนิษฐาน

- At

- อะตอม

- BE

- คาน

- จะกลายเป็น

- รับ

- ระหว่าง

- เขตแดน

- by

- คำนวณ

- CAN

- ผู้สมัคร

- ไม่ได้

- บาง

- ช่อง

- บริษัท

- เมื่อเทียบกับ

- เปรียบเทียบ

- ซับซ้อน

- คงที่

- ข้อ จำกัด

- ควบคุม

- ตามธรรมเนียม

- ทองแดง

- ราคา

- สร้าง

- ที่สร้างขึ้น

- คริสตัล

- ข้อมูล

- ลดลง

- ลึก

- องศา

- สาธิต

- ขึ้นอยู่กับ

- ฝากเงิน

- ฝาก

- ที่ต้องการ

- ที่กำลังพัฒนา

- พัฒนาการ

- เครื่อง

- การจัดจำหน่าย

- แสดง

- ระยะทาง

- การแตกต่าง

- ลง

- ในระหว่าง

- แต่ละ

- ผล

- ผลกระทบ

- ทั้ง

- วิศวกร

- เท่ากัน

- EV

- ที่คาดหวัง

- ความชำนาญ

- ที่ชี้แจง

- ความล้มเหลว

- รูป

- ใส่

- แบน

- ไหล

- ตาม

- สำหรับ

- ฟอร์ม

- การสร้าง

- รูปแบบ

- ฟรี

- ราคาเริ่มต้นที่

- อย่างเต็มที่

- ฟังก์ชัน

- ฟังก์ชั่น

- ตะแกรง

- มี

- he

- จุดสูง

- อย่างสูง

- หลุม

- HTTPS

- ความคิด

- การแช่

- การปรับปรุง

- การปรับปรุง

- in

- อุบัติการณ์

- รวม

- ขาเข้า

- รวมเข้าด้วยกัน

- เพิ่มขึ้น

- เพิ่มขึ้น

- แสดง

- สถาบัน

- บูรณาการ

- อินเตอร์เฟซ

- เปลี่ยว

- IT

- ITS

- jpg

- หวด

- ชั้น

- ชั้น

- ข้อ จำกัด

- ถูก จำกัด

- Line

- เส้น

- นาน

- ต่ำ

- ทำให้

- หน้ากาก

- มาสก์

- วัสดุ

- วัสดุ

- ความกว้างสูงสุด

- วัด

- หน่วยความจำ

- โลหะ

- วิธี

- กลาง

- แบบ

- โมเดล

- ข้อมูลเพิ่มเติม

- ธรรมชาติ

- จำเป็น

- จำเป็น

- of

- on

- ใบสั่ง

- อื่นๆ

- ของเรา

- Parallel

- เส้นทาง

- แบบแผน

- กายภาพ

- ทางร่างกาย

- ฟิสิกส์

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- จุด

- ขั้วโลก

- โพสต์

- โพสต์

- ป้องกัน

- ก่อน

- กระบวนการ

- กระบวนการ

- สุ่ม

- ที่ได้รับ

- สีแดง

- สะท้อน

- ภูมิภาค

- เอาออก

- การวิจัย

- ความต้านทาน

- ผลสอบ

- s

- เดียวกัน

- ตาชั่ง

- รูปแบบ

- วิทยาศาสตร์

- สารกึ่งตัวนำ

- รูปร่าง

- มีรูป

- รูปร่าง

- แสดงให้เห็นว่า

- สายตา

- สำคัญ

- ซิลิคอน

- ตั้งแต่

- เดียว

- มีขนาดเล็กกว่า

- So

- ซอฟต์แวร์

- กระจาย

- ที่เริ่มต้น

- สถานะ

- ขั้นตอน

- ขั้นตอน

- โครงสร้าง

- ต่อจากนั้น

- พื้นผิว

- ตาราง

- เทคนิค

- เทคโนโลยี

- เทคโนโลยี

- ที่

- พื้นที่

- ล้อยางขัดเหล่านี้ติดตั้งบนแกน XNUMX (มม.) ผลิตภัณฑ์นี้ถูกผลิตในหลายรูปทรง และหลากหลายเบอร์ความแน่นหนาของปริมาณอนุภาคขัดของมัน จะทำให้ท่านได้รับประสิทธิภาพสูงในการขัดและการใช้งานที่ยาวนาน

- สาม

- ภาพขนาดย่อ

- ไปยัง

- โตเกียว

- สูงสุด

- ตามธรรมเนียม

- โปร่งใส

- ยูซีแอล

- เข้าใจ

- มหาวิทยาลัย

- ใช้

- มือสอง

- ใช้

- ความคุ้มค่า

- ผ่านทาง

- เสมือน

- ความชัดเจน

- ระเหย

- ปริมาณ

- vs

- ที่

- ในขณะที่

- จะ

- ลวด

- กับ

- งาน

- ทำงาน

- โรงงาน

- ผล

- ลมทะเล