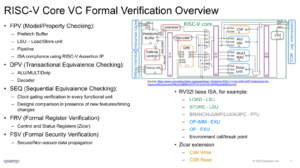

What’s different from other RISC-V designs and what’s needed to ensure it works as planned.

Verifying an SoC is very different than verifying a processor due to the huge state space in the processor. In addition to the tools needed for an SoC, additional tools are required for a step and compare environment. Larry Lapides, vice president at Imperas, talks about the need to verify asynchronous events like interrupts, how to compare a reference model to RTL, and the need for both hardware/software co-design and architectural analysis.

[embedded content]

Ed Sperling

(all posts)

Ed Sperling is the editor in chief of Semiconductor Engineering.

- SEO Powered Content & PR Distribution. Get Amplified Today.

- PlatoData.Network Vertical Generative Ai. Empower Yourself. Access Here.

- PlatoAiStream. Web3 Intelligence. Knowledge Amplified. Access Here.

- PlatoESG. Carbon, CleanTech, Energy, Environment, Solar, Waste Management. Access Here.

- PlatoHealth. Biotech and Clinical Trials Intelligence. Access Here.

- Source: https://semiengineering.com/verifying-a-risc-v-processor-model/

- :is

- 26

- 27

- 40

- 66

- 7

- 80

- a

- About

- addition

- Additional

- All

- All Posts

- an

- analysis

- and

- architectural

- ARE

- AS

- At

- both

- chief

- compare

- content

- designs

- different

- due

- ed

- editor

- embedded

- Engineering

- ensure

- Environment

- Ether (ETH)

- events

- For

- from

- How

- How To

- HTTPS

- huge

- in

- IT

- jpg

- like

- model

- Need

- needed

- of

- Other

- photo

- planned

- plato

- Plato Data Intelligence

- PlatoData

- popularity

- Posts

- president

- Processor

- reference

- required

- ROW

- semiconductor

- Space

- State

- Step

- Talks

- than

- The

- thumbnail

- to

- tools

- verify

- verifying

- very

- vice

- Vice President

- works

- youtube

- zephyrnet