Logic simulators have been around for decades providing a way for engineers to verify how their designs operate at the gate, RTL and SystemVerilog levels. Getting the fastest simulation speed is high on the priority list, because it means that a more thorough verification can be performed, improving the odds of first silicon success. Cadence recently presented a webinar on this topic for their simulator called Xcelium as part of a Techtalk series.

Ankur Jain from Cadence started out with the big picture of trying to maximize the number of bugs found per dollar, per day, by having the most efficient simulator and highest throughput. SoC designs are getting up to billion gate capacity, and the time to market pressures are relentless as competitors vie for a dominant and early product introduction.

Performance Switches

Two switches were recommended for all coding styles to improve simulation throughput:

- –newperf (helps SV Test bench, RTL, gate level and low power designs)

- –plusperf (helps assertions, RTL optimizations)

It’s even recommended that both of this switches be used together. Your simulation run times can be reduced by up to 1.5X or even 3X, depending on the specific coding style used.

Profiling

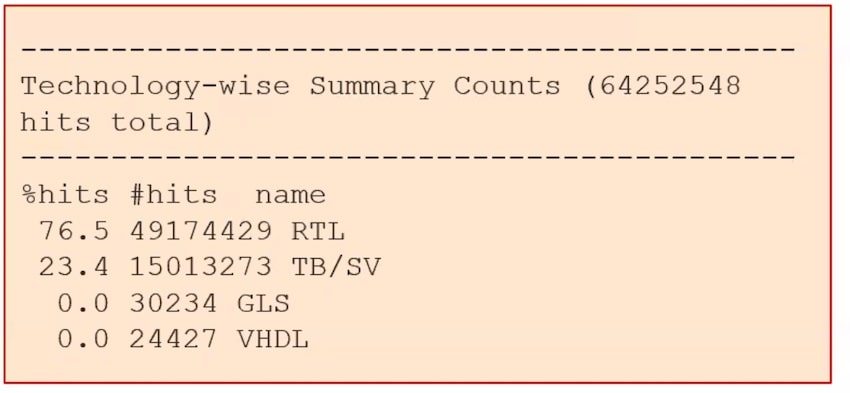

To gain better insight into the Xcelium simulator speed it was shown how to profile a simulation run to learn metrics like:

- Memory consumed, Cache size

- CPU utilization

- RTL time vs test bench time

- License loading times

For regression runs avoid using the -xprof option, as it incurs up to a 20% overhead penalty. Use the latest software release for better optimizations. If your runs are memory intensive, then consider running on CPUs with larger cache sizes.

Some simulator options to remove for improved speed are:

- -DISABLE_FORGEN_CAOPT

- -NOCAG

- -NODEADCODE

- -COVERGE all

- -ACCESS +rwc

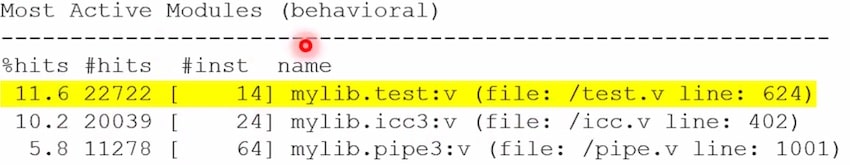

Profiling also shows you the most active modules, identifying which file and line number have the most hits. There are app notes at Cadence.com that provide best coding practices for improved speed.

Tuning the access levels in the simulator impact speed, so for highest performance use: r, nocellacces, accessreg.

Advanced Technologies

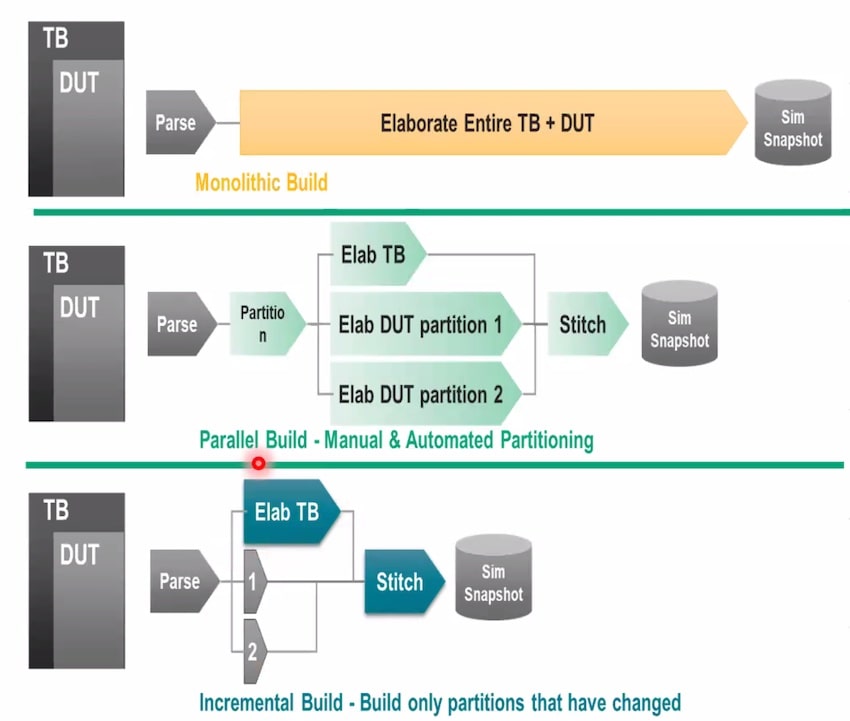

Four advanced technologies were shared in this Techtalk, providing up to a 10X gain in simulation run times. The first one was the build technology with parallel, incremental and hierarchical approaches. For the parallel and incremental build methods you can use automated or manual partitioning.

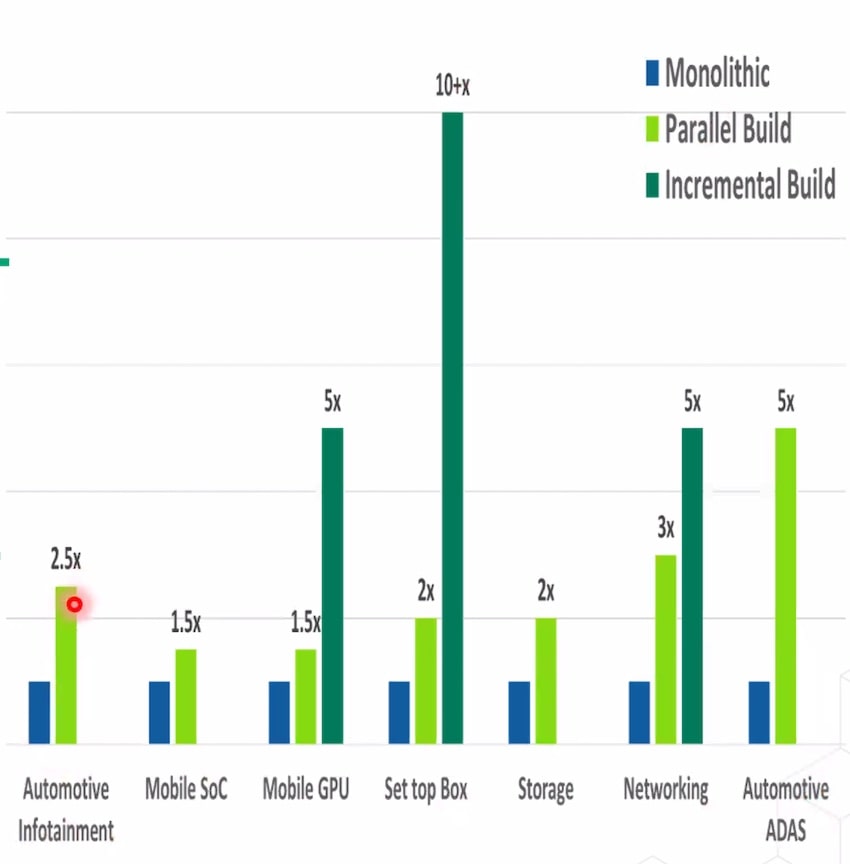

Results from several customer designs run through each build technology show the possible speed improvements, reaching up to 10X based on design and coding styles:

Save and Restore is the second advanced approach and is best used when your design requires a long initialization time, where you only need to run the initialization one time, save the design state, then use the restore for all subsequent runs.

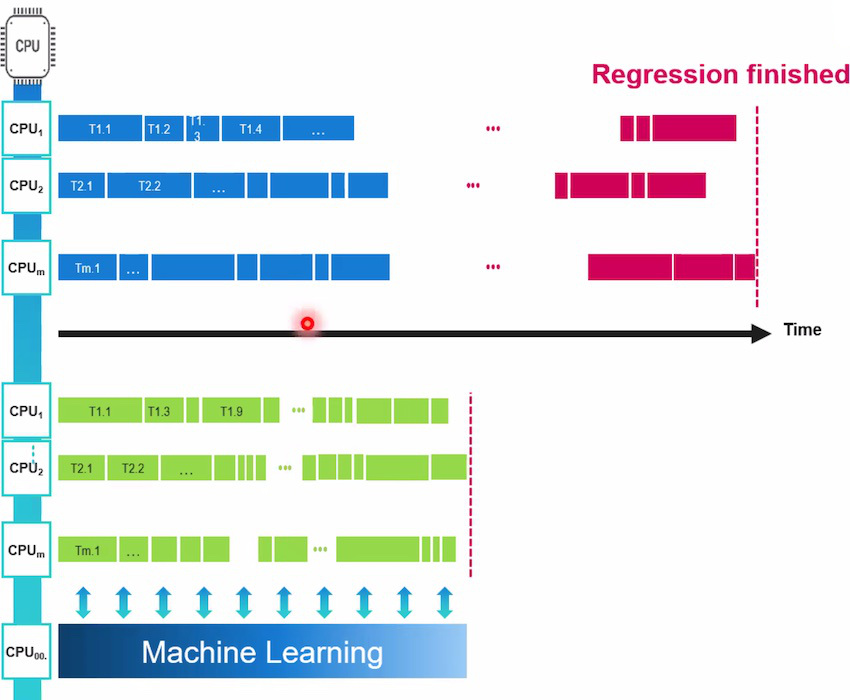

The third advanced feature is an app called Xcelium ML, which requires a license, and during regression runs it collects coverage data and the random seeds, analyzes how these impact coverage goals, then creates a better set of instructions as part of its model. It basically creates a leaner regression while reaching the same coverage.

The final advanced feature is called the Xcelium Multi-Core App, and it’s ideal for DFT gate-level simulations that are high activity by multi-threading the simulator kernel. Another use for the Multi-Core App is when running ATPG vectors in serial and parallel, where Zero-delay cases show a 5-10X improvement, and with SDF annotation 3-5X benefits. The final place to use Multi-Core App is for MBIST and LBIST, where you can expect a 2-3X gain.

Summary

Functional logic simulation may be a mature product category, yet innovation is still happening for Cadence Xcelium, and the best practices described in the Techtalk were time well spent, as the benefits are faster run times. Knowing how to use the performance switches, profiling, and using advanced technology will yield speed improvements. If you need a little assistance, then check out the Cadence support site, or give the local AE a phone call to start simulating faster.

Webinar

Attend the next Cadence TechTalk, Find Elusive Bus Faster with Xcelium ML, it’s on February 8th, 2023 at 9AM PDT.

Related Blogs

Share this post via:- SEO Powered Content & PR Distribution. Get Amplified Today.

- Platoblockchain. Web3 Metaverse Intelligence. Knowledge Amplified. Access Here.

- Source: https://semiwiki.com/eda/320077-fastest-logic-simulation-with-xcelium/

- 1

- 2023

- a

- access

- active

- activity

- advanced

- Advanced Technology

- All

- analyzes

- and

- Another

- app

- approach

- approaches

- around

- Assistance

- Automated

- based

- Basically

- because

- benefits

- BEST

- best practices

- Better

- Big

- Big Picture

- Billion

- bugs

- build

- bus

- cache

- Cadence

- call

- called

- Capacity

- cases

- Category

- check

- Coding

- collects

- COM

- competitors

- Consider

- consumed

- Cost

- coverage

- creates

- customer

- data

- day

- decades

- Depending

- described

- Design

- designs

- Dollar

- dominant

- during

- each

- Early

- efficient

- Engineers

- Even

- expect

- faster

- fastest

- Feature

- File

- final

- First

- found

- from

- Gain

- getting

- Give

- Goals

- having

- helps

- High

- highest

- Hits

- How

- How To

- HTTPS

- ideal

- identifying

- Impact

- improve

- improved

- improvement

- improvements

- improving

- in

- Innovation

- insight

- instructions

- Introduction

- IT

- Knowing

- larger

- latest

- LEARN

- Level

- levels

- License

- Line

- List

- little

- loading

- local

- Long

- Low

- manual

- Market

- mature

- max-width

- Maximize

- means

- Memory

- methods

- Metrics

- ML

- model

- Modules

- more

- most

- Need

- next

- Notes

- number

- Odds

- ONE

- operate

- Option

- Options

- Parallel

- part

- performance

- phone

- Phone call

- picture

- Place

- plato

- Plato Data Intelligence

- PlatoData

- possible

- Post

- power

- practices

- presented

- priority

- Product

- Profile

- profiling

- provide

- providing

- random

- recently

- recommended

- Reduced

- regression

- release

- relentless

- remove

- requires

- Run

- running

- same

- Save

- Second

- seeds

- serial

- Series

- set

- several

- shared

- show

- shown

- Shows

- Silicon

- simulation

- simulator

- site

- sizes

- So

- Software

- specific

- speed

- speeds

- spent

- start

- started

- State

- Still

- style

- subsequent

- success

- support

- Technologies

- Technology

- test

- The

- their

- Third

- Through

- throughput

- time

- times

- to

- together

- topic

- use

- Verification

- verify

- via

- webinar

- which

- will

- Yield

- Your

- zephyrnet