A new technical paper titled “REFRESH FPGAs: Sustainable FPGA Chiplet Architectures” was published by University of Notre Dame and University of Pittsburgh.

Abstract

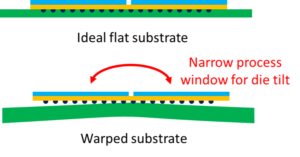

“There is a growing call for greater amounts of increasingly agile computational power for edge and cloud infrastructure to serve the computationally complex needs of ubiquitous computing devices. Thus, an important challenge is addressing the holistic environmental impacts of these next-generation computing systems. To accomplish this, a life-cycle view of sustainability for computing advancements is necessary to reduce environmental impacts such as greenhouse warming gas emissions from these computing choices. Unfortunately, decadal efforts to address operational energy efficiency in computing devices have ignored and in some cases exacerbated embodied impacts from manufacturing these edge and cloud systems, particularly their integrated circuits. During this time FPGA architectures have not changed dramatically except to increase in size. Given this context, we propose REFRESH FPGAs to build new FPGA devices and architectures from recently retired FPGA dies using 2.5D integration. To build REFRESH FPGAs requires creative architectures that leverage existing chiplet pins with an inexpensive to-manufacture interposer coupled with creative design automation. In this paper, we discuss how REFRESH FPGAs can leverage industry trends for renewable energy integration into data centers while providing an overall improvement for sustainability and amortizing their significant embodied cost investment over a much longer “first” lifetime.

Find the technical paper here. Published November 2023.

Zhou, Peipei, Jinming Zhuang, Stephen Cahoon, Yue Tang, Zhuoping Yang, Xingzhen Chen, Yiyu Shi, Jingtong Hu, and Alex K. Jones. “REFRESH FPGAs: Sustainable FPGA Chiplet Architectures.” arXiv preprint arXiv:2312.02991 (2023).

Related

Proprietary Vs. Commercial Chiplets

Who wins, who loses, and where are the big challenges for multi-vendor heterogeneous integration.

- SEO Powered Content & PR Distribution. Get Amplified Today.

- PlatoData.Network Vertical Generative Ai. Empower Yourself. Access Here.

- PlatoAiStream. Web3 Intelligence. Knowledge Amplified. Access Here.

- PlatoESG. Carbon, CleanTech, Energy, Environment, Solar, Waste Management. Access Here.

- PlatoHealth. Biotech and Clinical Trials Intelligence. Access Here.

- Source: https://semiengineering.com/environmentally-sustainable-fpgas-notre-dame-univ-of-pittsburgh/

- :is

- :not

- :where

- 2023

- a

- accomplish

- address

- addressing

- advancements

- agile

- alex

- amounts

- an

- and

- ARE

- AS

- Automation

- Big

- build

- by

- call

- CAN

- cases

- Centers

- challenge

- challenges

- changed

- chen

- choices

- Cloud

- cloud infrastructure

- commercial

- complex

- computational

- computational power

- computing

- context

- Cost

- coupled

- Creative

- data

- data centers

- Design

- Devices

- discuss

- dramatically

- during

- Edge

- efficiency

- efforts

- Emissions

- energy

- energy efficiency

- environmental

- environmentally

- Except

- existing

- For

- fpga

- from

- GAS

- given

- greater

- Growing

- Have

- holistic

- How

- HTTPS

- Impacts

- important

- improvement

- in

- Increase

- increasingly

- industry

- inexpensive

- Infrastructure

- integrated

- integration

- into

- investment

- jones

- Leverage

- life-cycle

- lifetime

- longer

- Loses

- manufacturing

- much

- necessary

- needs

- New

- next-generation

- November

- of

- operational

- over

- overall

- Paper

- particularly

- pins

- pittsburgh

- plato

- Plato Data Intelligence

- PlatoData

- power

- propose

- providing

- published

- recently

- reduce

- Renewable

- renewable energy

- requires

- serve

- significant

- Size

- some

- Stephen

- such

- Sustainability

- sustainable

- Systems

- tang

- Technical

- that

- The

- their

- These

- this

- Thus

- time

- titled

- to

- Trends

- ubiquitous

- unfortunately

- university

- using

- View

- vs

- was

- we

- while

- WHO

- Wins

- with

- zephyrnet