Scalable manycore architecture; thermal management and packaging of power devices; neuromorphic processor; auto creation of HBM architecture; processor fuzzing; vertical GeSn nanowire MOSFETs; automated chiplet design; self-driving 360/3D visual perception; EUV lithography; new 2D non-VdW materials.

New technical papers recently added to Semiconductor Engineering’s library:

| Technical Paper | Research Organizations |

|---|---|

| MemPool: A Scalable Manycore Architecture with a Low-Latency Shared L1 Memory | ETH Zurich and University of Bologna |

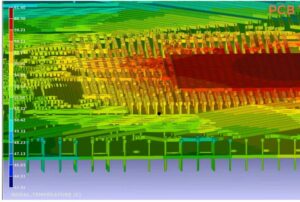

| Thermal management and packaging of wide and ultra-wide bandgap power devices: a review and perspective | Virginia Polytechnic Institute and State University, U.S. Naval Research Laboratory, and Univ Lyon, CNRS |

| Open the box of digital neuromorphic processor: Towards effective algorithm-hardware co-design | imec and KU Leuven |

| Automatic Creation of High-bandwidth Memory Architectures from Domain-specific Languages | Politecnico di Milano and TU Dresden |

| HyPFuzz: Formal-Assisted Processor Fuzzing | Texas A&M University and Technische Universität Darmstadt |

| Vertical GeSn nanowire MOSFETs for CMOS beyond beyond silicon | Peter Grünberg Institute 9, JARA, RWTH Aachen University, CEA, LETI, University of Grenoble Alpes, University of Leeds, and IHP |

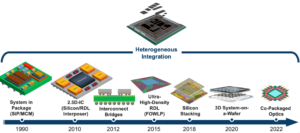

| Automated Design of Chiplets | UC Berkeley and Peking University |

| NVAutoNet: Fast and Accurate 360∘ 3D Visual Perception For Self Driving | NVIDIA |

| Particle charging during pulsed EUV exposures with afterglow effect | ASML, ISTEQ B.V., and Eindhoven University of Technology |

| A New Group of 2D Non-van der Waals Materials with Ultra Low Exfoliation Energies | TU Dresden, HZDR, and Aalto University |

If you have research papers you are trying to promote, we will review them to see if they are a good fit for our global audience. At a minimum, papers need to be well researched and documented, relevant to the semiconductor ecosystem, and free of marketing bias. There is no cost involved for us posting links to papers. Please send suggestions (via comments section below) for what else you’d like us to incorporate.

More Reading

Technical Paper Library home

Linda Christensen

(all posts)Linda Christensen is vice president of operations and a contributing writer at Semiconductor Engineering.

- SEO Powered Content & PR Distribution. Get Amplified Today.

- Platoblockchain. Web3 Metaverse Intelligence. Knowledge Amplified. Access Here.

- Minting the Future w Adryenn Ashley. Access Here.

- Source: https://semiengineering.com/chip-industrys-technical-paper-roundup-apr-18/

- :is

- 1

- 10

- 11

- 2D

- 3d

- 7

- 9

- a

- accurate

- added

- All

- All Posts

- and

- architecture

- ARE

- At

- audience

- auto

- Automated

- BE

- below

- Berkeley

- Beyond

- bias

- Box

- charging

- chip

- Christensen

- comments

- contributing

- Cost

- creation

- Design

- Devices

- digital

- during

- ecosystem

- Effective

- Engineering

- Even

- FAST

- fit

- For

- Free

- from

- Global

- global audience

- good

- Group

- Have

- HTTPS

- incorporate

- industry’s

- Institute

- involved

- laboratory

- Library

- like

- links

- Low

- Lyon

- management

- Marketing

- materials

- Memory

- MILANO

- minimum

- Need

- New

- of

- Operations

- our

- packaging

- Paper

- papers

- Peking

- perception

- plato

- Plato Data Intelligence

- PlatoData

- please

- popularity

- Posts

- power

- president

- Processor

- promote

- recently

- relevant

- research

- review

- roundup

- ROW

- s

- scalable

- Section

- self-driving

- semiconductor

- shared

- State

- Technical

- The

- Them

- thermal

- thumbnail

- to

- towards

- u.s.

- Ultra

- university

- us

- via

- Vice President

- WELL

- What

- wide

- will

- with

- writer

- zephyrnet

- Zurich