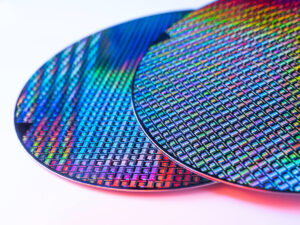

A new technical paper titled “Chiplet Placement for 2.5D IC with Sequence Pair Based Tree and Thermal Consideration” was published by researchers at National Yang Ming Chiao Tung University (Taiwan).

Abstract

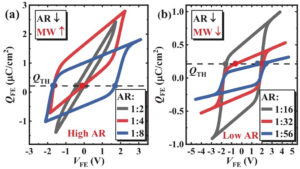

“This work develops an efficient chiplet placer with thermal consideration for 2.5D ICs. Combining the sequence-pair based tree, branch-and-bound method, and advanced placement/pruning techniques, the developed placer can find the solution fast with the optimized total wirelength (TWL) on half-perimeter wirelength (HPWL). Additionally, with the post placement procedure, the placer reduces maximum temperatures with slight increase of wirelength. Experimental results show that the placer can not only find better optimized TWL (reducing 1.035% HPWL) but also speed up at most two orders of magnitude than the prior art. With thermal consideration, the placer can reduce the maximum temperature up to 8.214 °C with an average 5.376% increase of TWL.”

Find the technical paper here. Published January 2023.

Hong-Wen Chiou, Jia-Hao Jiang, Yu-Teng Chang, Yu-Min Lee, and Chi-Wen Pan. 2023. Chiplet Placement for 2.5D IC with Sequence Pair Based Tree and Thermal Consideration. In Proceedings of the 28th Asia and South Pacific Design Automation Conference (ASPDAC ’23). Association for Computing Machinery, New York, NY, USA, 7–12. https://doi.org/10.1145/3566097.3567911

- SEO Powered Content & PR Distribution. Get Amplified Today.

- Platoblockchain. Web3 Metaverse Intelligence. Knowledge Amplified. Access Here.

- Source: https://semiengineering.com/chiplet-placer-with-thermal-consideration-for-2-5d-ics/

- 1

- 2023

- 214

- ACM

- Additionally

- advanced

- and

- Art

- asia

- Association

- Automation

- average

- based

- Better

- combining

- computing

- Conference

- consideration

- Design

- developed

- develops

- efficient

- FAST

- Find

- HTTPS

- ICS

- in

- Increase

- January

- Lee

- machinery

- maximum

- method

- most

- National

- New

- New York

- NY

- optimized

- orders

- Pacific

- PAN

- Paper

- plato

- Plato Data Intelligence

- PlatoData

- Post

- Prior

- Proceedings

- published

- reduce

- reduces

- reducing

- researchers

- Results

- Sequence

- show

- solution

- South

- speed

- Taiwan

- Technical

- techniques

- The

- thermal

- titled

- to

- Total

- university

- USA

- Work

- zephyrnet