Rezystywność miedzi zależy od jej struktury krystalicznej, objętości pustych przestrzeni, granic ziaren i niedopasowania międzyfazowego materiału, co staje się bardziej znaczące w mniejszych skalach. Tworzenie drutów miedzianych (Cu) tradycyjnie odbywa się poprzez wytrawianie wzoru rowu w dwutlenku krzemu o niskiej wartości k przy użyciu procesu wytrawiania rowów, a następnie wypełnianie rowu Cu za pomocą strumienia damasceńskiego. Niestety metoda ta wytwarza struktury multikrystaliczne ze znacznymi granicami ziaren i pustymi przestrzeniami, co zwiększa rezystancję drutu Cu. Wysoce rezystancyjny materiał wykładziny TaN jest również wykorzystywany w tym procesie, aby zapobiec dyfuzji Cu podczas procesu wyżarzania damasceńskiego.

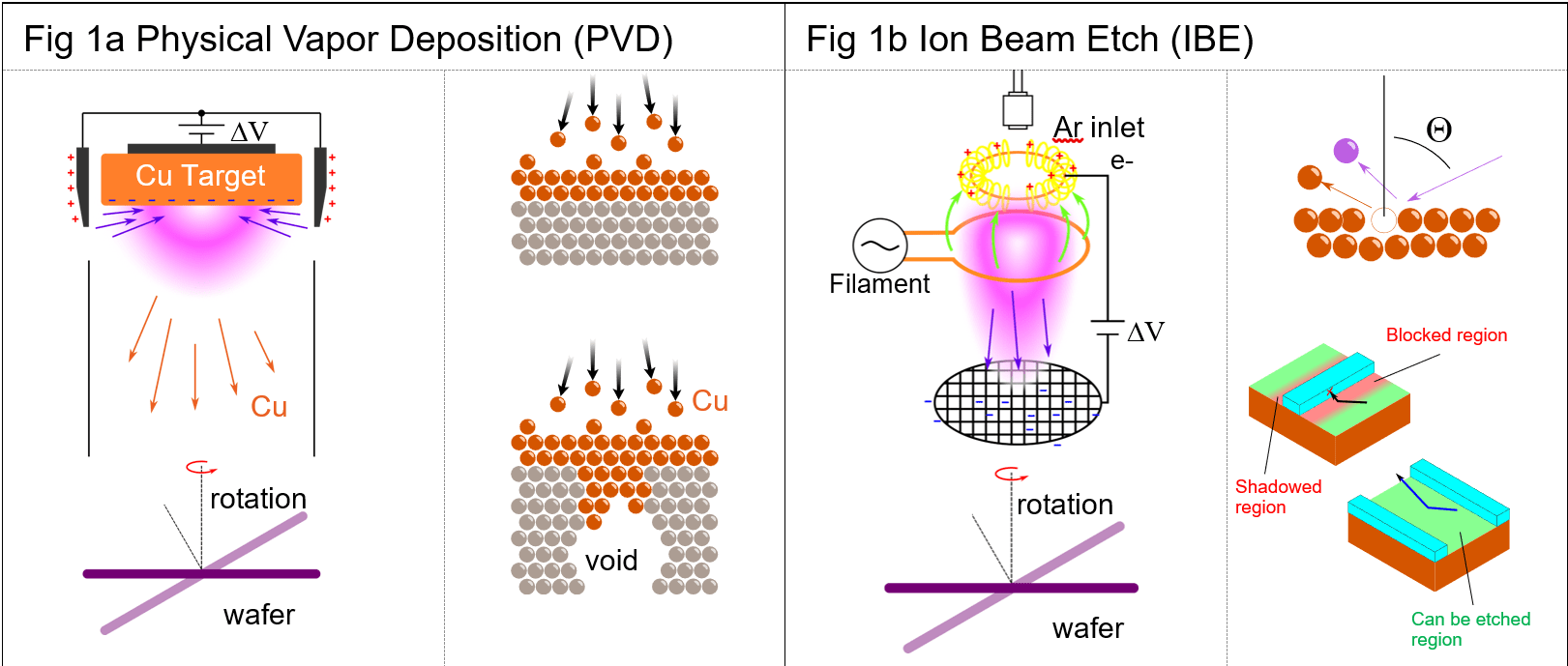

Fizyczne osadzanie z fazy gazowej (PVD) może być stosowane do osadzania miedzi przy wysokich energiach kinetycznych (od 10 do 100 eV), tworząc gęste struktury monokrystaliczne o niskiej rezystancji. Wadą PVD jest to, że osadzanie PVD ma rozłożoną linię widzenia i może być osadzane równomiernie tylko na płaskich powierzchniach. Nie można go używać do wypełniania głębokich otworów lub rowów (rysunek 1a). Aby utworzyć izolowane kształty drutów, jednorodna warstwa Cu musi zostać osadzona na płaskiej powierzchni, a następnie fizycznie wytrawiona wiązką jonów. Cu nie tworzy lotnych związków z reaktywnymi gazami, więc nie można zastosować reaktywnego procesu trawienia jonowego. Przyspieszone jony Ar powstające podczas trawienia wiązką jonów (IBE) mogą usuwać Cu, jeśli kąt padania jest bardzo wysoki. Niestety, możliwe do wytrawienia obszary będą ograniczone ze względu na efekt cieniowania maski. Rysunek 1b pokazuje obszary (na czerwono), w których materiału nie można wytrawić, gdy maska jest prostopadła do nadchodzącej wiązki jonów. To niepowodzenie wytrawiania występuje z powodu zacienienia lub zablokowania ścieżki wyrzuconego atomu. Gdy maska jest równoległa do ścieżki jonu, wszystkie niezamaskowane obszary mogą zostać wytrawione. Zatem wytrawianie wiązką jonów jest ograniczone do wytrawiania masek w kształcie linii o dowolnie długich długościach.

![]()

Ryc. 1: (1a) Fizyczne osadzanie z fazy gazowej (PVD); (1b) Wytrawianie wiązką jonów (IBE).

Etapy procesu i proces wirtualnej produkcji

Aby zrozumieć wpływ osadzania i wytrawiania na rezystancję linii, modelujemy teraz procesy wytrawiania PVD i IBE przy użyciu funkcji osadzania i wytrawiania widoczności SEMulator3D. PVD odtworzono przy użyciu procesu osadzania widzialności pod kątem 30 stopni w SEMulator3D, który dokładnie modeluje losową naturę wyrzucanych atomów Cu podczas bombardowania jonami AR. IBE został odtworzony w modelu przy użyciu wytrawiania widoczności z rozpiętością kątową 2 stopni i pochyleniem kąta biegunowego 60 stopni, aby odzwierciedlić zachowanie jonów przyspieszonych siatką z niską dywergencją wiązki. Zakłada się, że oba wafle mają swobodną rotację. Inne etapy procesu zostały dostosowane w procesie wirtualnej produkcji, aby uwzględnić ograniczenia IBE i PVD. Rysunek 2 przedstawia tę samą strukturę utworzoną zarówno przy użyciu damasceńskiego wypełnienia Cu (rysunek 2a), jak i procesu PVD/IBE (rysunek 2b). Uwzględniono dodatkowe etapy procesu, aby uwzględnić pewne ograniczenia PVD/IBE i stworzyć równoważny kształt dla naszych pożądanych struktur końcowych.

![]()

Ryc. 2: (2a) Wytwarzanie drutu Cu z wypełnieniem damasceńskim; (2b) Produkcja drutu Cu PVD/IBE.

Następnie pokazujemy, że równoważne ogniwo obwodu SRAM 16 nm można wyprodukować z drutów PVD/IBE, przestrzegając tych ograniczeń. Ponieważ wszystkie warstwy metalu powyżej środkowego końca linii są wykonane z płaskiej powierzchni, jest to idealny kandydat na przewody PVD/IBE, w przeciwieństwie do złożonych topologii połączeń obserwowanych w urządzeniu finFET. Rysunek 3 przedstawia izolowaną strukturę każdej warstwy metalu oraz kroki niezbędne do stworzenia trójwarstwowej struktury finFET przy użyciu PVD/IBE.

![]()

Rys. 3: (3a) 16 nm FinFET MEOL i 3 warstwy metalu; (3b) Wytwarzanie warstw metalu krok po kroku metodą PVD/IBE.

Wyniki odporności i wnioski

Następnie mierzymy rezystancję elektryczną drutów od najwyższej warstwy metalu do przelotek kanałów P i N finFET, zarówno dla przepływu damasceńskiego, jak i fizycznego osadzania z fazy gazowej. Rysunek 4 pokazuje punkt początkowy i punkt końcowy pomiaru rezystancji w kanałach P i N (wszystkie inne materiały izolacyjne są przezroczyste). Aby skompensować rezystancję interfejsu między wykładziną TaN a drutem miedzianym, rezystywność miedzi zwiększono, stosując wykładniczą stałą zaniku 1 nm jako funkcję najbliższej odległości do interfejsu TaN. Ponieważ nie oczekuje się, aby osadzanie Cu w wypełnieniu damasceńskim było w pełni krystaliczne, rezystywność Cu wzrosła o 50%. Proces miedzi PVD/IBE nie wykorzystuje wykładziny TaN, więc funkcja zaniku wykładniczego nie została zastosowana, a w tym modelu wykorzystano rezystywność masową miedzi. Tabela rezystywności porównująca przepływ damasceński z PVD znajduje się na rycinie 4.

![]()

Rys. 4: Punkt początkowy i punkt końcowy pomiaru rezystancji w kanałach P i N.

Wartości rezystancji obliczone na podstawie naszego modelu wskazują, że możemy osiągnąć 67% spadek rezystancji przy użyciu metody wytwarzania IBE/PVD w porównaniu z konwencjonalnym wytrawianiem rowów, po którym następuje osadzanie damasceńskie. Dzieje się tak, ponieważ w IBE/PVD nie jest potrzebna wkładka TaN, a rezystywność CU jest niższa podczas tego procesu. Nasze wyniki wskazują, że poprawę rezystywności można osiągnąć, stosując IBE/PVD w porównaniu z wypełnieniem damasceńskim podczas tworzenia linii metalowej, kosztem bardziej złożonego procesu produkcyjnego.

Tymoteusz Yang

(wszystkie posty)

Timothy Yang jest inżynierem oprogramowania w Coventor, firmie badawczej Lam. Zajmuje się rozwojem procesów, integracją i aplikacjami poprawiającymi wydajność, posiadając doświadczenie w technologiach pamięci. Przed podjęciem pracy w Coventor, Yang pracował w Tokyo Electron, opracowując schematy wytrawiania, techniki ulepszania wzorów po litografii, sterowanie przepływem procesów w aplikacjach wzorcowania SADP i SAQP oraz technologię EUV i litografii zanurzeniowej fotomaski. Yang uzyskał tytuł licencjata z fizyki na Uniwersytecie Kalifornijskim w Los Angeles, tytuł magistra inżynierii materiałowej na Chiba Institute of Technology oraz tytuł doktora. uzyskał stopień naukowy w materiałoznawstwie na Uniwersytecie Tohoku.

- Dystrybucja treści i PR oparta na SEO. Uzyskaj wzmocnienie już dziś.

- Platoblockchain. Web3 Inteligencja Metaverse. Wzmocniona wiedza. Dostęp tutaj.

- Wybijanie przyszłości w Adryenn Ashley. Dostęp tutaj.

- Źródło: https://semiengineering.com/a-deposition-and-etch-technique-to-lower-resistance-of-semiconductor-metal-lines/

- :ma

- :Jest

- ][P

- 1

- 10

- 100

- a

- powyżej

- przyśpieszony

- pomieścić

- dokładnie

- Osiągać

- osiągnięty

- Dodatkowy

- Skorygowana

- Wszystkie kategorie

- Wszystkie Posty

- i

- Angular

- aplikacje

- stosowany

- AR

- SĄ

- AS

- przypuszczalny

- At

- atom

- BE

- Belka

- staje się

- być

- pomiędzy

- Granice

- by

- obliczony

- CAN

- kandydat

- nie może

- pewien

- kanały

- sukcesy firma

- w porównaniu

- porównanie

- kompleks

- stały

- Ograniczenia

- kontrola

- Konwencjonalny

- Miedź

- Koszty:

- Stwórz

- stworzony

- Kryształ

- dane

- spadek

- głęboko

- Stopień

- wykazać

- zależy

- kaucja

- zdeponowany

- życzenia

- rozwijanie

- oprogramowania

- urządzenie

- Transmitowanie

- wyświetlacze

- dystans

- Rozbieżność

- na dół

- podczas

- każdy

- efekt

- ruchomości

- bądź

- inżynier

- Równoważny

- EV

- spodziewany

- ekspertyza

- wykładniczy

- Brak

- Postać

- wypełniać

- mieszkanie

- pływ

- następnie

- W razie zamówieenia projektu

- Nasz formularz

- formacja

- formularze

- Darmowy

- od

- w pełni

- funkcjonować

- Funkcje

- Krata

- Have

- he

- Wysoki

- wysoko

- Dziury

- HTTPS

- pomysł

- zanurzenie

- poprawa

- ulepszenia

- in

- incydent

- włączony

- Przybywający

- włączać

- wzrosła

- Zwiększenia

- wskazać

- Instytut

- integracja

- Interfejs

- odosobniony

- IT

- JEGO

- jpg

- Chłostać

- warstwa

- nioski

- Ograniczenia

- Ograniczony

- Linia

- linie

- długo

- niski

- WYKONUJE

- maska

- Maski

- materiał

- materiały

- Maksymalna szerokość

- zmierzyć

- Pamięć

- metal

- metoda

- Środkowy

- model

- modele

- jeszcze

- Natura

- niezbędny

- potrzebne

- of

- on

- zamówienie

- Inne

- ludzkiej,

- Parallel

- ścieżka

- Wzór

- fizyczny

- Fizycznie

- Fizyka

- plato

- Analiza danych Platona

- PlatoDane

- punkt

- polarny

- Post

- Wiadomości

- zapobiec

- Wcześniejszy

- wygląda tak

- procesów

- przypadkowy

- Odebrane

- Czerwony

- odzwierciedlić

- regiony

- usunąć

- Badania naukowe

- Odporność

- Efekt

- s

- taki sam

- waga

- systemy

- nauka

- Semiconductor

- Shape

- kształcie

- kształty

- Targi

- Widok

- znaczący

- Krzem

- ponieważ

- pojedynczy

- mniejszy

- So

- Tworzenie

- rozpiętość

- Startowy

- Stan

- Ewolucja krok po kroku

- Cel

- Struktura

- Następnie

- Powierzchnia

- stół

- Techniki

- Technologies

- Technologia

- że

- Połączenia

- Te

- trzy

- miniatur

- do

- Tokio

- najwyższy

- tradycyjnie

- przezroczysty

- ucla

- zrozumieć

- uniwersytet

- posługiwać się

- używany

- wykorzystany

- Wartości

- przez

- Wirtualny

- widoczność

- lotny

- Tom

- vs

- który

- Podczas

- będzie

- Drut

- w

- Praca

- pracował

- działa

- Wydajność

- zefirnet