Hvis vi ser på ekspansjonen i halvlederindustrien i løpet av de siste 25 årene, ser bruk av design IP i alle applikasjoner ut til å være en av de viktigste suksessfaktorene, med silisiumteknologi utrolig utvikling med en x100-faktor, fra 250nm i 2018 til 3nm (hvis ikke 2nm) i 2023. Vi ser for oss at overgangen til brikkebasert arkitektur snart vil spille den samme rollen som SoC brikkebasert arkitektur og massiv bruk av design-IP har spilt på 2000-tallet.

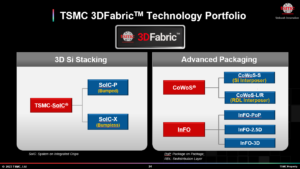

Spørsmålet er hvordan man nøyaktig kan forutsi tidsrammen for adopsjon av chiplet og hva som vil være de viktigste muliggjørerne for denne revolusjonen. Vi vil se om spredning av innovasjonsteori kan være nyttig for å finjustere en prediksjon, bestemme hvilken type applikasjon som vil være driveren. Chip-to-chip interconnect-protokollstandardspesifikasjoner som tillater rask bransjeadopsjon, kjøring av applikasjoner som IA eller smarttelefonapplikasjonsprosessor ser raskt ut til å være den beste muliggjøreren, men EDA-verktøyeffektivitet eller pakking av nye teknologier og dedikert produksjon, blant annet, er absolutt nøkkelen.

Introduksjon: fremveksten av chiplet-teknologi

I løpet av 2010-tiåret begynte fordelene med Moores lov å falle fra hverandre. Moores lov sa at transistortettheten dobles hvert annet år, og kostnadene ved beregning ville krympe med tilsvarende 50%. Endringen i Moores lov skyldes økt designkompleksitet utviklingen av transistorstrukturen fra plane enheter til Finfets. Finfets trenger flere mønstre for litografi for å oppnå enhetsdimensjoner til under 20 nm noder.

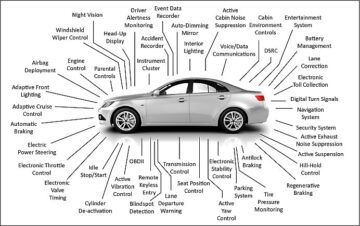

På slutten av dette tiåret har databehandlingsbehovet eksplodert, hovedsakelig på grunn av spredning av datasentre og på grunn av mengden data som genereres og behandles. Faktisk blir bruk av kunstig intelligens (AI) og teknikker som Machine Learning (ML) nå brukt til å behandle stadig økende data og har ført til at servere har økt datakapasiteten betydelig. Servere har lagt til mange flere CPU-kjerner, har integrert større GPU-er brukt utelukkende for ML, ikke lenger brukt til grafikk, og har innebygd tilpassede ASIC AI-akseleratorer eller komplementær, FPGA-basert AI-behandling. Tidlige AI-brikkedesigner ble implementert ved bruk av større monolittiske SoC-er, noen av dem nådde størrelsesgrensen pålagt av trådkorset, omtrent 700 mm2.

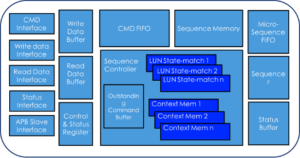

På dette tidspunktet ser oppdeling til en mindre SoC pluss forskjellige data- og IO-brikker ut til å være den rette løsningen. Flere brikkeprodusenter, som Intel, AMD eller Xilinx, har valgt dette alternativet for produkter som skal i produksjon. I den utmerkede hvitboken fra The Linley Group, "Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small", ble det vist at dette alternativet fører til bedre kostnader sammenlignet med monolitiske SoCs, på grunn av avkastningseffekten av større. Disse brikkeprodusentene har designet homogene brikke, men fremveksten og bruken av sammenkoblingsstandarder som Universal Chiplet Interconnect Express (UCIe) IP letter adopsjonen av heterogen brikke.

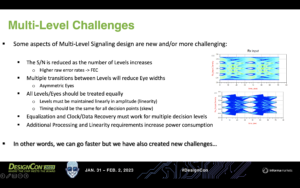

Utviklingen av de nyere, raskere protokollstandardene tar fart ettersom industrien stadig ber om høyere ytelse. Dessverre er de ulike standardene ikke synkronisert av en enkelt organisasjon. Nye PCIe-standarder kan komme ett år (eller mer) tidligere eller senere enn den nye Ethernet-protokollstandarden. Ved å bruke heterogen integrasjon kan silisiumleverandører tilpasse seg det raskt skiftende markedet ved kun å endre utformingen av den relevante brikken. Med tanke på avansert produksjon av SoC-design krever massive kapitalutgifter for 5nm, 4nm eller 3nm prosessnoder, er virkningen av chiplet-arkitekturer enorm for å drive fremtidig innovasjon i halvlederområdet.

Heterogen chiplet-design lar oss målrette mot ulike applikasjoner eller markedssegmenter ved å modifisere eller legge til bare de relevante chiplets mens resten av systemet holdes uendret. Nye utviklinger kan lanseres raskere til markedet, med betydelig lavere investering, da redesign bare vil påvirke pakkesubstratet som brukes til å huse brikkene. For eksempel kan databrikken redesignes fra TSMC 5nm til TSMC 3nm for å integrere større L1-cache eller høyere ytelse CPU eller antall CPU-kjerner, samtidig som resten av systemet holdes uendret. Chiplet-integrerende SerDes kan redesignes for raskere hastigheter på nye prosessnoder som tilbyr mer IO-båndbredde for bedre markedsposisjonering.

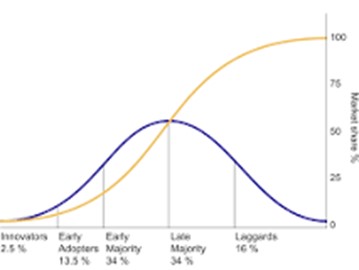

Bruk av heterogen chiplet vil gi bedre Time-to-Market (TTM) ved oppdatering av systemet, gjenbruk av delen av systemet uten endring hvis den er designet i chiplet. Dette vil også være en måte å minimere kostnadene når du holder en funksjonell brikke på mindre avanserte noder, billigere enn de mest avanserte. Men hovedspørsmålet er å forutsi når chiplet-teknologien vil skape et betydelig segment av halvledermarkedet? Vi vil gå gjennom IP-adopsjonshistorien ettersom chiplet og IP er like, begge må bryte NIH-syndromet for å bli vellykket. Vi vil trekke ut hovedårsakene til chipletadopsjon og bygge en prognose, ved å bruke innovasjonsteorien og den definerte kategorien (Innovators, Early Adopters, etc. se figur nedenfor).

Vi vil gjennomgå ARM CPU IP-adopsjon gjennom 1991 til 2018 og IP-adopsjonshistorikk gjennom 1995 til 2027, og sjekke hvordan denne adopsjonsraten holder seg til innovasjonsteorien.

Vi vil forklare hvorfor chiplet-adopsjon vil øke, og vurdere teknologien og markedsføringsrelaterte årsaker:

- Fra IP-basert SoC til chiplet-basert system

- Interoperabilitet, takket være chiplet interconnect foretrukket protokollstandard

- Forklarer hvorfor high-end grensesnitt IP er nøkkelen for brikkeadopsjon

- Designrelaterte utfordringer å løse.

- Sist men ikke minst, investering gjort av støperi

Til slutt kan vi bygge en tentativ prognose for chipletadopsjon, basert på innovasjonsteori. Bare for å nevne, industrien har nettopp beveget seg i "Early adopters"-fasen, og så mange IP- og chipletleverandører som betjener HPC og AI.

Hvis du laster ned hvitt papir, vil du nyte med all teksten og mange bilder, noen av dem er laget eksklusivt for dette arbeidet.

By Erik Esteve (PhD.) Analytiker, eier IPnest

Alphawave sponset opprettelsen av denne hvitboken, men meningene og analysen er forfatterens. Artikkelen finner du her:

https://awavesemi.com/resource/will-chiplet-adoption-to-mimic-ip-adoption/

Les også:

Disaggregerte systemer: Aktiverer databehandling med UCIe Interconnect og Chiplet-basert design

Grensesnitt-IP i 2022: 22 % årlig vekst fortsatt datasentrert

Del dette innlegget via:

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- PlatoData.Network Vertical Generative Ai. Styrk deg selv. Tilgang her.

- PlatoAiStream. Web3 Intelligence. Kunnskap forsterket. Tilgang her.

- PlatoESG. Karbon, CleanTech, Energi, Miljø, Solenergi, Avfallshåndtering. Tilgang her.

- PlatoHelse. Bioteknologisk og klinisk etterretning. Tilgang her.

- kilde: https://semiwiki.com/chiplet/339927-will-chiplet-adoption-mimic-ip-adoption/

- : har

- :er

- :ikke

- $OPP

- 1

- 1995

- 200

- 2018

- 2022

- 2023

- 25

- a

- Om oss

- akseleratorer

- Oppnå

- tilpasse

- la til

- legge

- adoptere

- Adopsjon

- avansert

- AI

- AI-data

- Alle

- tillate

- tillater

- også

- AMD

- blant

- beløp

- analyse

- analytiker

- og

- hverandre

- vises

- Søknad

- søknader

- arkitektur

- ER

- ARM

- Artikkel

- kunstig

- kunstig intelligens

- Kunstig intelligens (AI)

- AS

- ASIC

- spør

- At

- forfatter

- Båndbredde

- basert

- BE

- bli

- begynte

- være

- under

- Fordeler

- Bedre

- Stor

- styrket

- både

- Break

- bygge

- men

- by

- cache

- CAN

- Kapasitet

- hovedstad

- Kategori

- årsaker

- Gjerne

- utfordringer

- endring

- endring

- billigere

- sjekk

- chip

- chips

- Kom

- sammenlignet

- utfyllende

- kompleksitet

- Beregn

- databehandling

- vurderer

- Tilsvarende

- Kostnad

- Kostnader

- kunne

- prosessor

- skape

- opprettet

- skaperverket

- skikk

- dato

- tiår

- dedikert

- definert

- tetthet

- utforming

- designet

- design

- Bestem

- Utvikling

- utviklingen

- Enheter

- forskjellig

- kringkasting

- dimensjoner

- doblet

- nedlasting

- stasjonen

- sjåfør

- kjøring

- to

- under

- Tidligere

- Tidlig

- tidlig adopters

- lettelser

- økosystem

- effektivitet

- innebygd

- veksten

- enabler

- muliggjør

- slutt

- nyte

- etc

- stadig økende

- Hver

- evolusjon

- eksempel

- utmerket

- utelukkende

- utvidelse

- Forklar

- ekspress

- trekke ut

- Faktisk

- faktor

- faktorer

- Fall

- FAST

- raskere

- Figur

- Til

- Varsel

- forutse

- funnet

- FPGA

- fra

- funksjonelle

- framtid

- Gevinst

- generert

- få

- skal

- GPU

- grafikk

- Gruppe

- Vekst

- Ha

- nyttig

- her.

- High-End

- høyere

- historie

- hus

- Hvordan

- Hvordan

- hpc

- HTTPS

- ia

- if

- Påvirkning

- implementert

- pålagt

- in

- økt

- økende

- utrolig

- industri

- Innovasjon

- innovatører

- integrere

- integrert

- Integrering

- integrering

- Intel

- Intelligens

- Interface

- inn

- investering

- IP

- IT

- jpg

- bare

- holde

- nøkkel

- større

- Siste

- seinere

- lansert

- Law

- Fører

- læring

- minst

- Led

- mindre

- i likhet med

- BEGRENSE

- lenger

- Se

- lavere

- maskin

- maskinlæring

- laget

- Hoved

- større

- Makers

- mange

- marked

- Marketing

- massive

- nevner

- minimere

- ML

- Monolithic

- mer

- mest

- for det meste

- flytte

- flyttet

- flere

- Trenger

- behov

- Ny

- Ny teknologi

- nyere

- NIH

- Nei.

- noder

- nå

- Antall

- mange

- of

- tilby

- tilby

- on

- ONE

- bare

- Meninger

- Alternativ

- or

- organisasjon

- andre

- eieren

- pakke

- emballasje

- Papir

- del

- ytelse

- utfører

- fase

- phd

- PHP

- plukking

- Bilder

- plato

- Platon Data Intelligence

- PlatonData

- Spille

- spilt

- i tillegg til

- Point

- posisjonering

- Post

- Slå

- nettopp

- forutsi

- prediksjon

- trekkes

- prosess

- behandlet

- prosessering

- prosessor

- Produksjon

- Produkter

- protokollen

- tilbydere

- spørsmål

- raskere

- raskt

- rask

- Sats

- priser

- nå

- Lese

- grunner

- redesign

- redesignet

- i slekt

- relevant

- påminnelse

- Krever

- REST

- anmeldelse

- gjennomgå

- Revolution

- ikke sant

- Rolle

- samme

- se

- se

- synes

- segmentet

- segmenter

- velg

- halvledere

- servere

- servering

- flere

- vist

- signifikant

- betydelig

- Silicon

- lignende

- enkelt

- Størrelse

- mindre

- smarttelefon

- løsning

- LØSE

- noen

- Snart

- Rom

- spesifikasjoner

- fart

- Sponset

- Standard

- standarder

- uttalte

- Stick

- Still

- struktur

- suksess

- vellykket

- system

- Systemer

- Target

- teknikker

- Technologies

- Teknologi

- tekst

- enn

- Takk

- Det

- De

- deres

- Dem

- teori

- Disse

- denne

- De

- Gjennom

- tidsramme

- til

- verktøy

- topp

- enorm

- tsmc

- to

- typen

- dessverre

- Universell

- oppdatering

- us

- bruke

- brukt

- ved hjelp av

- ulike

- leverandører

- av

- var

- Vei..

- we

- var

- Hva

- når

- mens

- hvit

- hvitt papir

- hvorfor

- vil

- med

- Arbeid

- ville

- år

- år

- Utbytte

- du

- zephyrnet