Siden debuten på 1980-tallet med 10 Mbps delte LAN over koaksialkabler, har Ethernet sett konsekvente fremskritt, nå med potensial til å støtte hastigheter på opptil 1.6 Tbps. Denne progresjonen har gjort det mulig for Ethernet å betjene et bredere spekter av applikasjoner, for eksempel direktestrømming, radiotilgangsnettverk og industriell kontroll, og understreker viktigheten av pålitelig pakkeoverføring og tjenestekvalitet. Med dagens Internett-båndbredde som nynner på ~500 Tbps, er det et økende behov for forbedret back-end-trafikkhåndtering innen datasenteret. Selv om individuelle servere ennå ikke opererer på Terabit-per-sekund-nivåer, nærmer den totale datasentertrafikken seg denne skalaen, noe som får IEEEs 802.3dj-gruppe til å gjennomføre standardiseringsinnsats og krever robuste Ethernet-kontrollere og SerDes for å administrere den ekspanderende dataflyten. Midt i dette bakteppet av eskalerende krav, øker interprosessorkommunikasjonen allerede til disse hastighetene.

Interprosessorkommunikasjon går i spissen for behovet for 1.6T-hastigheter med minimal latenstid. Mens individuelle enheter er begrenset av deres iboende prosesseringskapasitet og brikkestørrelse, kan kombinasjonen av brikker utvide disse kapasitetene betydelig. Den første generasjonen av applikasjoner forventes å bli fulgt av bytte-til-svitsj-forbindelser i datasenteret, noe som muliggjør sammenslåing av høyytelsesprosessorer og minne, noe som øker skalerbarheten og effektiviteten innen cloud computing.

IEEEs 802.3dj-initiativ: Fremme Ethernet-standarder for 1.6 Tbps interoperabilitet

Overholdelse av standardiseringsinnsatsen i utvikling er avgjørende for sømløs økosysteminteroperabilitet. IEEEs 802.3dj-gruppe er i ferd med å formulere den kommende Ethernet-standarden, som omfatter fysiske lag og administrasjonsparametere for hastigheter fra 200G opp til 1.6 terabit per sekund. Gruppens mål er en 1.6 Tbps Ethernet MAC-datahastighet, med sikte på en maksimal bitfeilrate på ikke mer enn 10-13 på MAC-laget. Ytterligere bestemmelser inkluderer valgfrie 16 og 8 lane Attachment Unit Interfaces (AUI) som er egnet for forskjellige brikkeapplikasjoner, og utnytter 112G og 224G SerDes. Fysisk sett innebærer 1.6 Tbps-spesifikasjonen overføring gjennom 8 par kobber twinax-kabler for opptil én meter og 8 par fiber for avstander mellom 500 meter og 2 km. Selv om standardens fullstendige ratifisering er forventet innen våren 2026, er kjernesettet med funksjoner anslått for en fullføring i 2024.

Båndbreddeoverhead og feilretting i et 1.6T Ethernet-undersystem

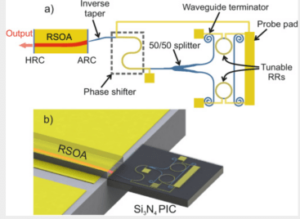

Fig. 1: Diagram som viser komponentene i et 1.6T Ethernet-undersystem.

I tidligere Ethernet-iterasjoner fokuserte PCS først og fremst på datakoding for pålitelig pakkedeteksjon. Men med eskaleringen til 1.6T Ethernet-hastigheter, blir behovet for Forward Error Correction (FEC) tydelig, spesielt for å motvirke signalforringelse over selv korte lenker. For dette formålet fortsetter 1.6T Ethernet å bruke Reed-Solomon FEC. Denne tilnærmingen bygger et kodeord som omfatter 514 10-bits symboler kodet inn i en 544 symbolblokk, noe som resulterer i en båndbredde på 6 %. Disse FEC-kodeordene er fordelt på tvers av de fysiske koblingene til AUI, slik at hver fysisk kobling (8 for 1.6T Ethernet) ikke har et helt kodeord. Denne metoden gir ikke bare ekstra beskyttelse mot feilutbrudd, men muliggjør også parallellisering ved den andre dekoderen, og reduserer dermed ventetiden.

Physical Medium Attachment (PMA), med girkasse og SerDes, bringer Ethernet-signalet til de overførte kanalene. For 1.6T Ethernet involverer dette 8 kanaler som hver kjører med 212 Gbps, noe som utgjør en FEC-overhead på 6 %. Modulasjonsteknikken som brukes er 4-nivå pulsamplitudemodulering (PAM-4), som koder for to databiter for hvert overføringssymbol, og dermed effektivt dobler båndbredden når den settes sammen med den tradisjonelle Non-Return Zero (NRZ) tilnærmingen. Overføringsmekanismen er avhengig av digital-til-analog-konvertering, mens en analog-til-digital-konvertering kombinert med DSP-er på mottakersiden sikrer nøyaktig signalutvinning.

Videre er det viktig å merke seg at Ethernet PCS introduserer en "ytre FEC" som spenner fra ende til ende på en Ethernet-kobling. For å styrke kanaler med lengre rekkevidde, er et ekstra lag med feilkorreksjon for individuelle fysiske linjer i rørledningen, sannsynligvis ved å ta i bruk en hamming-kode FEC. Denne korreksjonen forventes å finne sin primære anvendelse i optiske sender/mottakermoduler der slik korreksjon er avgjørende.

Fig. 2: Diagram som viser ekstra overhead lagt til ved bruk av en sammenkoblet FEC for utvidet rekkevidde.

I eksempelsystemet avbildet i figur 2 er MAC og PCS koblet sammen via en optisk modul og en fiberstrekning. PCS har en bitfeilrate på 10-5 ved den optiske modulkoblingen, pluss feil fra selve den optiske koblingen. Å bruke en eneste RS-FEC ende-til-ende ville ikke være tilstrekkelig for å oppnå 10-13 Ethernet-standard, noe som gjør koblingen upålitelig. Et alternativ ville være en trippel implementering av separat RS FEC på hvert hopp, noe som øker kostnadene og ventetiden betydelig. En mer effektiv løsning er integreringen av en sammenkoblet Hamming Code FEC spesifikt for den optiske lenken, som imøtekommer de typiske tilfeldige feilene til optiske tilkoblinger. Dette indre FEC-laget skaper en ekstra utvidelse av linjehastigheten fra 212 Gbps til 226 Gbps, derfor er det viktig at SerDes kan støtte denne linjehastigheten.

Latensutfordringer i 1.6T Ethernet-systemer

Fig. 3: Latensbane for 1.6T Ethernet-undersystem.

Ulike komponenter bidrar til Ethernet-latens: overføringskøen, overføringsvarighet, middels gjennomløpstid og flere behandlings- og mottakstider. For å visualisere dette, se på figur 3, som viser et omfattende 1.6T Ethernet-undersystem. Mens latens kan påvirkes av reaksjonstiden til fjernapplikasjonen, er denne faktoren ekstern i forhold til Ethernet og derfor ofte ekskludert under latensanalyse. Minimering av ventetid ved Ethernet-grensesnittet krever forståelse av de spesifikke omstendighetene. For eksempel kan latens ikke være en primær bekymring for trunkforbindelser mellom svitsjer på grunn av iboende forsinkelser på tregere klientkoblinger. Avstand spiller også en rolle; større lengder introduserer mer ventetid. Dette betyr selvfølgelig ikke at vi skal overse latens i andre scenarier, å redusere latens er alltid et mål.

Overføringsforsinkelse er iboende knyttet til Ethernet-hastigheten og rammestørrelsen. Nærmere bestemt, for et 1.6T Ethernet-system, krever overføring av en pakke med minimumsstørrelse 0.4ns – i hovedsak én Ethernet-ramme per hake av en 2.5 GHz-klokke. På den annen side tar overføring av en standard ramme i maksimal størrelse 8 ns, og strekker seg til 48 ns for Jumbo-rammer. Det valgte mediet dikterer videre latens. For eksempel har optisk fiber vanligvis en latenstid på 5 ns per meter, mens kobberkabling er marginalt raskere med 4 ns per meter.

Et betydelig segment av den totale ventetiden er forankret i mottakerkontrolleren. RS FEC-dekoderen introduserer iboende latens. For å starte feilretting må systemet motta 4 kodeord, som ved 1.6 Tbps utgjør 12.8 ns. Påfølgende aktiviteter, inkludert feilretting og buffering, forsterker denne ventetiden. Mens FEC-kodeordets lagringsvarighet forblir konsistent, er ventetiden under meldingsmottak betinget av den spesifikke implementeringen. Ikke desto mindre kan ventetiden optimaliseres ved å bruke grundige digitale designstrategier.

I hovedsak er det en iboende, uunngåelig ventetid på grunn av FEC-mekanismen og den fysiske avstanden eller kabellengden. Utover disse faktorene spiller designekspertise en sentral rolle for å minimere Ethernet-kontrollerens latens. Å utnytte en komplett løsning som integrerer og optimerer MAC, PCS og PHY baner vei for den mest effektive implementeringen med lav latens.

Oppsummering

Fig. 4: First-pass silisiumsuksess for Synopsys 224G Ethernet PHY IP i 3nm prosess som viser svært lineære PAM-4 øyne.

1.6 Tbps Ethernet er skreddersydd for de mest båndbreddekrevende og latenssensitive applikasjonene. Med fremveksten av 224G SerDes-teknologi, i forbindelse med fremskritt innen MAC og PCS IP, er omfattende løsninger nå tilgjengelige som kontinuerlig samsvarer med de utviklende 1.6T Ethernet-standardene. I tillegg, på grunn av latensen som er iboende til protokollen og feilrettingsmetodene, må den digitale og analoge IP-designen utformes flittig av ekspertdesignere for å unngå å introdusere unødvendig latens i databanen.

For å oppnå toppytelser for 1.6T SoC-design krever en effektivt optimert arkitektur og omhyggelig designpraksis for hver brikkekomponent. Dette legger vekt på strømsparing og minimerer silisiumfotavtrykket, noe som gjør 1.6T datahastigheter en realitet. Silisiumbevist Synopsys 224G Ethernet PHY IP har satt scenen for 1.6T MAC og PCS-kontrolleren. Ved å bruke ledende design-, analyse-, simulerings- og måleteknikker, fortsetter Synopsys å levere eksepsjonell signalintegritet og jitter-ytelse, med en komplett Ethernet-løsning inkludert MAC+PCS+PHY.

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- PlatoData.Network Vertical Generative Ai. Styrk deg selv. Tilgang her.

- PlatoAiStream. Web3 Intelligence. Kunnskap forsterket. Tilgang her.

- PlatoESG. Karbon, CleanTech, Energi, Miljø, Solenergi, Avfallshåndtering. Tilgang her.

- PlatoHelse. Bioteknologisk og klinisk etterretning. Tilgang her.

- kilde: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- : har

- :er

- :ikke

- :hvor

- $OPP

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- adgang

- tilgjengelig

- Regnskap og administrasjon

- nøyaktig

- Oppnå

- tvers

- Aktiviteter

- la til

- Ytterligere

- I tillegg

- vedta

- fremskritt

- Advancing

- mot

- Sikter

- tillatt

- allerede

- også

- Selv

- alltid

- blant

- beløp

- forsterke

- an

- analyse

- og

- forventet

- Søknad

- søknader

- tilnærming

- arkitektur

- ER

- AS

- At

- unngå

- Back-end

- bakteppe

- Båndbredde

- BE

- blir

- mellom

- Beyond

- Bit

- Blokker

- styrke

- øke

- Bringer

- bygger

- men

- by

- kabel

- kabler

- CAN

- kapasiteter

- bære

- utfordringer

- kanaler

- chip

- chips

- valgt ut

- omstendigheter

- kunde

- klokke

- Cloud

- cloud computing

- kode

- kombinert

- kombinere

- Kommunikasjon

- fullføre

- ferdigstillelse

- komponent

- komponenter

- omfattende

- omfattende

- databehandling

- Bekymring

- sammen

- tilkoblet

- Tilkoblinger

- BEVARING

- Vurder

- betraktninger

- konsistent

- fortsetter

- kontinuerlig

- bidra

- kontroll

- controller

- Konvertering

- Kobber

- Kjerne

- Kostnader

- motvirke

- kurs

- utformet

- skaper

- Gjeldende

- dato

- Datacenter

- debut

- forsinkelser

- leverer

- Etterspørsel

- krevende

- krav

- avbilder

- utforming

- designere

- design

- Gjenkjenning

- Enheter

- dikterer

- forskjellig

- digitalt

- flittig

- skjermer

- avstand

- distribueres

- ikke

- dobling

- to

- varighet

- under

- hver enkelt

- Tidligere

- økosystem

- Effektiv

- effektivt

- effektivitet

- effektiv

- effektivt

- innsats

- veksten

- legger vekt på

- streker

- ansatt

- ansette

- muliggjør

- muliggjør

- Omfatter

- slutt

- ende til ende

- sikrer

- Hele

- feil

- feil

- eskalering

- essens

- avgjørende

- hovedsak

- Eter (ETH)

- Selv

- Hver

- tydelig

- utvikling

- eksempel

- eksepsjonell

- ekskludert

- ekspanderende

- utvidelse

- forventet

- Expert

- ekspertise

- utvide

- strekker

- utvendig

- utdrag

- øyne

- faktor

- faktorer

- langt

- raskere

- Egenskaper

- Featuring

- Figur

- Finn

- Først

- Første generasjon

- flyten

- fokuserte

- fulgt

- Fotspor

- Til

- formulering

- Forward

- RAMME

- fra

- videre

- generasjonen

- gir

- større

- Gruppe

- Gruppens

- Økende

- hånd

- Håndtering

- Høy

- høy ytelse

- svært

- Men

- HTML

- HTTPS

- avgjørende

- gjennomføring

- betydning

- viktig

- forbedret

- in

- I andre

- inkludere

- Inkludert

- økende

- individuelt

- industriell

- påvirket

- iboende

- iboende

- initiere

- Initiative

- f.eks

- Integrerer

- integrering

- integritet

- Interface

- grensesnitt

- Internet

- Interoperabilitet

- inn

- egenverdi

- introdusere

- Introduserer

- innføre

- innebærer

- IP

- IT

- gjentakelser

- DET ER

- selv

- jpg

- Lane

- Ventetid

- lag

- lag

- Lengde

- nivåer

- utnytte

- Sannsynlig

- linje

- linjer

- LINK

- lenker

- leve

- lenger

- Lav

- mac

- Making

- administrer

- ledelse

- max bredde

- maksimal

- Kan..

- bety

- måling

- mekanisme

- medium

- Minne

- melding

- metode

- metoder

- grundig

- minimal

- minimere

- minimerer

- minimere

- moduler

- Moduler

- mer

- mest

- må

- nærmer seg

- Trenger

- nettverk

- likevel

- Nei.

- note

- nå

- Målet

- of

- ofte

- on

- ONE

- bare

- drift

- optimalisert

- Optimaliserer

- Alternativ

- or

- Annen

- enn

- samlet

- par

- parametere

- spesielt

- banen

- PC-er

- for

- ytelse

- forestillinger

- fysisk

- fysisk

- rørledning

- sentral

- plato

- Platon Data Intelligence

- PlatonData

- spiller

- i tillegg til

- potensiell

- makt

- praksis

- primært

- primære

- prosess

- prosessering

- prosessorer

- progresjon

- anslått

- beskyttelse

- protokollen

- puls

- formål

- Skyver

- kvalitet

- radio

- tilfeldig

- område

- Sats

- priser

- å nå

- nå

- reaksjon

- Reality

- motta

- mottak

- mottak

- redusere

- pålitelig

- forblir

- gjengivelse

- Krever

- begrenset

- resulterende

- robust

- Rolle

- forankret

- rennende

- skalerbarhet

- Skala

- scenarier

- sømløs

- Sekund

- sett

- segmentet

- sensitive

- separat

- betjene

- tjeneste

- sett

- flere

- delt

- Kort

- bør

- utstillingsvindu

- Signal

- betydelig

- Silicon

- simulering

- Størrelse

- So

- løsning

- Solutions

- spenn

- spydspiss

- spesifikk

- spesielt

- spesifikasjon

- hastigheter

- vår

- Scene

- Standard

- standardisering

- standarder

- lagring

- strategier

- streaming

- senere

- betydelig

- suksess

- slik

- egnet

- støtte

- symbol

- system

- skreddersydd

- tar

- teknikk

- teknikker

- Teknologi

- enn

- Det

- De

- deres

- Der.

- derved

- derfor

- Disse

- denne

- Gjennom

- Dermed

- tick

- Tied

- tid

- ganger

- til

- topp

- tradisjonelle

- trafikk

- overføre

- overføre

- Triple

- to

- typisk

- typisk

- uunngåelig

- forståelse

- påta

- enhet

- kommende

- upon

- ved hjelp av

- bruke

- av

- visualisere

- Vei..

- we

- når

- hvilken

- mens

- bredere

- med

- innenfor

- ville

- ennå

- zephyrnet

- null