Blandet signalmodellering blir viktigere ettersom interaksjonen mellom digitale og analoge kretser blir tettere sammenvevd. Dette nivået av modellering avhenger kritisk av tilstrekkelig nøyaktige, men raske atferdsmodeller for analoge komponenter. Paul Cunningham (Senior VP/GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, gründer, tidligere Synopsys CTO og nå Silvaco CTO) og jeg fortsetter vår serie om forskningsideer. Som alltid, tilbakemeldinger velkommen.

Innovasjonen

Denne månedens valg er Rask validering av SoC-er med blandede signaler. Oppgaven ble presentert i 2021 Journal of the Solid-State Circuits Society. Forfatterne er fra Stanford, Seoul National University og Scientific Analog.

En nylig SemiWiki-blogg om blandet signal fanget enorm interesse, noe som tyder på at dette er et område som er verdt å studere videre. Et kritisk skritt for å realisere effektiv blandet signalverifisering er å utvikle nøyaktige atferdsmodeller på blandet nivå for analoge funksjoner som er egnet for hendelsesdrevet simulering, og til og med syntetiserbare modeller for distribusjon i maskinvareemulering. Oppgaven beskriver en malbasert tilnærming til å generere modeller og to metoder for å interpolere analog oppførsel til hendelsesbaserte forbindelser: oversampling og hendelsesdrevet modellering med funksjonsvektorer (reelle tallmodeller).

Forfatterne demonstrerer anvendelse på en høyhastighets lenkesimulering og -emulering med imponerende resultater. Sammenligning mellom Spice- og Verilog-simulering på ADC viser nær samsvar i resultater, og kjører størrelsesordener raskere. Emuleringsbasert modellering legger til enda flere størrelsesordener til den hastigheten.

Paulus syn

Stor kontekst-bytte denne måneden inn i verden av analog verifisering og dens "blandet signal"-kryss med digital verifisering. Denne artikkelen er en invitert artikkel i et prestisjefylt tidsskrift som vakkert oppsummerer state-of-the-art for å bygge abstrakte modeller av analoge kretser som kan holde tritt med digital simulering, selv på en emulator, og gjøre det med utrolig god nøyaktighet.

I den analoge verden er alt jevnt og vanligvis oscillerende, med tiltenkt input-output-oppførsel ofte beskrevet ved først å transformere input/output-bølgeformer til frekvensdomenet. Gullstandarden for analog simulering er Spice, som iterativt løser differensialligninger på enhetsnivå for spenninger på alle punkter i en krets innenfor garanterte feiltoleranser. Sammenlignet med digital simulering er Spice tusenvis av ganger tregere.

Den typiske tilnærmingen til å lage raske abstrakte analoge modeller er å gjøre diskret tidssampling av inngangsbølgeformen og deretter generere den passende diskrete tidssamplede utgangsbølgeformen ved å bruke noen DSP-lignende logikk (f.eks. diskrete-tidsfiltre). Signalverdier mellom disse diskrete tidspunktene kan genereres om nødvendig ved bruk av lineær eller splinebasert interpolasjon.

Forfatterne presenterer et komplett åpen kildekode-rammeverk med et elegant modellgenereringsspråk og kompilator for å generere både simulerbare og emulerbare modeller fra dette språket. De bruker en adaptiv tidstrinnsprøvemetode med splinebasert interpolering og arbeider gjennom en troverdig casestudie ved å bruke rammeverket deres på en 16nm høyhastighets SERDES-link PHY. Å gå fra Spice til digital CPU-basert simulering med deres abstraherte modeller oppnår en hastighet på 13,000 300 ganger. Å sette modellene på en FPGA ga ytterligere XNUMXx hastighet. Hyggelig.

Raúl syn

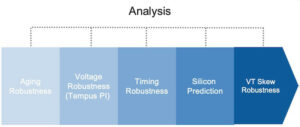

Valideringen av SoC-er med blandede signaler er en utfordring, blant annet fordi å kjøre tilstrekkelig med testvektorer for å validere de digitale delene – typisk med en hendelsesdrevet simulator eller på en emulator – resulterer i uoverkommelige tider for å simulere den analoge delen med en kretssimulator. En løsning er å lage analoge atferdsmodeller. Denne månedens artikkel gjennomgår flere tilnærminger for å lage disse modellene og presenterer det forfatterne mener er det første komplette rammeverket med åpen kildekode for AMS-emulering. Dette er en invitert artikkel til IEEE open journal of the Solid-State Circuits Society, og som sådan leses store passasjer som en veiledning om analog design og validering. Det er ganske annerledes enn det vi har gjort før i denne bloggen; leseren trenger litt analog kunnskap for å kunne dra full nytte (f.eks. Laplace-domene, z-transform, PLL, faseinterpolator, Nyquist-hastigheter, jitter, etc.).

Funksjonelle modeller av analoge kretser mottar innganger og genererer utganger på diskrete tidspunkter. Bølgeformer kan modelleres ved å bruke stykkevis konstante eller stykkevis lineære funksjoner, ved å bruke splinepunkter (tilnærmingen som brukes i denne artikkelen) eller summer av komplekse eksponentielle funksjoner. Tid er modellert som diskret tid (samplet eller oversamplet) eller som stykkevis lineær modellering (brukt her). De faktiske modellene av kretser er satt sammen fra et bibliotek med maler. Forfatterne setter alt dette sammen i et system bestående av: 1) Et Python-verktøy for å generere syntetiserbare AMS-modeller som gir et sett med funksjoner som lar brukere beskrive AMS-blokker som differensialligninger, nettlister, overføringsfunksjoner eller svitsjede systemer, … i enten fast eller flytende punkt, og 2) En simulatorlignende abstraksjon av FPGA-kort.. som gir emuleringsinfrastruktur som administrerer emuleringstidstrinnet, emuleringsklokkehastigheten og testgrensesnitt og genererer FPGA-emuleringsbitstrømmen ved hjelp av EDA-verktøy.

Trikset er ikke å bruke kretssimulering, men heller å erstatte kretsmodeller med funksjonelle modeller. For en høyhastighetslink-mottaker kalt DragonPHY er hastigheten til en Verilog versus en Spice-simulering 12,800 100,000x, noe som gir tilstrekkelig nøyaktighet. Men selv denne hastigheten er ikke nok til å simulere klokkegjenoppretting og kanalutjevningsløkker, for å teste bitfeilfrekvenser (BER), med tilbakemeldingsløkker som kan ta 5000 7.5-vis av sykluser å avgjøre. Å modifisere modellene slik at de er syntetiserbare og kan inkorporeres i emulering gir ytterligere XNUMXx hastighetsøkning, tilstrekkelig til å beregne BER innen XNUMX %. Imponerende!

Les også:

Påstandssyntese gjennom LLM. Innovasjon i verifikasjon

Cadence Tensilica Spins neste oppgradering til LX Architecture

Inferenseffektivitet i ytelse, kraft, areal, skalerbarhet

Del dette innlegget via:

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- PlatoData.Network Vertical Generative Ai. Styrk deg selv. Tilgang her.

- PlatoAiStream. Web3 Intelligence. Kunnskap forsterket. Tilgang her.

- PlatoESG. Karbon, CleanTech, Energi, Miljø, Solenergi, Avfallshåndtering. Tilgang her.

- PlatoHelse. Bioteknologisk og klinisk etterretning. Tilgang her.

- kilde: https://semiwiki.com/eda/336610-developing-effective-mixed-signal-models-innovation-in-verification/

- :er

- :ikke

- $OPP

- 1

- 100

- 12

- 13

- 2021

- 300

- 7

- a

- I stand

- ABSTRACT

- abstraksjon

- nøyaktighet

- nøyaktig

- oppnår

- faktiske

- adaptive

- Legger

- Alle

- tillater

- alltid

- blant

- an

- og

- En annen

- Søknad

- tilnærming

- tilnærminger

- hensiktsmessig

- ER

- AREA

- AS

- montert

- At

- forfattere

- BE

- vakkert

- fordi

- bli

- bli

- før du

- atferd

- tro

- nytte

- mellom

- Bit

- Blocks

- Blogg

- både

- bygge

- men

- by

- Cadence

- som heter

- CAN

- fanget

- saken

- case study

- Catalyst

- utfordre

- Kanal

- klokke

- Lukke

- tett

- sammenlignet

- sammenligning

- fullføre

- komplekse

- komponenter

- Beregn

- Tilkoblinger

- Består

- konstant

- fortsette

- skape

- Opprette

- skaperverket

- troverdig

- kritisk

- CTO

- sykluser

- demonstrere

- avhenger

- distribusjon

- beskrive

- beskrevet

- utforming

- utvikle

- utvikle

- forskjellig

- digitalt

- do

- domene

- gjort

- drevet

- e

- Effektiv

- effektivitet

- enten

- enorm

- nok

- Gründer

- ligninger

- feil

- etc

- Selv

- Event

- alt

- eksponentiell

- FAST

- raskere

- Trekk

- tilbakemelding

- filtre

- Først

- fikset

- flytende

- Til

- Tidligere

- FPGA

- Rammeverk

- Frekvens

- fra

- fullt

- funksjonelle

- funksjoner

- videre

- ga

- generere

- generert

- genererer

- genererer

- generasjonen

- skal

- Gull

- Gold Standard

- god

- garantert

- maskinvare

- Ha

- hjelpe

- her.

- Høy

- HTTPS

- i

- Ideer

- IEEE

- if

- viktig

- imponerende

- in

- Incorporated

- Infrastruktur

- Innovasjon

- inngang

- innganger

- tiltenkt

- interaksjon

- interesse

- grensesnitt

- kryss

- sammenflettet

- inn

- invitert

- IT

- DET ER

- journal

- Hold

- Språk

- stor

- Nivå

- Bibliotek

- i likhet med

- LINK

- logikk

- forvalter

- max bredde

- Kan..

- metode

- metoder

- blandet

- modell

- modellering

- modeller

- Måned

- mer

- nasjonal

- nødvendig

- behov

- Ny

- neste

- fint

- nå

- Antall

- of

- ofte

- on

- åpen

- åpen kildekode

- or

- ordrer

- Annen

- vår

- produksjon

- utganger

- Papir

- del

- deler

- paul

- ytelse

- fase

- plukke

- plato

- Platon Data Intelligence

- PlatonData

- Point

- poeng

- Post

- makt

- presentere

- presentert

- gaver

- prestisjetunge

- gir

- gi

- sette

- Sette

- Python

- ganske

- priser

- heller

- Lese

- Reader

- ekte

- realisere

- motta

- nylig

- utvinning

- forskning

- Resultater

- Anmeldelser

- rennende

- vitenskapelig

- senior

- Seoul

- Serien

- sett

- bosette

- flere

- Viser

- Signal

- Silicon

- simulering

- simulator

- glatter

- So

- Samfunnet

- løsning

- løse

- noen

- fart

- krydder

- spins

- Standard

- stanford

- state-of-the-art

- Trinn

- Studer

- slik

- tilstrekkelig

- egnet

- summer

- byttet om

- syntese

- system

- Systemer

- Ta

- maler

- test

- Det

- De

- verden

- deres

- deretter

- Disse

- de

- ting

- denne

- tusener

- Gjennom

- tid

- ganger

- til

- sammen

- verktøy

- verktøy

- overføre

- transformere

- tutorial

- to

- typisk

- typisk

- universitet

- oppgradering

- bruke

- brukt

- Brukere

- ved hjelp av

- vanligvis

- VALIDERE

- validering

- Verdier

- Verifisering

- Versus

- av

- var

- we

- velkommen

- Hva

- hvilken

- med

- innenfor

- Arbeid

- verden

- verdt

- ennå

- zephyrnet