Å forhindre spredning av systematiske defekter i dagens halvlederdesign-til-fabrikasjonsprosess krever mange validerings-, analyse- og optimaliseringstrinn. Verktøy som er involvert i denne prosessen kan inkludere designregelkontroll (DRC), verifikasjon av optisk nærhetskorreksjon (OPC), maskeskriving og wafer-utskriftsmetrologi/inspeksjon (for å måle prosessen), waferutskriftsmetrologi/inspeksjon og fysisk feilanalyse for å bekrefte feil diagnose. Utveksling av informasjon og co-optimalisering mellom disse trinnene er en kompleks prosess, med mange feed-forward og feedback loops. Kommunikasjon hemmes ofte av "vegger" mellom ulike deler av prosessteknologien, noe som bremser innovasjonen. På den nylige SPIE-konferansen presenterte Siemens EDA en hovedtale som foreslo en rekke tilnærminger for å bryte ned disse veggene for å forbedre brikkedesignet til produksjonsprosessen. Les videre for å se hvordan Siemens har som mål å bryte ned innovasjonsbarrierer ved å utvide samoptimalisering av designteknologi.

Om Keynote

SPIE er det internasjonale samfunnet for optikk og fotonikk. Organisasjonen dateres tilbake til 1955, og konferansen har blitt en ledende begivenhet for avanserte design- og produksjonsemner. På årets arrangement presenterte Siemens keynoten som er temaet for dette innlegget. Det var mange bidragsytere til presentasjonen, inkludert Le Hong, Fan Jiang, Yuansheng Ma, Srividya Jayaram, Joe Kwan, Siemens EDA (USA); Doohwan Kwak, Siemens EDA (Republikken Korea); Sankaranarayanan Paninjath Ayyappan, Siemens EDA (India). Tittelen på foredraget var Utvidelse av samoptimalisering av designteknologi fra teknologilansering til HVM.

Foredraget var en del av en økt om designteknologi co-optimalisering (DTCO). Dette konseptet er ikke nytt, men Siemens så på applikasjonen på tvers av et bredere spekter av prosessen, fra design til høyvolumproduksjon (HVM). Ideene og resultatene som presenteres har betydelige implikasjoner. La oss ta en nærmere titt.

Hva ble presentert

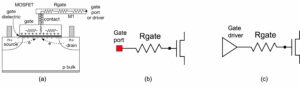

Først ble en titt på den nåværende tilstanden til DTCO-bruk på tvers av sentrale deler av økosystemet presentert. Fra et designperspektiv har mange avanserte fabelløse selskaper et DFM-team som ser grensene for en mønsterbasert tilnærming. Det som virkelig trengs er ny teknologi for å lette utbyttelæring uten støperiavhengighet.

Støperiene bruker brute-force mønsterbaserte maskinlæringsmetoder, som er kostbare, men ikke helt effektive. De søker også effektiv informasjonsutvinning av de enorme produksjonsdataene de lager. Utstyrsleverandører og EDA-leverandører har jobbet tettere sammen og kommer opp med mer effektive maskinlæringsløsninger.

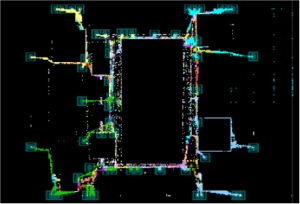

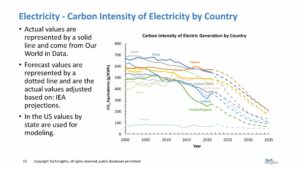

Ved å gå litt tilbake ble det påpekt at det er vegger mellom design- og produksjonsfasene i prosessen. Fabless-selskaper lager designet, utfører DRC og design for manufacturing (DFM), så kaster de det over veggen til OPC/RET-teamet i støperiet eller IDM. Designet får utført oppgaver som OPC og verifisering, og deretter kastes dataene over en annen vegg for maskeskriving og metrologi/inspeksjon. Den siste veggen er for fabrikasjon. Her vil det bli gjort elektrisk test og feilanalyse. Innen en grunnleggende årsak til feilen er funnet, har det gått 6-18 måneder. Det er en veldig lang tilbakemeldingssløyfe. Grafikken øverst i dette innlegget viser denne prosessen.

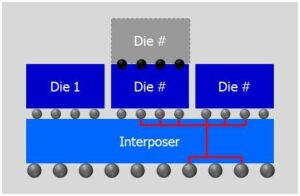

DTCO forsøker å bryte ned veggene, men de tilgjengelige metodikkene er ufullstendige. Tradisjonell DTCO starter veldig tidlig i prosessutvikling. Med utgangspunkt i et skaleringsbehov defineres en standardcelle, og syntese, sted og rute utføres for å komme opp med grunnleggende mønstre og måle ytelsen og kraften. SRAM-utbytte gjøres også, og at data går tilbake til standard celledesign.

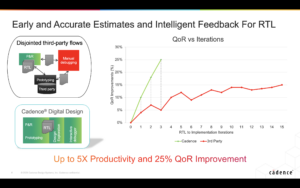

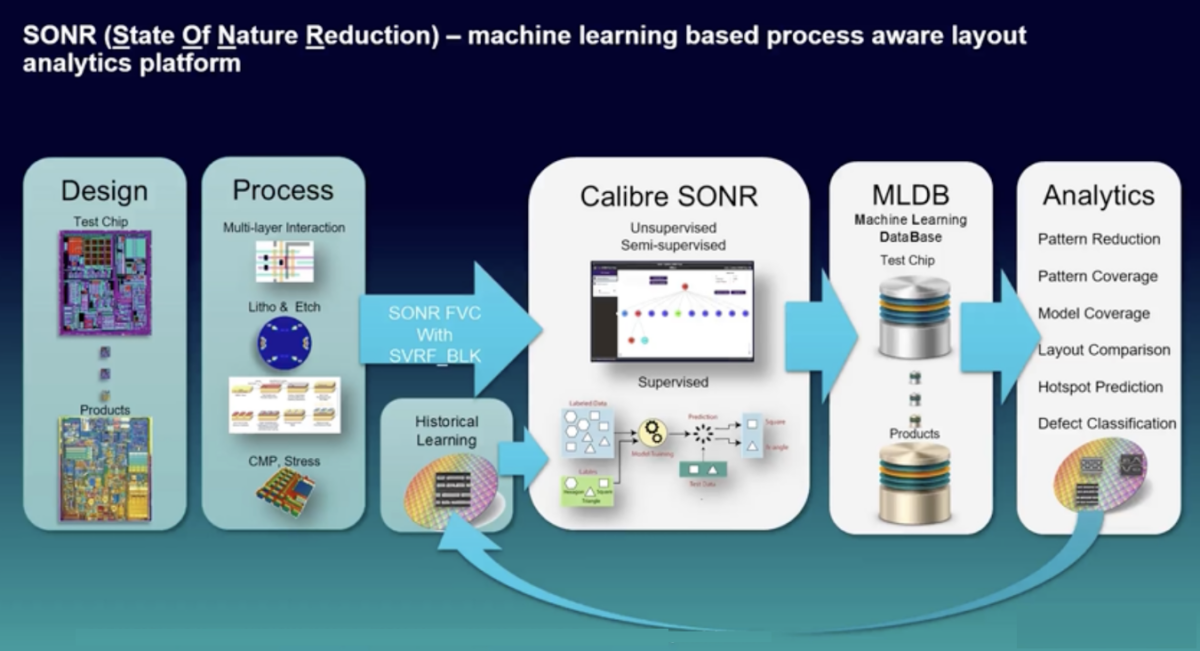

Det som ble presentert på SPIE-keynoten var en måte å utvide dette samoptimeringskonseptet til hele prosessen fra design til produksjon. Tilnærmingen innebærer å muliggjøre en enklere informasjonsflyt fra design hele veien til sluttprosessen og fysisk analyse ved å lage en informasjonskanal.

Selv om dette høres enkelt ut, er det ikke det. Mange utfordringer ble diskutert med konkrete tilnærminger for å dempe problemene. For eksempel kan tidlige design lages med syntetiske layoutgeneratorer for å hjelpe til med å kalibrere prosessen til reelle designproblemer etter hvert som prosessen utvikles. Dette kan lindre mange av overraskelsene som for tiden står overfor med tidlig prosess tapeouts.

Å håndtere enorme datamengder er en annen utfordring. Ved å bruke nye sofistikerte kompresjonsteknikker er en 30X forbedring mulig. Dette forbedrer datahåndteringen og analyseoppgavene ganske mye. Et konsept som heter forklarbar AI kan bidra til å finne de grunnleggende årsakene til problemer mye raskere. Evnen til å trene AI-modeller på nytt senere i produksjonsprosessen uten å ugyldiggjøre tidligere resultater er et annet område for forbedring. Også i dataanalyseområdet er teknikker for å håndtere "ubalanserte data". For eksempel kan det være ett hot spot funnet i 100,000,000 XNUMX XNUMX mønstre.

Å sette alt dette sammen kan skape en mye mer effektiv ende-til-ende designflyt, som vist i figuren nedenfor.

Å lære mer

Virkningen av tilnærmingene som er skissert i denne hovedpresentasjonen er betydelig. Du kan se presentasjonen og få tilgang til en hvitbok om prosessen her. Det er mye nyttig informasjon å hente. Og det er slik Siemens har som mål å bryte ned innovasjonsbarrierer ved å utvide samoptimering av designteknologi.

Del dette innlegget via:

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- PlatoData.Network Vertical Generative Ai. Styrk deg selv. Tilgang her.

- PlatoAiStream. Web3 Intelligence. Kunnskap forsterket. Tilgang her.

- PlatoESG. Karbon, CleanTech, Energi, Miljø, Solenergi, Avfallshåndtering. Tilgang her.

- PlatoHelse. Bioteknologisk og klinisk etterretning. Tilgang her.

- kilde: https://semiwiki.com/events/339386-spie-2023-buzz-siemens-aims-to-break-down-innovation-barriers-by-extending-design-technology-co-optimization/

- : har

- :er

- :ikke

- $OPP

- 000

- 100

- 2023

- a

- evne

- adgang

- tvers

- adresse

- avansert

- AI

- AI-modeller

- mål

- Alle

- lindre

- også

- an

- analyse

- og

- En annen

- Søknad

- tilnærming

- tilnærminger

- ER

- AREA

- AS

- At

- forsøk

- tilgjengelig

- tilbake

- barrierer

- grunnleggende

- BE

- bli

- vært

- under

- mellom

- Bit

- Break

- bredere

- men

- by

- som heter

- CAN

- Årsak

- årsaker

- celle

- utfordre

- utfordringer

- Kanal

- kontroll

- chip

- nærmere

- CO

- Kom

- kommer

- Kommunikasjon

- Selskaper

- helt

- komplekse

- konsept

- betong

- Konferanse

- Bekrefte

- bidragsytere

- kostbar

- skape

- opprettet

- Opprette

- Gjeldende

- Nåværende situasjon

- I dag

- dato

- dataanalyse

- datoer

- avtale

- definert

- avhengighet

- utforming

- design

- detaljer

- utviklet

- Utvikling

- diagnose

- diskutert

- gjort

- ned

- DRC

- Tidligere

- Tidlig

- enklere

- økosystem

- Effektiv

- effektiv

- muliggjør

- ende til ende

- Hele

- utstyr

- Event

- eksempel

- utveksling

- utvide

- strekker

- møtt

- legge til rette

- Failure

- vifte

- raskere

- tilbakemelding

- Figur

- slutt~~POS=TRUNC

- Finn

- flyten

- Til

- funnet

- Støperi

- fra

- fikk

- måler

- generatorer

- grafisk

- Håndtering

- Ha

- hjelpe

- her.

- Hong

- HOT

- Hvordan

- HTTPS

- Ideer

- Påvirkning

- implikasjoner

- forbedre

- forbedring

- forbedrer

- in

- inkludere

- Inkludert

- india

- informasjon

- Innovasjon

- internasjonalt

- involvert

- innebærer

- saker

- IT

- DET ER

- joe

- nøkkel

- Keynote

- korea

- seinere

- lansere

- Layout

- LÆRE

- læring

- grenser

- Lang

- Se

- så

- Lot

- maskin

- maskinlæring

- produksjon

- mange

- maske

- massive

- max bredde

- Kan..

- måle

- metoder

- Gruvedrift

- Minske

- modeller

- måneder

- mer

- mer effektivt

- mye

- Trenger

- nødvendig

- Ny

- of

- ofte

- on

- ONE

- optikk

- Optikk og fotonikk

- optimalisering

- or

- organisasjon

- ut

- skissert

- enn

- Papir

- del

- deler

- bestått

- mønstre

- utføre

- ytelse

- utført

- perspektiv

- fysisk

- Sted

- plattform

- plato

- Platon Data Intelligence

- PlatonData

- mulig

- Post

- makt

- premier

- presentasjon

- presentert

- utskrift

- problemer

- prosess

- forplantning

- foreslått

- ganske

- Lese

- ekte

- virkelig

- nylig

- Republic

- Krever

- Resultater

- root

- Rute

- Regel

- skalering

- omfang

- se

- se

- søker

- halvledere

- Serien

- Session

- vist

- Siemens

- signifikant

- bremse

- Samfunnet

- Solutions

- sofistikert

- Spot

- Standard

- Start

- starter

- Tilstand

- Stater

- Steps

- betydelig

- slik

- overraskelser

- syntese

- syntetisk

- Ta

- Snakk

- oppgaver

- lag

- teknikker

- Teknologi

- test

- Det

- De

- deretter

- Der.

- Disse

- de

- denne

- tid

- Tittel

- til

- dagens

- sammen

- verktøy

- topp

- Tema

- temaer

- slenge

- kastet

- tradisjonelle

- forent

- Forente Stater

- bruk

- nyttig informasjon

- ved hjelp av

- validering

- ulike

- leverandører

- Verifisering

- veldig

- av

- volumer

- Wall

- var

- Vei..

- var

- Hva

- Hva er

- hvilken

- hvit

- hvitt papir

- vil

- med

- innenfor

- uten

- arbeid

- skriving

- Utbytte

- givende

- du

- zephyrnet