Designere har mange veier for å differensiere RISC-V-løsninger. Én bane starter inn i ulike RISC-V-kjernetilpasninger og utvidelser i henhold til spesifikasjonen. En annen fokuserer på å velge og sette sammen IP-blokker i en komplett system-on-chip (SoC) design rundt en eller flere RISC-V-kjerner. En tredje dukker opp: sammenkobling av RISC-V-kjerner og andre IP-blokker med en nettverk-på-brikke (NoC) i stedet for en enkel bussstruktur. Og det er ikke bare i den høye enden – sammenkobling av RISC-V-kjerner med NoCs svarer på mange SoC-designutfordringer der data må flyte effektivt i enhver arbeidsbelastning ved å bruke en hvilken som helst on-chip-protokoll.

Ytelsesnivåene endres med avanserte sammenkoblingsordninger

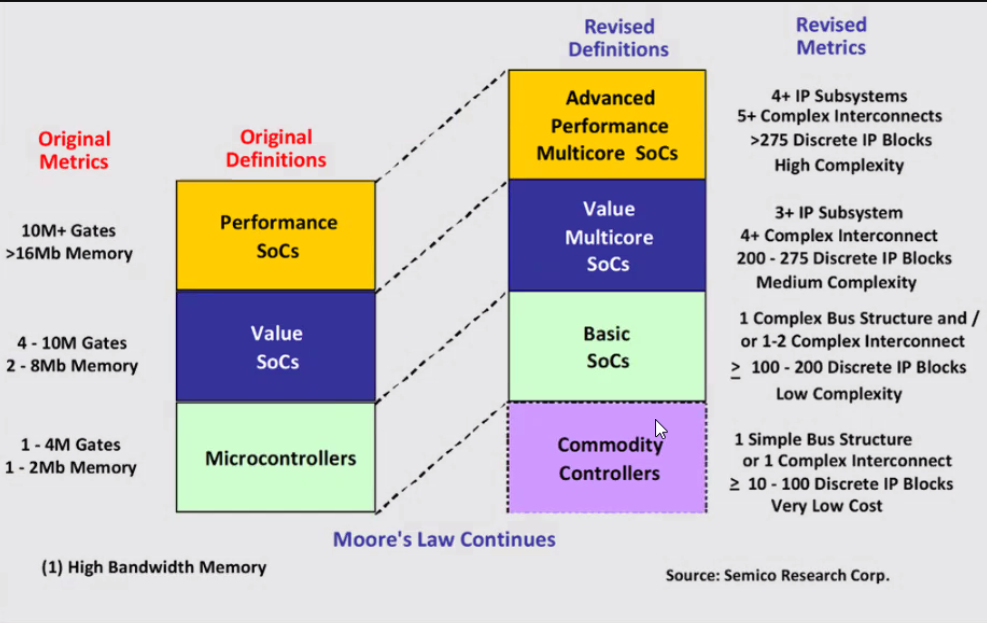

Bare å telle porter, kjerner og perifere blokker beskriver ikke lenger ytelsespotensialet til en SoC-design. Sammenkoblingsordninger definerer nå linjene mellom SoC ytelsesnivåer, ifølge Semico Research, og et nytt nivå har åpnet der sammenkoblinger endres fra enkle bussstrukturer til mer sofistikerte ordninger.

Semicos oppdaterte definisjon gjenkjenner tre krefter som virker: utbredelsen av flerkjernedesign, en høyere bar for det som anses som en kompleks design, og den påfølgende uskarpe linjen mellom "mikrokontroller" og "SoC." I Semicos siste syn forsvinner ideen om port som en metrikk siden en moderne prosessorkjerne kan dra mange porter med seg. Kompleksitet blir en funksjon av sammenkoblinger, som varierer med undersystemer og forskjellige IP-blokker.

SoC ytelsesnivåer, bilde med tillatelse fra Semico Research Corp.

Der en enkel buss vil gjøre det, sannsynligvis en del med en enkelt prosessorkjerne og periferiutstyr med lav driftssyklus som ikke kontinuerlig kjemper om bussen, ser Semico et varekontrollnivå. Alt over det blir en SoC, antagelig med minst noen periferiutstyr som kjemper om båndbredde på brikken og oppmerksomhet fra prosessorkjernen(e). Høyere SoC-nivåer har flere kjerner og flere IP-undersystemer, hver med innstilt sammenkoblingsteknologi.

NoC-er plukker opp flere protokoller og undersystemer

RISC-V har raskt flyttet opp disse ytelsesnivåene etter hvert som kraftigere kjerner dukker opp, med ikke mindre anvendelighet i den nedre enden av Semico-skalaen. Imidlertid kan RISC-V-designere ha mindre erfaring med komplekse sammenkoblingsordninger sett i de høyere nivåene. "TileLink kan være den første tanken for RISC-V-sammenkobling, men det kan være vanskelig å bruke i mer komplekse scenarier," sier Frank Schirrmeister, VP for løsninger og forretningsutvikling for Arteris.

En NoCs superkraft er dens evne til å koble sammen undersystemer ved hjelp av forskjellige protokoller, og SoC-designere vil sannsynligvis støte på flere protokoller med til og med moderat kompleksitet. AXI utjevnet konkurransevilkårene for enkle IP-blokkforbindelser. Flerkjerneløsninger med sambehandlingsblokker krever cache-koherens, noe som gir opphav til CHI-protokollen. I/O-minnedeling bidro til å forme den raskere CXL-sammenkoblingen. "Når det er på tide å samoptimalisere databehandling og transport med ulike undersystemer og protokoller i spill, er en NoC en bedre løsning," fortsetter Schirrmeister.

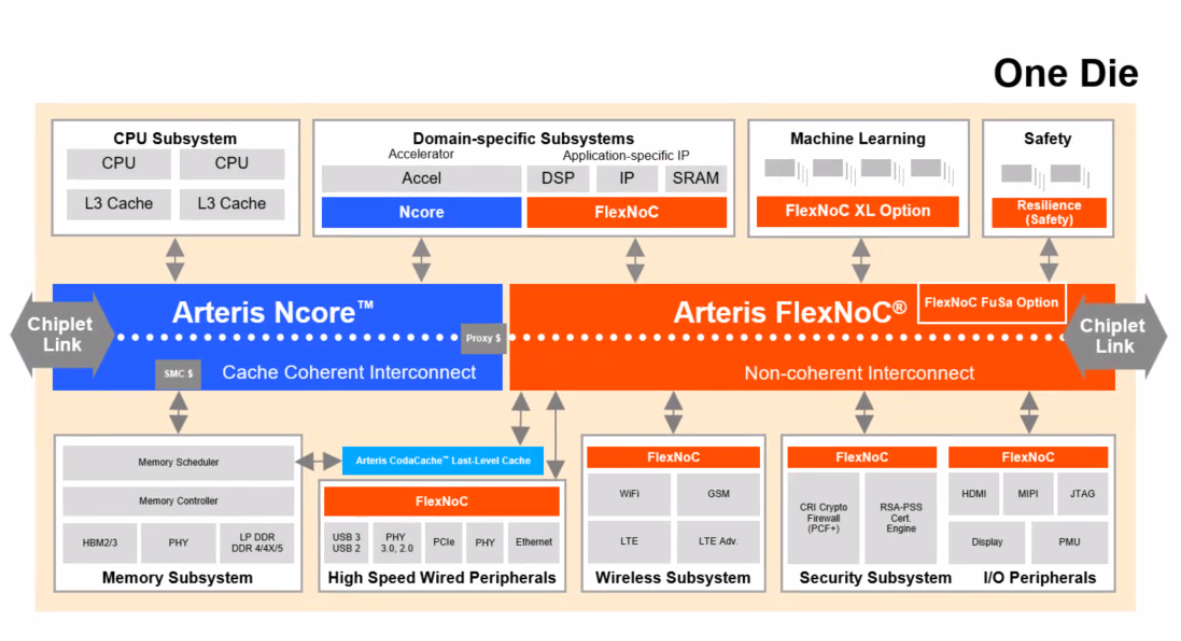

Hvordan kan paring av RISC-V-kjerner med NoC-er se ut? Arteris-kunde Tenstorrent gir et innblikk i mulighetene. Deres nylige fokus er å lage en gjenbrukbar brikke som kombinerer RISC-V-kjerner, maskinlæringsakselerasjons-IP og standard periferiutstyr som finnes i mange avanserte AI-applikasjoner. I stor skala kan en enkeltmatrisimplementering se ut som følgende diagram, ved å bruke Arteris Ncore cache-koherent sammenkobling og flere segmenter av Arteris FlexNoC ikke-koherent sammenkobling.

bilde med tillatelse av Arteris

En Smart Memory Controller (SMC) gir en høyytelses, server-grade minnetilkobling i minnekrevende applikasjoner. Den ikke navngitte "chiplet-lenken" kan være UCIe, en relativt ny spesifikasjon optimalisert for tettere chiplet-integrasjon. Når nye undersystemforbindelser dukker opp, er tilpasning av en del av NoC mer håndterlig enn å rive opp hele brikkevidde strukturen.

Sammenkobling av RISC-V-kjerner med NoC-er reduserer risiko og time-to-market

Hvis det diagrammet ser komplekst ut, og gitt, kanskje de fleste RISC-V-applikasjoner ikke er så komplekse akkurat nå, tenk på dette: chiplets driver allerede integrasjonen mye høyere. Dagens avanserte RISC-V flerkjernedel vil være neste års verdi-SoC ettersom innovasjonen tar fart.

Arteris Ncore og Arteris FlexNoC utviklingsverktøy gir ut RTL for implementering, noe som gir flere fordeler. Fysisk NoC-estimering er enkel i en EDA-arbeidsflyt. NoC-parameterjusteringer, for eksempel antall pipeline-trinn, er også noen få klikk unna i EDA-verktøy. Modifikasjonene nevnt ovenfor for å legge til en undersystemprotokoll kan også lett utføres. "I den høye enden får brukere umiddelbar tilgang til vår NoC-ekspertise," sier Schirrmeister. "I den lave enden er verktøyene våre enkle å bruke for førstegangssuksess og gir en vekstvei for mer ambisiøse fremtidige prosjekter med komplekse sammenkoblinger."

Sammenkobling av RISC-V-kjerner med NoC-er reduserer risikoen for at en IP-blokk til kommer inn i et design og utløser en bølge av redesign av sammenkoblinger over brikken. Det reduserer også time-to-market for komplekse SoC-design sammenlignet med gjør-det-selv-sammenkoblingsstrukturer. Vi har ikke diskutert de andre fordelene med NoC-er her, for eksempel båndbredde og strømstyring, men saken for NoC-er i RISC-V-design er sterk bare med tanke på en mangfoldig protokollmiks.

Besøk Arteris nettside for mer informasjon om NoCs og andre produkter.

Del dette innlegget via:

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- PlatoData.Network Vertical Generative Ai. Styrk deg selv. Tilgang her.

- PlatoAiStream. Web3 Intelligence. Kunnskap forsterket. Tilgang her.

- PlatoESG. Karbon, CleanTech, Energi, Miljø, Solenergi, Avfallshåndtering. Tilgang her.

- PlatoHelse. Bioteknologisk og klinisk etterretning. Tilgang her.

- kilde: https://semiwiki.com/ip/arteris/336086-pairing-risc-v-cores-with-nocs-ties-soc-protocols-together/

- : har

- :er

- :ikke

- :hvor

- $OPP

- a

- evne

- ovenfor

- akselerasjon

- adgang

- oppnådd

- Ifølge

- tvers

- legge

- justeringer

- avansert

- fordeler

- AI

- allerede

- også

- ambisiøs

- an

- og

- En annen

- svar

- noen

- hva som helst

- vises

- søknader

- ER

- rundt

- AS

- At

- oppmerksomhet

- borte

- Båndbredde

- Bar

- BE

- blir

- Fordeler

- Bedre

- mellom

- Blokker

- Blocks

- buss

- virksomhet

- forretningsutvikling

- men

- CAN

- saken

- utfordringer

- endring

- endring

- chip

- kombinere

- handelsvare

- sammenlignet

- fullføre

- komplekse

- kompleksitet

- Beregn

- Koble

- tilkobling

- Tilkoblinger

- Vurder

- ansett

- vurderer

- fortsetter

- kontinuerlig

- controller

- Kjerne

- Corp

- kunne

- telling

- Opprette

- kunde

- dato

- definere

- definisjon

- Etterspørsel

- utforming

- designere

- design

- Utvikling

- utviklingsverktøy

- forskjellig

- vanskelig

- diskutert

- diverse

- do

- kjøring

- hver enkelt

- lett

- Edge

- effektivt

- dukke

- Emery

- slutt

- går inn

- Hele

- Selv

- erfaring

- ekspertise

- utvidelser

- raskere

- Noen få

- felt

- slåss

- Først

- flyten

- Fokus

- fokuserer

- etter

- Til

- Krefter

- funnet

- frank

- fra

- funksjon

- framtid

- Gevinst

- Gates

- Giving

- Glimpse

- innvilget

- Vekst

- Ha

- hjulpet

- her.

- Høy

- høy ytelse

- høyere

- Men

- HTTPS

- bilde

- umiddelbar

- gjennomføring

- in

- informasjon

- Innovasjon

- i stedet

- integrering

- sammenkobling

- sammenkoblinger

- inn

- IP

- IT

- DET ER

- bare

- siste

- lanseringer

- minst

- mindre

- i likhet med

- Sannsynlig

- linje

- linjer

- lenger

- Se

- ser ut som

- UTSEENDE

- Lav

- lavere

- ledelse

- mange

- max bredde

- Kan..

- kan være

- Minne

- nevnt

- metrisk

- bland

- moderat

- Moderne

- modifikasjoner

- mer

- mest

- flyttet

- mye

- flere

- må

- Ny

- neste

- Nei.

- Forestilling

- nå

- Antall

- of

- on

- ONE

- åpnet

- optimalisert

- or

- Annen

- vår

- produksjon

- Fred

- sammenkobling

- parameter

- del

- banen

- for

- ytelse

- perifer

- periferiutstyr

- fysisk

- plukke

- Picks

- rørledning

- plato

- Platon Data Intelligence

- PlatonData

- Spille

- spiller

- muligheter

- Post

- potensiell

- makt

- kraftig

- prosessor

- Produkter

- prosjekter

- protokollen

- protokoller

- gi

- gir

- gi

- raskt

- lett

- nylig

- gjenkjenner

- redesign

- reduserer

- relativt

- forskning

- gjenbruk

- ikke sant

- Ripple

- Rise

- Risiko

- Kjør

- s

- sier

- Skala

- scenarier

- ordninger

- Seksjon

- sett

- Sees

- segmenter

- velge

- flere

- Form

- deling

- Enkelt

- siden

- enkelt

- Smart

- løsning

- Solutions

- noen

- sofistikert

- spesifikasjon

- stadier

- Standard

- rett fram

- sterk

- struktur

- strukturer

- senere

- suksess

- slik

- supermakt

- Teknologi

- enn

- Det

- De

- deres

- Disse

- Tredje

- denne

- trodde

- tre

- nivået

- Ties

- strammere

- tid

- til

- dagens

- sammen

- verktøy

- transportere

- utløsende

- UNAVNT

- oppdatert

- bruke

- Brukere

- ved hjelp av

- verdi

- ulike

- Varierende

- av

- Se

- vp

- we

- Nettsted

- Hva

- Hva er

- når

- vil

- med

- Arbeid

- arbeidsflyt

- zephyrnet