Den var inn igjen 1991 at Cadence først annonserte Virtuoso-produktnavnet, og her er vi 32 år senere, og produktet lever og gjør det ganske bra. Steven Lewis fra Cadence ga meg en oppdatering om noe nytt som de kaller Virtuos Studio, og det handler om tilpasset IC-design for den virkelige verden. I løpet av de 32 årene har vi sett halvlederprosessen marsjere langs Moores lov fra 600nm ved bruk av plan CMOS, nedskalert til FinFET-æraen under 22 nm, og nådd GAA ved 3nm-noden. Tydeligvis har EDA-verktøykravene endret seg ettersom mindre noder har gitt nye fysiske effekter som måtte modelleres og simuleres for å sikre første silisiumsuksess.

Fokuset til Cadence Virtuoso Studio er å hjelpe IC-designere med å ta på seg dagens utfordringer gjennom seks områder:

- Økt prosesskompleksitet

- Håndterer 10,000 XNUMX-vis av kretssimuleringer

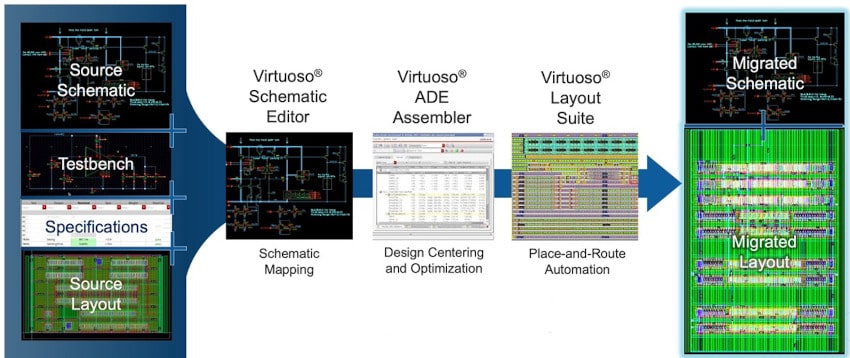

- Designautomatisering og kretsmigrering

- Heterogen integrasjon

- AI

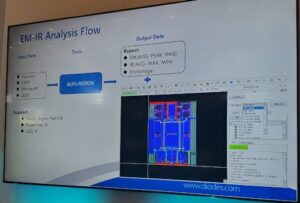

- Sign-off, in-design verifisering og analyse

De Virtuos ADE (Analog Design Environment) lar kretsingeniører utforske sine analoge, blandede signal- og RFIC-design gjennom skjematisk fangst og kretssimulering. Arkitekturen til Virtuoso ADE har blitt fornyet for bedre jobbkontroll, redusere RAM-bruk og øke hastigheten på simuleringer ved å bruke skyen. For ett eksempel ble RAM-en som kreves for å kjøre Spectre på 10,000 420-vis med simuleringer redusert fra 18 MB ned til bare 420 MB for simuleringsovervåking, mens uttrykksevalueringer reduserte fra 280 MB RAM til bare XNUMX MB.

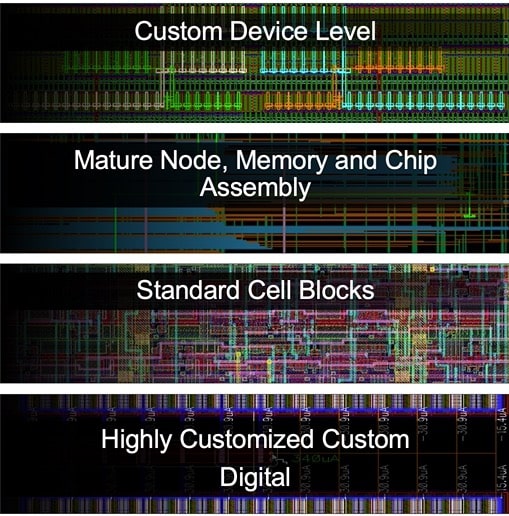

Oppdateringer til Virtuos Layout Suite inkluderer fire valg av sted og ruteteknologi, som hver passer til den unike oppgaven som er på hånden gjennom det virtuose miljøet:

Fire P&R-teknologier

DRC- og LVS-kjøringer er en del av fysisk verifisering, og å kjøre disse i batch-modus, fikse og gjenta, fører til lange utviklingsplaner. In-design-verifisering tillater interaktiv bruk av DRC og LVS mens du jobber med en IC-layout, så tilbakemelding om hva som skal endres blir raskt fremhevet, noe som øker produktiviteten. En layoutdesigner som bruker Virtuoso Layout Suite drar nytte av designverifisering ved å bruke Pegasus DRC og LVS teknologi.

Chiplets, 2.5D og 3D-emballasje spenner over de tradisjonelt separate rikene av PCB-, pakke- og IC-designdomener. Virtuoso Studio muliggjør co-design og verifisering av pakker, moduler og ICer ved å:

Når du ser inn i nær fremtid, kan du forvente å se detaljer dukke opp om hvordan AI brukes for automatisk å gå fra en analog skjematisk til layout basert på maskinlæring og spesifikasjoner. Disse autogenererte prøveoppsettene vil ytterligere fremskynde en svært arbeidskrevende prosess. Et annet utviklingsområde for AI som skal brukes, er problemet med å migrere tilpasset analog IP til en ny prosessnode. Følg med.

Tidlige kunder av Virtuoso Studio inkluderer Analog Devices for co-design av IC og pakke, ledende IC-forbrukerdesign hos MediaTek og AI-basert prosessmigrering hos Renesas.

Oppsummering

Virtuoso Studio har satt i utgivelse 23.1 noen imponerende nye funksjoner som IC-designteam kan begynne å bruke for å bli mer produktive. Den virtuose infrastrukturen har endret seg for å møte utfordringene i Moores lov, simuleringer med 10,000 2.5-talls kretssimuleringer er praktiske, RFIC og modul 3D/XNUMXD co-design støttes, DRC/LVS-verifisering i design tar mye mindre tid, og AI er brukes til å automatisere analoge oppgaver.

Relaterte blogger

Del dette innlegget via:- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- Platoblokkkjede. Web3 Metaverse Intelligence. Kunnskap forsterket. Tilgang her.

- Minting the Future med Adryenn Ashley. Tilgang her.

- kilde: https://semiwiki.com/eda/327556-whats-new-with-cadence-virtuoso/

- : har

- :er

- $OPP

- 1

- 10

- 3d

- a

- Om oss

- akselerer

- AI

- Alle

- tillater

- langs

- og

- annonsert

- anvendt

- arkitektur

- ER

- AREA

- områder

- AS

- At

- automatisere

- automatisk

- Automatisering

- tilbake

- basert

- BE

- vært

- være

- under

- Fordeler

- Bedre

- brakte

- by

- Cadence

- ring

- CAN

- fangst

- utfordringer

- endring

- valg

- klart

- Cloud

- forbruker

- kontroll

- skikk

- Kunder

- dag

- krav

- utforming

- designer

- designere

- design

- detaljer

- Utvikling

- Enheter

- gjør

- domener

- ned

- hver enkelt

- effekter

- muliggjør

- Ingeniører

- sikre

- Miljø

- Era

- evalueringer

- eksempel

- forvente

- utforske

- Egenskaper

- tilbakemelding

- Først

- Fokus

- Til

- fire

- fra

- videre

- framtid

- Go

- hånd

- Ha

- hjelpe

- her.

- Fremhevet

- Hvordan

- HTML

- HTTPS

- ICS

- imponerende

- in

- inkludere

- Infrastruktur

- interaktiv

- IP

- Jobb

- jpg

- arbeidskraft

- Law

- Layout

- Fører

- læring

- Lewis

- Lang

- maskin

- maskinlæring

- Mars

- max bredde

- Møt

- migrasjon

- Mote

- moduler

- Moduler

- overvåking

- mer

- navn

- Nær

- nødvendig

- Ny

- Nye funksjoner

- node

- noder

- of

- on

- ONE

- pakke

- pakker

- emballasje

- del

- fysisk

- Sted

- plato

- Platon Data Intelligence

- PlatonData

- Post

- Praktisk

- presentere

- Problem

- prosess

- Produkt

- produktiv

- produktivitet

- sette

- raskt

- RAM

- nå

- ekte

- virkelige verden

- Redusert

- redusere

- slipp

- påkrevd

- Rute

- Kjør

- rennende

- skalering

- Sekund

- se detaljer

- halvledere

- separat

- Silicon

- simulering

- SIX

- mindre

- So

- noen

- noe

- span

- spesifikasjoner

- spektrum

- fart

- Begynn

- opphold

- studio

- suksess

- suite

- Støttes

- Ta

- tar

- Oppgave

- oppgaver

- lag

- Teknologi

- Det

- De

- deres

- Disse

- Gjennom

- tid

- til

- verktøy

- tradisjonelt

- prøve

- unik

- Oppdater

- bruk

- bruke

- Verifisering

- av

- VI VIL

- Hva

- mens

- vil

- med

- arbeid

- verden

- år

- zephyrnet