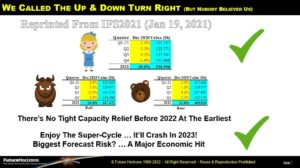

Mange troverdige markedsanalysefirmaer spår at halvledermarkedet vil nå trillioner dollar i løpet av de neste seks årene eller så. Bare sammenlign dette med de mer enn seks tiårene det tok for markedet å krysse 500 milliarder dollar. Den anslåtte vekstraten er virkelig utrolig og er drevet av raskt voksende markedssegmenter som høyytelsesdatabehandling (HPC), mobil, klientdatabehandling og bilelektronikk. Beregningsetterspørselen på systemer har også vokst med utrolige hastigheter hvert par år. Den enorme veksten i kunstig intelligens (AI)-drevne systemer og fremskrittene innen dyplæringsnevrale nettverksmodeller har absolutt bidratt til dette og trukket oss inn i "SysMoore-æraen." Og multi-die-systemer blir avgjørende for å møte systemkravene til SysMoore-æraen.

Gitt trendene ovenfor, kommer silisium IP til å spille en enda mer kritisk rolle i den fremtidige veksten av halvledermarkedet. Gårsdagens hyllevare IP kommer ikke til å kutte den når det kommer til spesifikke PPA-krav for ulike applikasjoner. Det handler om differensiert IP for spesifikke applikasjoner og prosesser. I SysMoore-epoken bør IP-utviklingsstrategien ikke bare drives av å se frem til neste node, men også se på vertikale markedskrav, horisontalt (prosessvarianter) og bakover ettersom multi-die-systemer muliggjør optimalisering av prosessteknologier.

Forrige uke, Synopsys annonserte en utvidet avtale med Samsung Foundry å utvikle en bred portefølje av IP for å redusere designrisiko og akselerere silisiumsuksess for bil-, mobil- og HPC-markeder, og multi-die-design også. Jeg hadde en mulighet til å chatte med John Koeter, senior visepresident for produktledelse og strategi for IP hos Synopsys. Diskusjonen min fokuserte på å forstå hvordan denne avtalen er forskjellig og den viktige rollen de støttede markedssegmentene og multi-die system-trenden spilte for å komme frem til en utvidet avtale. Følgende er en syntese av diskusjonen min, som fremhever de viktigste punktene.

Proaktivt samarbeid ved å se på vertikale markedsbehov

Synopsys og Samsung Foundry har en lang historie med å samarbeide når det gjelder IP-utvikling. Generelt sett var IP-utvikling i det siste drevet av spesifikk gjensidig kundeetterspørsel. Gitt den komprimerte tiden-til-marked-etterspørselen fra SysMoore Era, har ikke kunder råd til å vente på lange utviklingssykluser etter spesifikke IP-forespørsler. IP-utvikling må starte proaktivt basert på å forutse fremtidig vertikalt marked. Og det er det Synopsys og Samsung Foundry gjør i henhold til denne utvidede avtalen. De vil analysere markedssegmenter og utvikle den nødvendige IP for å ivareta vertikale markedsbehov helhetlig. Sammen vil de for eksempel vurdere hvordan en neste generasjons ADAS-brikke eller en neste generasjons MCU eller neste generasjons mobilbrikke vil se ut og proaktivt utvikle IP for å møte disse behovene. IP vil også bli optimalisert i henhold til sluttapplikasjonens behov. For eksempel vil PCIe IP for HPC-markedet være optimalisert for minst mulig ventetid, mens PCIe IP for bilmarkedet vil bli optimalisert for pålitelighet over et bredere temperaturområde.

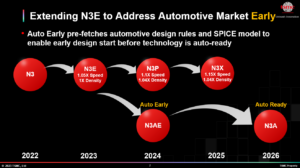

For bilmarkedet spesifikt vil Synopsys optimalisere IP for Samsungs 8LPU, SF5A og SF4A bilprosessnoder for å møte strenge grad 1 eller grad 2 temperatur og AEC-Q100 pålitelighetskrav. Den automatiske IP-en for ADAS SoC-er vil inkludere designfeilmodus- og effektanalyse (DFMEA)-rapporter som kan spare måneder med utviklingsinnsats for SoC-applikasjoner for biler.

Forutse krav til multi-die-systemer

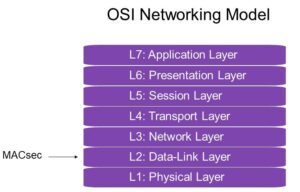

Ettersom monolittiske brikkeimplementeringer viker for multi-die systemimplementeringer, handler det ikke lenger bare om den neste avanserte prosessnoden. Et multi-die-system kan ha forskjellige dyser i forskjellige prosessnoder og fortsatt levere ytelses- og strømkravene til en redusert kostnad sammenlignet med en monolittisk implementering. Dette åpner for muligheten til å vurdere å lage avansert IP (for eksempel PCIe Gen6) for eldre prosessnoder for å støtte I/O-brikker i et multi-die-system. Synopsys og Samsung vurderer proaktivt slike muligheter og vil utvikle en portefølje av avansert IP på mange prosessnoder, samt samarbeide om å utvikle høyhastighets UCIe IP for chip-to-chip kommunikasjon.

Avtaleutvidelse som fører til økt IP-fotavtrykk

Som et resultat av de ovenfor identifiserte IP-samarbeidsstrategiene, kommer tilgjengeligheten IP for Samsung Foundry-prosesser til å øke betydelig. For kunder er det en betydelig økning når det gjelder tilgang til IP i en tidsalder etter Covid-tiden når klare forsyningskjeder er høyt oppe på kravlisten. Med denne avtalen inkluderer Synopsys IP tilgjengelig eller under utvikling for Samsung-prosesser logiske biblioteker, innebygde minner, TCAM-er, GPIO-er, eUSB2, USB 2.0/3.0/3.1/4.0, USB-C/DisplayPort, PCI Express 3.0/4.0/5.0/6.0 , 112G Ethernet, Multi-Protocol 16G/32G PHYs, UCIe, HDMI 2.1, LPDDR5X/5/4X/4, DDR5/4/3, SD3.0/eMMC 5.1, MIPI C/D PHY og MIPI M-PHY G4 /G5.

Synopsys sertifiserte designflyter fremskynder tiden til silisiumsuksess

En bred portefølje av IP fra én enkelt leverandør har flere fordeler, både forretningsmessig og teknisk sett. Fra et ingeniørperspektiv, for eksempel, vil feiljusteringer av strømnett eller pinneplassering ved integrering av forskjellige IP-blokker være mindre sannsynlige. Synopsys jobber også veldig tett med Samsung på EDA-siden for å utvikle og sertifisere ulike referansestrømmer som bør bidra til å akselerere tiden til silisiumsuksess.

Å lese hele pressemelding, klikk her. For mer informasjon, kontakt Synopsys.

Les også:

Krav for suksess med multi-die-system

En automatisert metode for å sikre at design er feilsikre i felten

Del dette innlegget via:

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- EVM Finans. Unified Interface for desentralisert økonomi. Tilgang her.

- Quantum Media Group. IR/PR forsterket. Tilgang her.

- PlatoAiStream. Web3 Data Intelligence. Kunnskap forsterket. Tilgang her.

- kilde: https://semiwiki.com/ip/330636-synopsys-expands-agreement-with-samsung-foundry-to-increase-ip-footprint/

- : har

- :er

- :ikke

- $OPP

- 1

- 300

- 500

- a

- Om oss

- ovenfor

- akselerere

- adgang

- Ifølge

- ADA-er

- adresse

- avansert

- fremskritt

- fordeler

- Etter

- alder

- Avtale

- AI

- Alle

- også

- an

- analyse

- analysere

- og

- annonsert

- forutse

- Søknad

- søknader

- ER

- ankommer

- kunstig

- kunstig intelligens

- Kunstig intelligens (AI)

- AS

- At

- Automatisert

- automotive

- tilgjengelighet

- tilgjengelig

- basert

- BE

- bli

- vært

- Milliarder

- Blocks

- både

- bred

- virksomhet

- men

- by

- CAN

- kan ikke

- Gjerne

- Sertifisert

- sertifisere

- kjeder

- chip

- fjerne

- klikk

- kunde

- tett

- samarbeider

- samarbeid

- kommer

- Kommunikasjon

- sammenligne

- sammenlignet

- Beregn

- databehandling

- Vurder

- vurderer

- kontakt

- bidratt

- Kostnad

- kunne

- Par

- Opprette

- troverdig

- kritisk

- Kryss

- kunde

- Kunder

- Kutt

- sykluser

- tiår

- dyp

- dyp læring

- leverer

- Etterspørsel

- krav

- utforming

- design

- utvikle

- utvikle

- Utvikling

- forskjellig

- differensiert

- diskusjon

- gjør

- Dollar

- drevet

- effekt

- innsats

- Elektronikk

- innebygd

- muliggjøre

- slutt

- Ingeniørarbeid

- sikre

- Era

- avgjørende

- Selv

- Hver

- eksempel

- utvidet

- utvides

- utvidelse

- ekspress

- Failure

- FAST

- bedrifter

- Flows

- fokuserte

- etter

- Fotspor

- Til

- Forward

- Støperi

- fra

- fullt

- framtid

- fremtidig vekst

- generelt

- generasjonen

- Gi

- gitt

- skal

- klasse

- Grid

- Økende

- Vekst

- HAD

- Ha

- hjelpe

- Høy

- High Performance Computing

- utheving

- historie

- Hvordan

- hpc

- HTTPS

- i

- identifisert

- gjennomføring

- viktig

- in

- inkludere

- inkluderer

- Øke

- utrolig

- informasjon

- f.eks

- Integrering

- Intelligens

- inn

- IP

- IT

- John

- jpg

- bare

- Ventetid

- ledende

- læring

- mindre

- bibliotekene

- i likhet med

- Sannsynlig

- Liste

- plassering

- logikk

- Lang

- lenger

- Se

- ser ut som

- ser

- ledelse

- mange

- merke

- marked

- Markedsanalyse

- Markets

- max bredde

- MCU

- Møt

- Minner

- metode

- minimum

- Mobil

- Mote

- modeller

- Monolithic

- måneder

- mer

- flere

- gjensidig

- my

- nødvendig

- behov

- nettverk

- neural

- nevrale nettverket

- neste

- neste generasjon

- Nei.

- node

- noder

- of

- eldre

- on

- bare

- åpner

- Muligheter

- Opportunity

- optimalisering

- Optimalisere

- optimalisert

- or

- enn

- Past

- ytelse

- perspektiv

- plato

- Platon Data Intelligence

- PlatonData

- Spille

- spilt

- poeng

- portefølje

- mulig

- Post

- makt

- Kraftnettet

- forutsi

- president

- prosess

- Prosesser

- Produkt

- produktledelse

- anslått

- område

- Sats

- priser

- å nå

- Lese

- redusere

- Redusert

- slipp

- pålitelighet

- Rapporter

- forespørsler

- Krav

- resultere

- Risiko

- Rolle

- Samsung

- Spar

- sier

- segmenter

- halvledere

- senior

- bør

- side

- signifikant

- betydelig

- Silicon

- enkelt

- SIX

- So

- sett

- spesifikk

- Begynn

- Still

- strategier

- Strategi

- suksess

- slik

- levere

- Forsyningskjeder

- støtte

- Støttes

- system

- Systemer

- Technologies

- vilkår

- enn

- Det

- De

- Fremtiden

- deres

- de

- denne

- De

- tid

- til

- sammen

- tok

- enorm

- Trend

- Trender

- Trillion

- forståelse

- us

- usb

- ulike

- leverandør

- vertikal

- veldig

- av

- Vice President

- vente

- var

- Vei..

- uke

- VI VIL

- Hva

- når

- mens

- hvilken

- bredere

- vil

- med

- arbeid

- år

- zephyrnet