Gedurende het decennium van 2010 begonnen de voordelen van de wet van Moore uiteen te vallen. Volgens de wet van Moore verdubbelde de transistordichtheid elke twee jaar, waardoor de computerkosten met een overeenkomstige 50% zouden dalen. De verandering in de wet van Moore is te wijten aan de toegenomen ontwerpcomplexiteit en de evolutie van de transistorstructuur van vlakke apparaten naar Finfets. Finfets hebben meerdere patronen nodig voor lithografie om apparaatafmetingen tot knooppunten onder de 20 nm te bereiken.

Aan het begin van dit decennium zijn de computerbehoeften geëxplodeerd, vooral als gevolg van de toename van het aantal datacentra en de hoeveelheid gegevens die wordt gegenereerd en verwerkt. Sterker nog, de adoptie van kunstmatige intelligentie (AI) en technieken als machinaal leren (ML) worden nu gebruikt om steeds meer gegevens te verwerken en heeft ertoe geleid dat servers hun rekencapaciteit aanzienlijk hebben vergroot.

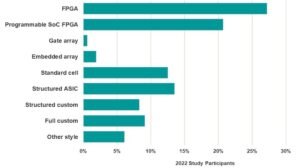

Servers hebben veel meer CPU-kernen toegevoegd, hebben grotere GPU's geïntegreerd die exclusief voor ML worden gebruikt en niet langer voor grafische afbeeldingen worden gebruikt, en hebben aangepaste ASIC AI-versnellers of aanvullende, op FPGA gebaseerde AI-verwerking ingebed. Vroege AI-chipontwerpen werden geïmplementeerd met behulp van grotere monolithische SoC's, waarvan sommige de maximale grootte bereikten die door het dradenkruis werd opgelegd, ongeveer 700 mm2.

Op dit moment lijkt desaggregatie in een kleinere SoC plus verschillende compute- en IO-chiplets de juiste oplossing. Verschillende chipfabrikanten, zoals Intel, AMD of Xilinx, hebben deze optie geselecteerd voor producten die in productie gaan. In het uitstekende witboek van The Linley Group, “Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small”, werd aangetoond dat deze optie tot betere kosten leidt in vergelijking met monolithische SoC’s, vanwege de opbrengstimpact van grotere.

De grootste impact van deze trend op IP-leveranciers ligt vooral op de interconnectiefuncties die worden gebruikt om SoC's en chiplets met elkaar te verbinden. Op dit moment (Q3 2021) worden er verschillende protocollen gebruikt, waarbij de industrie voor veel daarvan geformaliseerde standaarden probeert te ontwikkelen.

De huidige toonaangevende D2D-standaarden omvatten i) Advanced Interface Bus (AIB, AIB2), aanvankelijk gedefinieerd door Intel, en biedt nu royaltyvrij gebruik, ii) High Bandwidth Memory (HBM) waarbij DRAM-chips op elkaar worden gestapeld bovenop een silicium-interposer en zijn verbonden via TSV's, iii) Open Domain-Specific Architecture (ODSA)-subgroep, een branchegroep, heeft twee andere interfaces gedefinieerd, Bunch of Wires (BoW) en OpenHBI.

Dankzij het heterogene chipletontwerp kunnen we ons richten op verschillende toepassingen of marktsegmenten door alleen de relevante chiplets aan te passen of toe te voegen, terwijl de rest van het systeem ongewijzigd blijft. Nieuwe ontwikkelingen zouden sneller op de markt kunnen worden gebracht, met aanzienlijk lagere investeringen, omdat herontwerp alleen invloed zal hebben op het verpakkingssubstraat dat wordt gebruikt om de chiplets te huisvesten.

De computerchiplet kan bijvoorbeeld opnieuw worden ontworpen van TSMC 5nm naar TSMC 3nm om grotere L1-cache of beter presterende CPU-kernen te integreren, terwijl de rest van het systeem ongewijzigd blijft. Aan de andere kant van het spectrum kan alleen de chiplet waarin SerDes is geïntegreerd opnieuw worden ontworpen voor hogere snelheden op nieuwe procesknooppunten die meer IO-bandbreedte bieden voor een betere marktpositionering.

Intel PVC is een perfect voorbeeld van heterogene integratie (verschillende functionele chiplets, CPU, schakelaars, enz.) die we verticale integratie zouden kunnen noemen, wanneer dezelfde chipfabrikant eigenaar is van de verschillende chipletcomponenten (behalve geheugenapparaten).

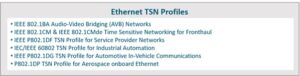

Chipfabrikanten die SoC's ontwikkelen voor geavanceerde toepassingen, zoals HPC, datacenters, AI of netwerken, zijn waarschijnlijk early adopters voor chiplet-architecturen. Specifieke functies, zoals SRAM's voor grotere L3-cache, of AI-versnellers, Ethernet-, PCIe- of CXL-standaarden zouden de eerste interfacekandidaat moeten zijn voor chipletontwerpen.

Wanneer deze early adopters de validiteit hebben aangetoond van heterogene chiplets die gebruik maken van meerdere verschillende bedrijfsmodellen, en uiteraard de haalbaarheid van de productie voor testen en verpakken, zal er een ecosysteem zijn gecreëerd dat van cruciaal belang is om deze nieuwe technologie te ondersteunen. Op dit punt kunnen we een bredere marktacceptatie verwachten, niet alleen voor hoogwaardige toepassingen.

We kunnen ons voorstellen dat heterogene producten nog verder kunnen gaan als een chipfabrikant een systeem op de markt brengt dat bestaat uit verschillende chiplets die zich richten op computer- en IO-functionaliteit. Deze aanpak maakt convergentie op een D2D-protocol verplicht, omdat een IP-leverancier die chiplets aanbiedt met een intern D2D-protocol niet aantrekkelijk is voor de industrie.

Een analogie hiermee is het SoC-gebouw uit de jaren 2000, waar halfgeleiderbedrijven overstappen op het integreren van verschillende ontwerp-IP’s uit verschillende bronnen. De IP-leveranciers van de jaren 2000 zullen onvermijdelijk de chiplet-leveranciers van de 2020 worden. Voor bepaalde functies, zoals geavanceerde SerDes of complexe protocollen, zoals PCIe, Ethernet of CXL, hebben IP-leveranciers de beste kennis om dit op silicium te implementeren.

Voor complexe Design IP moeten leveranciers, zelfs als er simulatieverificatie is uitgevoerd voordat ze naar klanten worden verzonden, de IP op silicium valideren om de prestaties te garanderen. Voor digitale IP kan de functie in FPGA worden geïmplementeerd omdat het sneller en veel goedkoper is dan het maken van een testchip. Voor mix-signal IP, zoals een op SerDes gebaseerde PHY, selecteren leveranciers de Test Chip (TC)-optie waarmee ze het IP-adres in silicium kunnen karakteriseren voordat ze naar de klant worden verzonden.

Hoewel een chiplet niet zomaar een TC is, omdat deze uitgebreid zal worden getest en gekwalificeerd voordat deze in het veld wordt gebruikt, is de hoeveelheid werk die de leverancier moet doen om een productie-chiplet te ontwikkelen veel kleiner. Met andere woorden: de IP-leverancier verkeert in de beste positie om snel een chiplet uit te brengen die is opgebouwd op basis van zijn eigen IP en de best mogelijke TTM te bieden en de risico's te minimaliseren.

Het bedrijfsmodel voor heterogene integratie is er voorstander van dat verschillende chiplets worden gemaakt door de relevante IP-leverancier (bijv. ARM voor op ARM gebaseerde CPU-chiplets, Si-Five voor op Risc-V gebaseerde computerchiplets en Alphawave voor snelle SerDes-chiplets). zij zijn eigenaar van de Design IP.

Niets van dit alles weerhoudt chipmakers ervan hun eigen chiplets te ontwerpen en complexe ontwerp-IP's te gebruiken om hun unieke architecturen te beschermen of zelfgemaakte interconnecties te implementeren. Net als bij SoC Design IP in de jaren 2000 zal de koop- of maakbeslissing voor chiplets worden afgewogen tussen de bescherming van kerncompetenties en de inkoop van niet-differentiërende functies.

We hebben gezien dat de historische en hedendaagse groei van Design IP sinds de jaren 2000 werd ondersteund door de voortdurende adoptie van externe sourcing. Beide modellen zullen naast elkaar bestaan (chiplet ontworpen in eigen huis of door een IP-leverancier), maar de geschiedenis heeft geleerd dat de koopbeslissing uiteindelijk de overhand krijgt.

Er bestaat nu consensus in de industrie dat een maniakale focus op het verwezenlijken van de wet van Moore niet meer geldt voor bijvoorbeeld geavanceerde technologieknooppunten. 7 nm en lager. Chipintegratie vindt nog steeds plaats, waarbij er op elk nieuw technologieknooppunt meer transistors per vierkante mm worden toegevoegd. De kosten per transistor worden echter ook met elk nieuw knooppunt hoger.

Chiplet-technologie is een belangrijk initiatief om meer integratie voor de belangrijkste SoC te stimuleren, terwijl oudere knooppunten voor andere functionaliteit worden gebruikt. Deze hybride strategie verlaagt zowel de kosten als het ontwerprisico dat gepaard gaat met de integratie van andere Design IP rechtstreeks op de hoofd-SoC.

IPnest gelooft dat deze trend twee belangrijke effecten zal hebben in de interface-IP-activiteiten: het ene zal de sterke groei van de D2D IP-inkomsten binnenkort (2021-2025) zijn, en het andere is de creatie van de heterogene chipletmarkt om de high-end silicium-inkomsten te vergroten. IP-markt.

Deze markt zal naar verwachting bestaan uit complexe protocolfuncties zoals PCIe, CXL of Ethernet. IP-leveranciers die interface-IP leveren die is geïntegreerd in I/O SoC's (USB, HDMI, DP, MIPI, enz.) kunnen besluiten om in plaats daarvan I/O-chiplets te leveren.

De andere IP-categorieën die door deze revolutie worden beïnvloed, zijn IP-leveranciers van SRAM-geheugencompilers voor L3-cache. Van nature wordt verwacht dat de cachegrootte varieert, afhankelijk van de processor. Niettemin kan het ontwerpen van een L3-cachechiplet voor IP-leveranciers een manier zijn om de Design IP-inkomsten te vergroten door een nieuw producttype aan te bieden.

Ook kan de NVM IP-categorie positief worden beïnvloed, omdat NVM IP niet langer is geïntegreerd in SoC's die zijn ontworpen op geavanceerde procesknooppunten. Het zou voor NVM IP-leveranciers een manier zijn om nieuwe business te genereren door het aanbieden van chiplets.

We denken dat FPGA- en AI-accelerator-chiplets een nieuwe bron van inkomsten zullen zijn voor ASSP-chipfabrikanten, maar we denken niet dat ze strikt kunnen worden gerangschikt als IP-leveranciers.

Als Interface IP-leveranciers belangrijke spelers zullen zijn in deze siliciumrevolutie, zullen de siliciumgieterijen die zich richten op de meest geavanceerde knooppunten zoals TSMC en Samsung ook een sleutelrol spelen. We denken niet dat gieterijen chiplets zullen ontwerpen, maar ze zouden de beslissing kunnen nemen om IP-leveranciers te ondersteunen en hen ertoe aan te zetten chiplets te ontwerpen voor gebruik met SoC's in 3nm, zoals ze vandaag doen bij het ondersteunen van geavanceerde IP-leveranciers om hun high-end SerDes op de markt te brengen. als harde IP in 7nm en 5nm.

Intel's recente transitie naar 3rd Er wordt verwacht dat partijgieterijen ook gebruik zullen maken van IP's van derden, evenals van de heterogene adoptie van chiplets door zwaargewichten in de halfgeleiderindustrie. In dit geval lijdt het geen twijfel dat Hyperscalars zoals Microsoft, Amazon en Google ook chiplet-architecturen zullen adopteren... als ze Intel niet voorgaan bij de adoptie van chiplets.

By Erik Esteve (PhD.) Analist, Eigenaar IPnest

Deel dit bericht via: Bron: https://semiwiki.com/semiconductor-services/ipnest/303790-chiplet-are-you-ready-for-next-semiconductor-revolution/

- 2021

- versneller

- versnellers

- Adoptie

- "Gevorderde Technologie

- AI

- Het toestaan

- Amazone

- AMD

- analist

- toepassingen

- architectuur

- ARM

- kunstmatige intelligentie

- Kunstmatige intelligentie (AI)

- ASIC

- BEST

- bouw

- Gebouw

- Bos

- bus

- bedrijfsdeskundigen

- bedrijfsmodel

- kopen

- Bellen

- Inhoud

- verandering

- spaander

- chips

- komst

- Bedrijven

- Berekenen

- computergebruik

- Overeenstemming

- Kosten

- Klanten

- gegevens

- het leveren van

- Design

- ontwikkelen

- systemen

- digitaal

- Vroeg

- early adopters

- ecosysteem

- etc

- Evolutie

- Voornaam*

- Focus

- FPGA

- Gratis

- functie

- Kopen Google Reviews

- GPU's

- Groep

- Groeiend

- Hoge

- geschiedenis

- Huis

- HTTPS

- Hybride

- Impact

- Laat uw omzet

- -industrie

- initiatief

- integratie

- Intel

- Intelligentie

- investering

- IP

- IT

- houden

- sleutel

- lancering

- Wet

- leidend

- leren

- LED

- Hefboomwerking

- LINK

- machine learning

- groot

- maker

- maken

- productie

- Markt

- Microsoft

- ML

- model

- netwerken

- nieuw product

- knooppunten

- bieden

- het aanbieden van

- open

- Keuze

- Overige

- eigenaar

- verpakking

- Papier

- prestatie

- Product

- productie

- Producten

- beschermen

- bescherming

- Tarieven

- herontwerp

- REST

- Risico

- lopen

- Samsung

- halfgeleider

- Verzending

- simulatie

- Maat

- normen

- Strategie

- ondersteuning

- Stap over voor slechts

- system

- doelwit

- technieken

- Technologie

- proef

- top

- us

- usb

- vendors

- Verificatie

- wit papier

- woorden

- Mijn werk

- jaar

- Opbrengst