Als we kijken naar de uitbreiding van de halfgeleiderindustrie in de afgelopen 25 jaar, lijkt de adoptie van ontwerp-IP in elke toepassing een van de belangrijkste succesfactoren te zijn, waarbij de siliciumtechnologie een ongelooflijke ontwikkeling heeft doorgemaakt met een factor x100, van 250 nm in 2018 naar 3 nm (als niet 2 nm) in 2023. We voorzien dat de overstap naar op chiplets gebaseerde architectuur binnenkort dezelfde rol zal spelen als de op SoC-chips gebaseerde architectuur en het massale gebruik van ontwerp-IP in de jaren 2000.

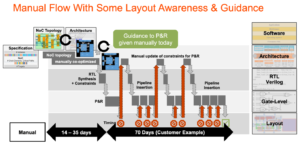

De vraag is hoe het tijdsbestek voor de adoptie van chiplets nauwkeurig kan worden voorspeld en wat de belangrijkste factoren voor deze revolutie zullen zijn. We zullen zien of de verspreiding van innovatietheorieën kan helpen om een voorspelling te verfijnen en te bepalen welk type toepassing de drijvende kracht zal zijn. Standaardspecificaties van het chip-naar-chip-interconnectprotocol die een snelle adoptie door de industrie mogelijk maken en het snel aansturen van applicaties zoals IA of een smartphone-applicatieprocessor lijken de belangrijkste factor te zijn, maar onder andere de efficiëntie van EDA-tools of het verpakken van nieuwe technologieën en het creëren van speciale fabrieken zijn zeker van cruciaal belang.

Inleiding: opkomst van chiplettechnologie

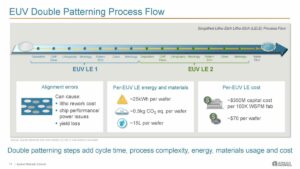

Gedurende het decennium van 2010 begonnen de voordelen van de wet van Moore uiteen te vallen. Volgens de wet van Moore verdubbelde de transistordichtheid elke twee jaar, waardoor de computerkosten met een overeenkomstige 50% zouden dalen. De verandering in de wet van Moore is te wijten aan de toegenomen ontwerpcomplexiteit en de evolutie van de transistorstructuur van vlakke apparaten naar Finfets. Finfets hebben meerdere patronen nodig voor lithografie om apparaatafmetingen tot knooppunten onder de 20 nm te bereiken.

Aan het einde van dit decennium zijn de computerbehoeften geëxplodeerd, vooral als gevolg van de proliferatie van datacentra en als gevolg van de hoeveelheid gegevens die wordt gegenereerd en verwerkt. Sterker nog, de adoptie van kunstmatige intelligentie (AI) en technieken als machinaal leren (ML) worden nu gebruikt om steeds meer gegevens te verwerken en heeft ertoe geleid dat servers hun rekencapaciteit aanzienlijk hebben vergroot. Servers hebben veel meer CPU-kernen toegevoegd, hebben grotere GPU's geïntegreerd die exclusief voor ML worden gebruikt en niet langer voor grafische afbeeldingen worden gebruikt, en hebben aangepaste ASIC AI-versnellers of aanvullende, op FPGA gebaseerde AI-verwerking ingebed. Vroege AI-chipontwerpen werden geïmplementeerd met behulp van grotere monolithische SoC's, waarvan sommige de maximale grootte bereikten die door het dradenkruis werd opgelegd, ongeveer 700 mm2.

Op dit moment lijkt desaggregatie in een kleinere SoC plus verschillende compute- en IO-chiplets de juiste oplossing. Verschillende chipfabrikanten, zoals Intel, AMD of Xilinx, hebben deze optie geselecteerd voor producten die in productie gaan. In het uitstekende witboek van The Linley Group, “Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small”, werd aangetoond dat deze optie tot betere kosten leidt in vergelijking met monolithische SoC’s, vanwege de opbrengstimpact van grotere. Deze chipfabrikanten hebben homogene chiplets ontworpen, maar de opkomst en acceptatie van interconnect-standaarden zoals Universal Chiplet Interconnect Express (UCIe) IP vergemakkelijkt de adoptie van heterogene chiplets.

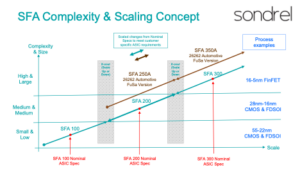

De evolutie van de nieuwere, snellere protocolstandaarden versnelt nu de industrie blijft vragen om hogere prestaties. Helaas worden de verschillende standaarden niet door één organisatie op elkaar afgestemd. Nieuwe PCIe-standaarden kunnen een jaar (of langer) eerder of later komen dan de nieuwe Ethernet-protocolstandaard. Door heterogene integratie te gebruiken, kunnen siliciumleveranciers zich aanpassen aan de snel veranderende markt door alleen het ontwerp van de relevante chiplet te veranderen. Aangezien de fabricage van geavanceerde SoC-ontwerpen enorme kapitaaluitgaven vereist voor 5nm-, 4nm- of 3nm-procesknooppunten, is de impact van chiplet-architecturen enorm om toekomstige innovatie in de halfgeleiderruimte te stimuleren.

Dankzij het heterogene chipletontwerp kunnen we ons richten op verschillende toepassingen of marktsegmenten door alleen de relevante chiplets aan te passen of toe te voegen, terwijl de rest van het systeem ongewijzigd blijft. Nieuwe ontwikkelingen zouden sneller op de markt kunnen worden gebracht, met aanzienlijk lagere investeringen, omdat herontwerp alleen invloed zal hebben op het verpakkingssubstraat dat wordt gebruikt om de chiplets te huisvesten. De computerchiplet kan bijvoorbeeld opnieuw worden ontworpen van TSMC 5nm naar TSMC 3nm om een grotere L1-cache of een beter presterende CPU of een aantal CPU-cores te integreren, terwijl de rest van het systeem ongewijzigd blijft. Chiplet waarin SerDes is geïntegreerd, kan opnieuw worden ontworpen voor hogere snelheden op nieuwe procesknooppunten die meer IO-bandbreedte bieden voor een betere marktpositionering.

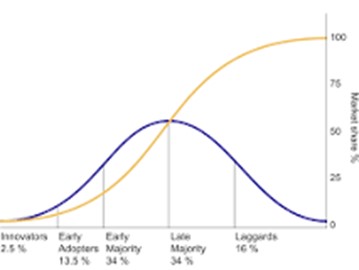

Het gebruik van een heterogene chiplet biedt een betere Time-to-Market (TTM) bij het updaten van het systeem, waarbij het deel van het systeem zonder wijziging wordt hergebruikt als het in chiplet is ontworpen. Dit zal ook een manier zijn om de kosten te minimaliseren bij het behouden van een functionele chiplet op minder geavanceerde knooppunten, goedkoper dan de meest geavanceerde. Maar de belangrijkste vraag is: voorspellen wanneer de chiplettechnologie een aanzienlijk segment van de halfgeleidermarkt zal creëren? We zullen de geschiedenis van IP-adoptie bekijken, aangezien chiplet en IP vergelijkbaar zijn en beide het NIH-syndroom moeten doorbreken om succesvol te worden. We zullen de belangrijkste oorzaken van chiplet-adoptie achterhalen en een voorspelling opstellen, met behulp van de innovatietheorie en de gedefinieerde categorie (Innovators, Early Adopters, etc., zie onderstaande figuur).

We zullen de ARM CPU IP-adoptie van 1991 tot 2018 en de IP-adoptiegeschiedenis van 1995 tot 2027 bekijken, en nagaan hoe dit adoptiepercentage aansluit bij de innovatietheorie.

We zullen uitleggen waarom de adoptie van chiplets zal worden gestimuleerd, waarbij we de technologie- en marketinggerelateerde redenen bekijken:

- Van IP-gebaseerde SoC naar chiplet-gebaseerd systeem

- Interoperabiliteit dankzij de voorkeursprotocolstandaard voor chiplet-interconnect

- Uitleggen waarom high-end Interface IP essentieel is voor de acceptatie van Chiplet

- Ontwerpgerelateerde uitdagingen om op te lossen.

- Last but not least: de investeringen van de gieterij

Ten slotte kunnen we een voorlopige voorspelling voor de adoptie van chiplets opstellen, gebaseerd op de innovatietheorie. Om maar te zwijgen: de sector bevindt zich net in de fase van ‘Early adopters’, waarbij talloze IP- en chipletleveranciers HPC en AI bedienen.

Als u de downloadt wit papier, je zult ervan genieten met alle tekst en talloze afbeeldingen, waarvan sommige exclusief voor dit werk zijn gemaakt.

By Erik Esteve (PhD.) Analist, Eigenaar IPnest

Alphawave sponsorde de creatie van dit witboek, maar de meningen en analyses zijn die van de auteur. Artikel is hier te vinden:

https://awavesemi.com/resource/will-chiplet-adoption-to-mimic-ip-adoption/

Lees ook:

Interface IP in 2022: 22% jaar-op-jaar groei nog steeds datagericht

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiwiki.com/chiplet/339927-will-chiplet-adoption-mimic-ip-adoption/

- : heeft

- :is

- :niet

- $UP

- 1

- 1995

- 200

- 2018

- 2022

- 2023

- 25

- a

- Over

- versnellers

- Bereiken

- aanpassen

- toegevoegd

- toe te voegen

- adoptanten

- Adoptie

- vergevorderd

- AI

- AI-gegevens

- Alles

- Het toestaan

- toestaat

- ook

- AMD

- onder

- bedragen

- analyse

- analist

- en

- uit elkaar

- komt naar voren

- Aanvraag

- toepassingen

- architectuur

- ZIJN

- ARM

- dit artikel

- kunstmatig

- kunstmatige intelligentie

- Kunstmatige intelligentie (AI)

- AS

- ASIC

- vragen

- At

- auteur

- bandbreedte

- gebaseerde

- BE

- worden

- begon

- wezen

- onder

- betekent

- Betere

- Groot

- Boosted

- zowel

- Breken

- bouw

- maar

- by

- cache

- CAN

- Inhoud

- hoofdstad

- Categorie

- oorzaken

- zeker

- uitdagingen

- verandering

- veranderende

- goedkoper

- controle

- spaander

- chips

- hoe

- vergeleken

- complementair

- ingewikkeldheid

- Berekenen

- computergebruik

- aangezien

- Overeenkomend

- Kosten

- Kosten

- kon

- CPU

- en je merk te creëren

- aangemaakt

- het aanmaken

- gewoonte

- gegevens

- decennium

- toegewijd aan

- gedefinieerd

- dichtheid

- Design

- ontworpen

- ontwerpen

- Bepalen

- Ontwikkeling

- ontwikkelingen

- systemen

- anders

- Verspreiding

- Afmeting

- verdubbelde

- Download

- rit

- bestuurder

- aandrijving

- twee

- gedurende

- Vroeger

- Vroeg

- early adopters

- versoepeling

- ecosysteem

- doeltreffendheid

- ingebed

- opkomst

- enabler

- waardoor

- einde

- en geniet van

- etc

- steeds groter

- Alle

- Evolutie

- voorbeeld

- uitstekend

- uitsluitend

- uitbreiding

- Verklaren

- uitdrukkelijk

- extract

- feit

- factor

- factoren

- Vallen

- SNELLE

- sneller

- Figuur

- Voor

- Voorspelling

- voorzien

- gevonden

- FPGA

- oppompen van

- functioneel

- toekomst

- Krijgen

- gegenereerde

- het krijgen van

- gaan

- GPU's

- grafiek

- Groep

- Hebben

- nuttig

- hier

- High-End

- hoger

- geschiedenis

- Huis

- Hoe

- How To

- hpc

- HTTPS

- ia

- if

- Impact

- geïmplementeerd

- opgelegd

- in

- meer

- meer

- ongelooflijk

- -industrie

- Innovatie

- innovators

- integreren

- geïntegreerde

- Integreren

- integratie

- Intel

- Intelligentie

- Interface

- in

- investering

- IP

- IT

- jpg

- voor slechts

- houden

- sleutel

- groter

- Achternaam*

- later

- gelanceerd

- Wet

- Leads

- leren

- minst

- LED

- minder

- als

- LIMIT

- langer

- Kijk

- te verlagen

- machine

- machine learning

- gemaakt

- Hoofd

- groot

- Makers

- veel

- Markt

- Marketing

- massief

- noemen

- verkleinen

- ML

- monolitisch

- meer

- meest

- meestal

- beweging

- verplaatst

- meervoudig

- Noodzaak

- behoeften

- New

- Nieuwe technologieën

- nieuwere

- NIH

- geen

- knooppunten

- nu

- aantal

- vele

- of

- bieden

- het aanbieden van

- on

- EEN

- Slechts

- Meningen

- Keuze

- or

- organisatie

- Overig

- eigenaar

- pakket

- verpakking

- Papier

- deel

- prestatie

- uitvoerend

- fase

- phd

- PHP

- plukken

- Foto's

- Plato

- Plato gegevensintelligentie

- PlatoData

- Spelen

- gespeeld

- plus

- punt

- positionering

- Post

- Powering

- Precies

- voorspellen

- voorspelling

- bij voorkeur

- verwerkt

- verwerking

- Gegevensverwerker

- productie

- Producten

- protocol

- providers

- vraag

- sneller

- snel

- snel

- tarief

- Tarieven

- het bereiken van

- Lees

- redenen

- herontwerp

- herontworpen

- verwant

- relevante

- herinnering

- vereist

- REST

- beoordelen

- herzien

- Revolutie

- rechts

- Rol

- dezelfde

- zien

- te zien

- lijkt

- segment

- segmenten

- kiezen

- halfgeleider

- servers

- serveer-

- verscheidene

- getoond

- aanzienlijke

- aanzienlijk

- Silicium

- gelijk

- single

- Maat

- kleinere

- smartphone

- oplossing

- OPLOSSEN

- sommige

- Spoedig

- Tussenruimte

- specificaties

- snelheid

- Gesponsorde

- standaard

- normen

- bepaald

- stok

- Still

- structuur

- succes

- geslaagd

- system

- Systems

- doelwit

- technieken

- Technologies

- Technologie

- tekst

- neem contact

- bedankt

- dat

- De

- hun

- Ze

- theorie

- Deze

- dit

- die

- Door

- tijdsbestek

- naar

- tools

- top

- ontzettend

- TSMC

- twee

- type dan:

- helaas

- Universeel

- bijwerken

- us

- .

- gebruikt

- gebruik

- divers

- vendors

- via

- was

- Manier..

- we

- waren

- Wat

- wanneer

- en

- wit

- wit papier

- Waarom

- wil

- Met

- Mijn werk

- zou

- jaar

- jaar

- Opbrengst

- u

- zephyrnet