아날로그 IC 설계자는 회로 설계를 위해 오래되고 친숙한 수동 반복 방법을 재사용하는 데 너무 많은 시간과 노력을 소비할 수 있습니다. 왜냐하면 이것이 항상 해왔던 방식이기 때문입니다. 회로 최적화는 아날로그 및 혼합 신호 설계 요구 사항을 충족하기 위해 PVT 코너 및 프로세스 변형 전반에 걸쳐 SPICE 시뮬레이션을 실행하여 셀의 모든 트랜지스터 크기를 자동으로 조정할 수 있는 EDA 접근 방식입니다. 유망한 것 같죠?

그렇다면 어떤 회로 최적화 프로그램을 사용해야 할까요?

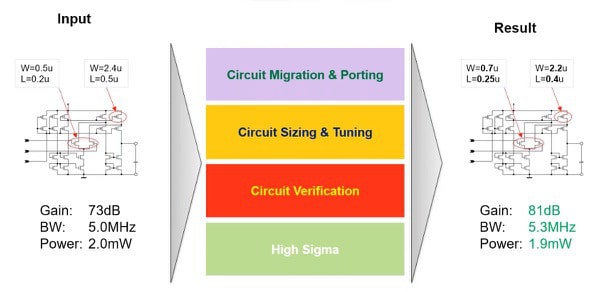

그 질문에 답하기 위해 다음 웹 세미나가 예정되어 있습니다. 문에다, EDA 회사는 2001년에 시작했으며 이름이 회로 최적화 프로그램에 관한 것입니다. 사악한. 입력은 이득, 대역폭, 전력 소비와 같은 설계 요구 사항이 포함된 SPICE 넷리스트입니다. 출력은 설계 요구 사항을 충족하거나 초과하는 크기의 넷리스트입니다.

WiCkeD의 비밀 소스는 기계 학습(ML) 모델을 구축하여 DOE(실험 계획법)를 실행하여 최악의 PVT 코너를 계산하고, 트랜지스터 기하학적 민감도를 찾고, OCV(On Chip Variation)까지 계산하는 방법입니다. ) 감도. 이 접근 방식은 시뮬레이션된 데이터에서 비선형 고차원 ML 모델을 생성하고 업데이트합니다.

ML 모델이 있으면 도구에서 최적화 문제를 해결한 다음 SPICE 시뮬레이션을 실행하여 최종 검증을 수행할 수 있습니다. 모든 요구 사항이 충족될 때까지 자동화된 반복이 수행됩니다. 이제는 이전의 수동 반복 방법보다 훨씬 빠르게 들립니다. ML 모델 교육은 모두 자동으로 이루어지며 매우 효율적입니다.

회로 설계자는 다음 내용도 배웁니다.

- 회로 최적화를 사용하는 위치

- 어떤 유형의 회로를 최적화하는 것이 좋은가요?

- 회로 최적화가 설계 흐름에 얼마나 많은 가치를 가져다 주는가

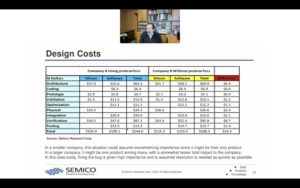

STMicroelectronics의 엔지니어들은 WiCkeD의 회로 최적화를 사용해 왔으며 MunEDA는 시간 절약 및 요구 사항 충족 개선에 대한 구체적인 결과에 대해 설명합니다. 전력 증폭기 회사인 Inplay Technologies는 DAC 2018 컨퍼런스에서 회로 최적화 결과를 선보였습니다.

웨비나 세부 정보

11월 10일 오전 XNUMX시(PDT)에 웹 세미나를 시청하세요. 온라인 등록.

관련 블로그

다음을 통해이 게시물 공유 :- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- 플라토 블록체인. Web3 메타버스 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 출처: https://semiwiki.com/eda/326047-webinar-enhance-productivity-with-machine-learning-in-the-analog-front-end-design-flow/

- :이다

- $UP

- 2001

- 2018

- a

- 소개

- 가로질러

- All

- 항상

- 과

- 답변

- 접근

- XNUMX월

- 있군요

- At

- 자동화

- Automatic

- 자동적으로

- 뒤로

- 대역폭

- 때문에

- 돋보이게

- 빌드

- by

- 계산하다

- CAN

- 도전

- 칩

- 오는

- 회사

- 컨퍼런스

- 고려

- 소비

- 모서리

- 모서리

- 생성

- 데이터

- 디자인

- 디자이너

- 암사슴

- 효율적인

- 노력

- 수

- 조차

- 넘다

- 익숙한

- 빠른

- 최후의

- Find

- 흐름

- 럭셔리

- 에

- 이득

- 기하학

- 좋은

- 있다

- 호스팅

- 방법

- HTTPS

- i

- 개량

- in

- IT

- 되풀이

- 반복

- JPG

- 배우다

- 배우기

- 처럼

- 기계

- 기계 학습

- 조작

- 최대 폭

- 소개

- 회의

- 만족

- 방법

- ML

- 모델

- 이름

- of

- 낡은

- on

- 최적화

- 플라톤

- 플라톤 데이터 인텔리전스

- 플라토데이터

- 게시하다

- 힘

- 방법

- 생산력

- 장래가 촉망되는

- 문제

- 요구조건 니즈

- 결과

- 달리기

- 달리는

- 저금

- 비밀

- 영상을

- 시뮬레이션

- 크기

- 구체적인

- 지출

- 향신료

- 시작

- 회담

- 기술

- 그

- XNUMXD덴탈의

- 그들의

- 시간

- 에

- 너무

- 수단

- 트레이닝

- 유형

- 업데이트

- 사용

- 가치

- 확인

- 를 통해

- 방법..

- 웹 세미나

- 어느

- 의지

- 과

- 제퍼 넷