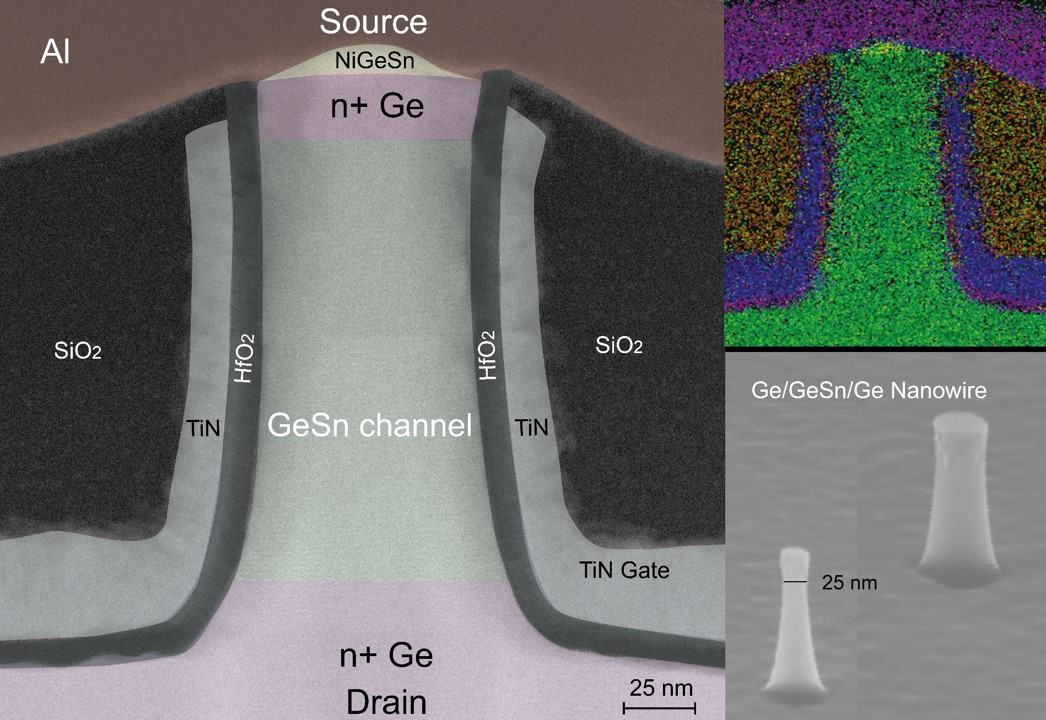

02 년 2023 월 XNUMX 일 (나노 워크 뉴스) CEA-Leti 연구 과학자들은 전자 및 기타 전하 캐리어가 실리콘이나 게르마늄보다 게르마늄 주석에서 더 빠르게 이동할 수 있어 평면 장치보다 수직에서 더 낮은 작동 전압과 더 작은 설치 공간을 가능하게 한다는 것을 입증했습니다. 이 개념 증명의 획기적인 발전은 게르마늄 주석으로 만들어진 수직형 트랜지스터가 미래의 저전력, 고성능 칩 및 양자 컴퓨터를 위한 유망한 후보라는 것을 의미합니다.

게르마늄-주석 트랜지스터 순수 게르마늄으로 만들어진 유사한 트랜지스터보다 2.5배 더 높은 전자 이동성을 나타냅니다. GeSn은 기존과 호환됩니다. CMOS 프로세스 칩 제조용. 게르마늄과 주석은 실리콘과 동일한 주기율표 그룹에서 나오므로 이러한 트랜지스터는 기존 생산 라인을 통해 기존 실리콘 칩에 직접 통합될 수 있습니다.

최근에 발표된 논문 통신 공학 (“실리콘을 넘어서는 CMOS용 수직형 GeSn 나노와이어 MOSFET”)는 “GeSn 합금은 Ge 및 SiGe가 포함된 에피택셜 헤테로구조에서 Sn 함량과 조정 가능한 밴드 오프셋을 변경하여 조정 가능한 에너지 밴드갭을 제공합니다. 실제로 최근 보고서에 따르면 Ge를 사용하는 경우0.92Sn0.08 Ge 나노와이어(NW) 상단의 소스로서 p-MOSFET 성능을 향상시킵니다.”

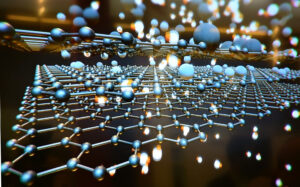

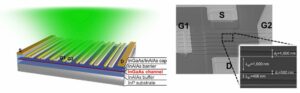

게르마늄-주석 트랜지스터의 전자 현미경 사진: 이 디자인은 최신 세대의 컴퓨터 프로세서에도 사용되는 3D 나노와이어 형상을 따릅니다. (이미지 : Forschungszentrum Jülich)

“전례 없는 전기 광학 특성 외에도 GeSn 바이너리의 주요 장점은 Si 및 SiGe 합금과 동일한 에피택시 반응기에서 성장할 수 있다는 것입니다. 이를 통해 단일체로 통합될 수 있는 모든 그룹 IV 광전자 반도체 플랫폼을 가능하게 합니다. Si”라고 신문은 보도합니다.

해당 프로젝트 연구에는 에피택셜 스택을 제공한 CEA-Leti 외에도 여러 조직의 기여가 포함되었습니다. 에피택시는 매우 정밀한 결정 구조를 지닌 매우 정돈된 템플릿인 실리콘 기판에서 수행됩니다. CEA-Leti는 재료를 변경하여 그 위에 놓인 층에 다이아몬드 결정 구조를 복제했습니다.

CEA 펠로우이자 팀 리더인 Jean-Michel Hartmann은 "에피택시는 원래 구조를 복제하여 다층을 만드는 기술이며 화학 기상 증착(CVD) 반응기에서 기체 전구체를 사용하여 저온에서 수행됩니다."라고 말했습니다. CEA-Leti에서 IV 에피택시.

이러한 종류의 스택을 증착하고 에피택셜 층 성장을 마스터하는 것은 패턴화된 실린더와 컨포멀 게이트 스택 증착이 필요한 프로세스 흐름에서 매우 복잡한 단계입니다. 즉, 전체 장치를 제조하는 것입니다. 복잡한 현장 도핑 Ge/GeSn 스택을 증착할 수 있는 세계적으로 몇 안 되는 RTO 중 하나인 CEA-Leti는 논문에 보고된 공동 연구의 해당 부분을 수행했습니다.

공동 저자인 Hartmann은 “이 협력은 채널의 높은 캐리어 이동도, 낮은 작동 전압 및 더 작은 설치 공간과 같은 흥미로운 전기적 특성을 가진 고급 트랜지스터에 대한 낮은 밴드갭 GeSn의 잠재력을 보여주었습니다.”라고 설명했습니다. “산업화는 아직 멀었습니다. 우리는 최첨단 기술을 발전시켜 채널 재료로서 게르마늄 주석의 잠재력을 보여주고 있습니다.”

이 작업에는 독일 ForschungsZentrum Jülich의 과학자도 포함되었습니다. 영국 리즈 대학교; IHP- 고성능 마이크로전자공학을 위한 혁신, 독일 프랑크푸르트(오데르) 및 독일 RWTH 아헨 대학교.

게르마늄-주석 트랜지스터의 전자 현미경 사진: 이 디자인은 최신 세대의 컴퓨터 프로세서에도 사용되는 3D 나노와이어 형상을 따릅니다. (이미지 : Forschungszentrum Jülich)

“전례 없는 전기 광학 특성 외에도 GeSn 바이너리의 주요 장점은 Si 및 SiGe 합금과 동일한 에피택시 반응기에서 성장할 수 있다는 것입니다. 이를 통해 단일체로 통합될 수 있는 모든 그룹 IV 광전자 반도체 플랫폼을 가능하게 합니다. Si”라고 신문은 보도합니다.

해당 프로젝트 연구에는 에피택셜 스택을 제공한 CEA-Leti 외에도 여러 조직의 기여가 포함되었습니다. 에피택시는 매우 정밀한 결정 구조를 지닌 매우 정돈된 템플릿인 실리콘 기판에서 수행됩니다. CEA-Leti는 재료를 변경하여 그 위에 놓인 층에 다이아몬드 결정 구조를 복제했습니다.

CEA 펠로우이자 팀 리더인 Jean-Michel Hartmann은 "에피택시는 원래 구조를 복제하여 다층을 만드는 기술이며 화학 기상 증착(CVD) 반응기에서 기체 전구체를 사용하여 저온에서 수행됩니다."라고 말했습니다. CEA-Leti에서 IV 에피택시.

이러한 종류의 스택을 증착하고 에피택셜 층 성장을 마스터하는 것은 패턴화된 실린더와 컨포멀 게이트 스택 증착이 필요한 프로세스 흐름에서 매우 복잡한 단계입니다. 즉, 전체 장치를 제조하는 것입니다. 복잡한 현장 도핑 Ge/GeSn 스택을 증착할 수 있는 세계적으로 몇 안 되는 RTO 중 하나인 CEA-Leti는 논문에 보고된 공동 연구의 해당 부분을 수행했습니다.

공동 저자인 Hartmann은 “이 협력은 채널의 높은 캐리어 이동도, 낮은 작동 전압 및 더 작은 설치 공간과 같은 흥미로운 전기적 특성을 가진 고급 트랜지스터에 대한 낮은 밴드갭 GeSn의 잠재력을 보여주었습니다.”라고 설명했습니다. “산업화는 아직 멀었습니다. 우리는 최첨단 기술을 발전시켜 채널 재료로서 게르마늄 주석의 잠재력을 보여주고 있습니다.”

이 작업에는 독일 ForschungsZentrum Jülich의 과학자도 포함되었습니다. 영국 리즈 대학교; IHP- 고성능 마이크로전자공학을 위한 혁신, 독일 프랑크푸르트(오데르) 및 독일 RWTH 아헨 대학교.

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- PlatoAiStream. Web3 데이터 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 미래 만들기 w Adryenn Ashley. 여기에서 액세스하십시오.

- PREIPO®로 PRE-IPO 회사의 주식을 사고 팔 수 있습니다. 여기에서 액세스하십시오.

- 출처: https://www.nanowerk.com/nanotechnology-news2/newsid=63102.php

- :있다

- :이다

- 10

- 3d

- 7

- 8

- 9

- a

- 할 수 있는

- 또한

- 조정

- 많은

- 전진하는

- 이점

- 또한

- an

- 와

- 있군요

- 미술

- AS

- At

- 떨어져

- 밴드

- BE

- 때문에

- 그 너머

- 돌파구

- by

- CAN

- 후보자

- 운반 된

- 캐리어

- 센터

- 변화

- 채널

- 요금

- 화학

- 칩

- 칩

- 공저자

- 협동

- 왔다

- 유사한

- 호환

- 복잡한

- 컴퓨터

- 컴퓨터

- 개념

- 함유량

- 기부금

- 전통적인

- 수

- Crystal

- 날짜

- 전달

- 시연

- 보여줍니다

- 예금

- 디자인

- 장치

- 디바이스

- 다이아몬드

- 직접

- 전자

- 가능

- 에너지

- 강화

- 전체의

- 전시회

- 현존하는

- 설명

- 매우

- 사실

- 멀리

- 빠른

- 사람

- 를

- 흐름

- 다음

- 발자국

- 럭셔리

- 에

- 미래

- ge

- 세대

- 기하학

- 독일

- 세계적으로

- 그룹

- 성장한

- 성장

- 있다

- 높은

- 고성능

- 더 높은

- HTTPS

- 영상

- in

- 포함

- 혁신

- 통합 된

- 흥미있는

- 으로

- IT

- 그

- 관절

- JPG

- 종류

- 왕국

- 최근

- 레이어

- 리더

- 라인

- 낮은

- 만든

- 주요한

- 유튜브 영상을 만드는 것은

- 제조

- 마스터

- 자료

- 방법

- 중간

- 유동성

- 움직임

- 노트

- of

- 제공

- on

- ONE

- 운영

- 조작

- or

- 조직

- 실물

- 기타

- 그렇지 않으면

- 아웃

- 서

- 부품

- 성능

- 공연

- 수행

- 주기

- PHP

- 플랫폼

- 플라톤

- 플라톤 데이터 인텔리전스

- 플라토데이터

- 혹시

- 가능성

- 정확한

- 방법

- 가공업자

- 생산

- 프로젝트

- 장래가 촉망되는

- 증명

- 개념 증명

- 속성

- 출판

- 놓다

- 양자 컴퓨팅

- 양자 컴퓨터

- 최근

- 최근에

- 신고

- 보고

- 보고서

- 연구

- 말했다

- 같은

- 과학자

- 반도체

- 몇몇의

- 짧은

- 표시

- 규소

- 작은

- 출처

- 스택

- 스택

- 주 정부

- 단계

- 아직도

- 구조

- 이러한

- 테이블

- 팀

- 이 템플릿

- 보다

- 그

- XNUMXD덴탈의

- 관절

- 국가

- 그들의

- Bowman의

- 그들

- 이

- 시대

- 에

- 상단

- 미국

- 영국

- 대학

- 전례가없는

- 사용

- 익숙한

- 수직선

- 대단히

- we

- 어느

- 과

- 작업

- 제퍼 넷