27년 2023월 XNUMX일(나노 워크 뉴스) 신흥 인공 지능 인간의 자연스러운 언어를 생성하는 챗봇과 같은 (AI) 애플리케이션은 더 조밀하고 강력한 컴퓨터 칩을 요구합니다. 그러나 반도체 칩은 전통적으로 상자 모양의 3D 구조인 벌크 재료로 만들어지므로 더 조밀한 통합을 만들기 위해 여러 층의 트랜지스터를 적층하는 것은 매우 어렵습니다. 그러나 반도체 트랜지스터 초박형으로 만든 2D 재료각각 두께가 약 2개의 원자인 , 더 강력한 칩을 만들기 위해 쌓일 수 있습니다. 이를 위해 MIT 연구원들은 이제 효과적이고 효율적으로 XNUMXD 레이어를 "성장"할 수 있는 새로운 기술을 시연했습니다. 전이금속 디칼코게나이드 (TMD) 재료를 완전히 제작된 실리콘 칩 위에 직접 배치하여 더 조밀한 통합을 가능하게 합니다. 실리콘 CMOS 웨이퍼에 직접 2D 재료를 성장시키는 것은 프로세스가 일반적으로 섭씨 약 600도의 온도를 필요로 하는 반면 실리콘 트랜지스터와 회로는 400도 이상으로 가열될 때 파손될 수 있기 때문에 주요 과제를 제기했습니다. 이제 MIT 연구원의 학제간 팀은 칩을 손상시키지 않는 저온 성장 프로세스를 개발했습니다. 이 기술을 통해 2D 반도체 트랜지스터를 표준 실리콘 회로 위에 직접 통합할 수 있습니다. 과거에 연구원들은 다른 곳에서 2D 재료를 성장시킨 다음 칩이나 웨이퍼로 옮겼습니다. 이로 인해 종종 최종 장치 및 회로의 성능을 방해하는 결함이 발생합니다. 또한 웨이퍼 스케일에서는 재료를 원활하게 이송하는 것이 매우 어려워집니다. 대조적으로 이 새로운 프로세스는 전체 8인치 웨이퍼에 걸쳐 매끄럽고 매우 균일한 레이어를 성장시킵니다. 새로운 기술은 또한 이러한 재료를 성장시키는 데 걸리는 시간을 크게 줄일 수 있습니다. 이전 접근 방식은 2D 재료의 단일 레이어를 성장시키는 데 하루 이상이 필요했지만 새로운 접근 방식은 전체 8인치 웨이퍼에서 2시간 이내에 TMD 재료의 균일한 레이어를 성장시킬 수 있습니다. 빠른 속도와 높은 균일성으로 인해 연구원들은 이전에 시연된 것보다 훨씬 더 큰 표면에 8D 재료 층을 성공적으로 통합할 수 있었습니다. 이것은 그들의 방법이 2인치 이상의 웨이퍼가 핵심인 상업적 응용 분야에서 사용하기에 더 적합하도록 만듭니다. “2D 재료를 사용하는 것은 집적 회로의 밀도를 높이는 강력한 방법입니다. 우리가 하는 일은 다층 건물을 짓는 것과 같습니다. 기존의 경우와 같이 XNUMX층만 있으면 많은 사람을 수용할 수 없습니다. 그러나 더 많은 층으로 인해 건물은 놀라운 새로운 것을 가능하게 할 수 있는 더 많은 사람들을 수용할 것입니다. 우리가 작업하고 있는 이기종 통합 덕분에 XNUMX층에 실리콘이 있고 그 위에 직접 통합된 XNUMXD 재료의 여러 층을 가질 수 있습니다.”라고 전기 공학 및 컴퓨터 과학 대학원생이자 공동 저자인 Jiadi Zhu는 말합니다. 이 새로운 기술에 대한 논문의

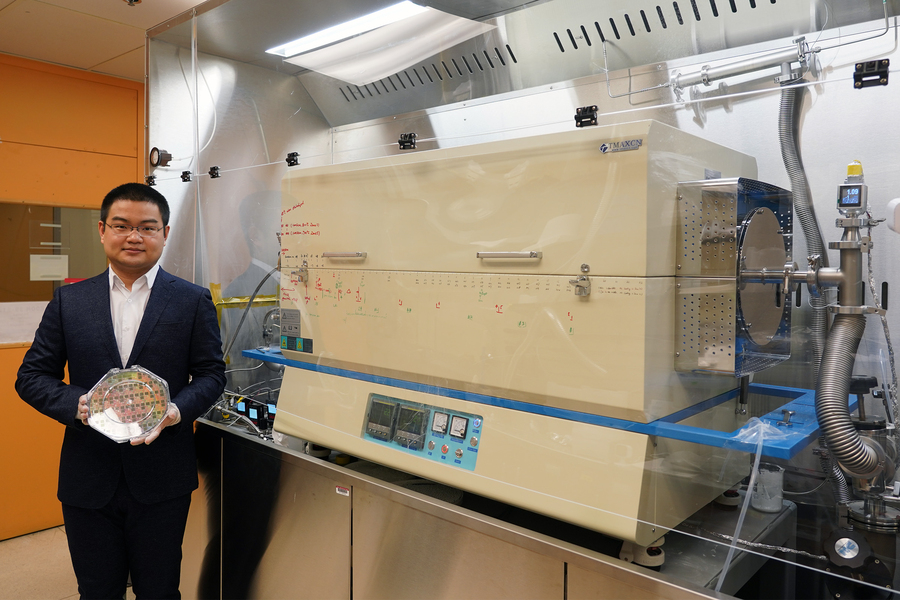

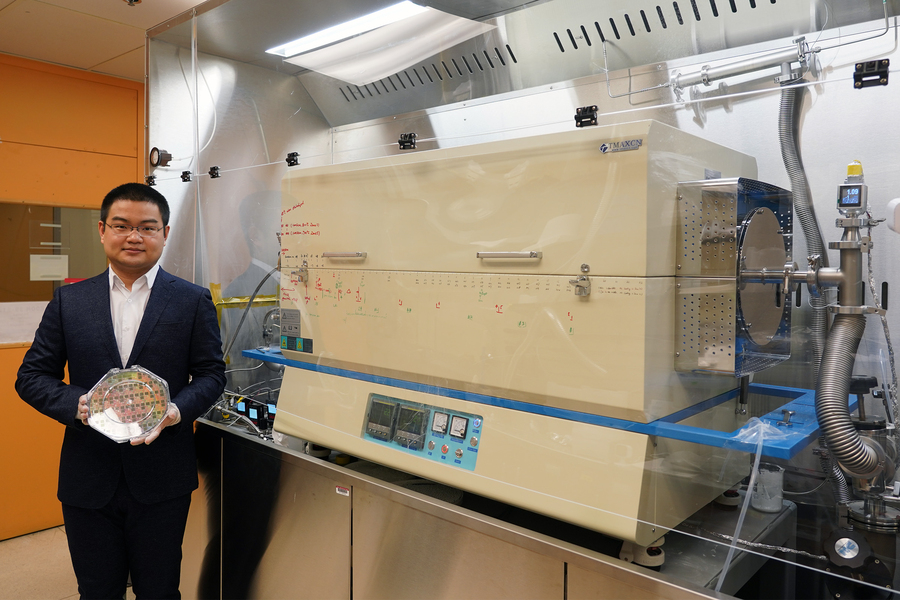

이황화 몰리브덴 박막이 있는 8인치 CMOS 웨이퍼를 들고 있는 대학원생 Jiadi Zhu. 오른쪽에는 웨이퍼를 손상시키지 않는 저온 공정을 사용하여 웨이퍼 위에 몰리브덴 이황화물 층을 "성장"할 수 있도록 연구원들이 개발한 용광로가 있습니다. (이미지: MIT) Zhu는 MIT 박사후 연구원인 공동 저자인 박지훈과 함께 논문을 작성했습니다. 교신 저자인 Jing Kong, 전기 공학 및 컴퓨터 과학(EECS) 교수이자 전자 연구소 회원; EECS 교수이자 MTL(Microsystems Technology Laboratories) 이사인 Tomás Palacios; 뿐만 아니라 MIT, MIT Lincoln 연구소, Oak Ridge 국립 연구소 및 Ericsson Research의 다른 사람들도 있습니다. 에 종이가 나타납니다. 자연 나노 기술 ("200mm 플랫폼에서 실리콘 백엔드 통합을 위한 단층 몰리브덴 이황화물의 저열 예산 합성").

이황화 몰리브덴 박막이 있는 8인치 CMOS 웨이퍼를 들고 있는 대학원생 Jiadi Zhu. 오른쪽에는 웨이퍼를 손상시키지 않는 저온 공정을 사용하여 웨이퍼 위에 몰리브덴 이황화물 층을 "성장"할 수 있도록 연구원들이 개발한 용광로가 있습니다. (이미지: MIT) Zhu는 MIT 박사후 연구원인 공동 저자인 박지훈과 함께 논문을 작성했습니다. 교신 저자인 Jing Kong, 전기 공학 및 컴퓨터 과학(EECS) 교수이자 전자 연구소 회원; EECS 교수이자 MTL(Microsystems Technology Laboratories) 이사인 Tomás Palacios; 뿐만 아니라 MIT, MIT Lincoln 연구소, Oak Ridge 국립 연구소 및 Ericsson Research의 다른 사람들도 있습니다. 에 종이가 나타납니다. 자연 나노 기술 ("200mm 플랫폼에서 실리콘 백엔드 통합을 위한 단층 몰리브덴 이황화물의 저열 예산 합성").

이황화 몰리브덴 박막이 있는 8인치 CMOS 웨이퍼를 들고 있는 대학원생 Jiadi Zhu. 오른쪽에는 웨이퍼를 손상시키지 않는 저온 공정을 사용하여 웨이퍼 위에 몰리브덴 이황화물 층을 "성장"할 수 있도록 연구원들이 개발한 용광로가 있습니다. (이미지: MIT) Zhu는 MIT 박사후 연구원인 공동 저자인 박지훈과 함께 논문을 작성했습니다. 교신 저자인 Jing Kong, 전기 공학 및 컴퓨터 과학(EECS) 교수이자 전자 연구소 회원; EECS 교수이자 MTL(Microsystems Technology Laboratories) 이사인 Tomás Palacios; 뿐만 아니라 MIT, MIT Lincoln 연구소, Oak Ridge 국립 연구소 및 Ericsson Research의 다른 사람들도 있습니다. 에 종이가 나타납니다. 자연 나노 기술 ("200mm 플랫폼에서 실리콘 백엔드 통합을 위한 단층 몰리브덴 이황화물의 저열 예산 합성").

이황화 몰리브덴 박막이 있는 8인치 CMOS 웨이퍼를 들고 있는 대학원생 Jiadi Zhu. 오른쪽에는 웨이퍼를 손상시키지 않는 저온 공정을 사용하여 웨이퍼 위에 몰리브덴 이황화물 층을 "성장"할 수 있도록 연구원들이 개발한 용광로가 있습니다. (이미지: MIT) Zhu는 MIT 박사후 연구원인 공동 저자인 박지훈과 함께 논문을 작성했습니다. 교신 저자인 Jing Kong, 전기 공학 및 컴퓨터 과학(EECS) 교수이자 전자 연구소 회원; EECS 교수이자 MTL(Microsystems Technology Laboratories) 이사인 Tomás Palacios; 뿐만 아니라 MIT, MIT Lincoln 연구소, Oak Ridge 국립 연구소 및 Ericsson Research의 다른 사람들도 있습니다. 에 종이가 나타납니다. 자연 나노 기술 ("200mm 플랫폼에서 실리콘 백엔드 통합을 위한 단층 몰리브덴 이황화물의 저열 예산 합성").

잠재력이 큰 슬림 소재

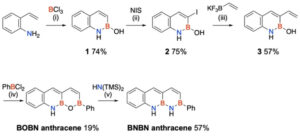

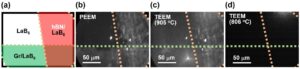

연구원들이 집중한 2D 재료인 이황화 몰리브덴은 유연하고 투명하며 반도체 트랜지스터에 이상적인 강력한 전자 및 광자 특성을 나타냅니다. 그것은 두 개의 황화물 원자 사이에 끼인 몰리브덴의 원자 550개 층으로 구성됩니다. 우수한 균일성으로 표면에 이황화 몰리브덴 박막을 성장시키는 것은 종종 금속-유기 화학 기상 증착(MOCVD)으로 알려진 프로세스를 통해 이루어집니다. 몰리브덴과 황 원자를 포함하는 두 가지 유기 화합물인 몰리브덴 헥사카보닐과 디에틸렌 황은 기화되고 반응 챔버 내부에서 가열되어 더 작은 분자로 "분해"됩니다. 그런 다음 화학 반응을 통해 연결되어 표면에 이황화 몰리브덴 사슬을 형성합니다. 그러나 전구체로 알려진 이러한 몰리브덴 및 황 화합물을 분해하려면 섭씨 400도 이상의 온도가 필요하며 실리콘 회로는 온도가 400도를 초과하면 성능이 저하되기 시작합니다. 그래서 연구원들은 틀 밖에서 생각하는 것부터 시작했습니다. 그들은 금속-유기 화학 기상 증착 공정을 위한 완전히 새로운 용광로를 설계하고 제작했습니다. 오븐은 실리콘 웨이퍼가 놓이는 전면의 저온영역과 후면의 고온영역의 XNUMX개의 챔버로 구성되어 있다. 기화된 몰리브덴 및 황 전구체가 용광로로 펌핑됩니다. 몰리브덴은 온도가 섭씨 XNUMX도 미만으로 유지되는 저온 영역에 머문다. 몰리브덴 전구체를 분해할 수 있을 만큼 충분히 뜨겁지만 실리콘 칩을 손상시킬 정도로 뜨겁지는 않다. 황 전구체는 분해되는 고온 영역으로 흐릅니다. 그런 다음 웨이퍼 표면에 이황화 몰리브덴을 성장시키는 화학 반응이 일어나는 저온 영역으로 다시 흐릅니다. “검은 후추를 만드는 것과 같은 분해에 대해 생각할 수 있습니다. 전체 후추를 가지고 가루 형태로 갈아서 만듭니다. 그래서 고온 영역에서 고추를 부수고 갈아서 가루가 다시 저온 영역으로 흐릅니다.”라고 Zhu는 설명합니다.더 빠른 성장 및 더 나은 균일성

이 프로세스의 한 가지 문제는 실리콘 회로가 일반적으로 알루미늄 또는 구리를 최상층으로 사용하여 칩이 인쇄 회로 기판에 장착되기 전에 패키지 또는 캐리어에 연결될 수 있다는 것입니다. 그러나 황은 일부 금속이 산소에 노출되었을 때 녹이 슬어 전도도를 파괴하는 것과 같은 방식으로 이러한 금속을 황화시킵니다. 연구원들은 먼저 칩 위에 매우 얇은 패시베이션 재료 층을 증착하여 황화를 방지했습니다. 그런 다음 나중에 패시베이션 레이어를 열어 연결을 만들 수 있습니다. 그들은 또한 수평이 아닌 수직으로 용광로의 저온 영역에 실리콘 웨이퍼를 배치했습니다. 수직으로 놓으면 양쪽 끝이 고온 영역에 너무 가깝지 않아 웨이퍼의 어떤 부분도 열에 의해 손상되지 않습니다. 또한 몰리브덴과 유황 가스 분자는 수평 표면 위로 흐르지 않고 수직 칩에 부딪히면서 소용돌이칩니다. 이 순환 효과는 이황화 몰리브덴의 성장을 개선하고 재료 균일성을 향상시킵니다. 보다 균일한 층을 생성하는 것 외에도 그들의 방법은 다른 MOCVD 프로세스보다 훨씬 빠릅니다. 일반적으로 MOCVD 성장 프로세스는 적어도 하루 종일 걸리는 반면, 그들은 8시간 이내에 레이어를 성장시킬 수 있습니다. 최첨단 MIT.Nano 시설을 사용하여 그들은 2인치 실리콘 웨이퍼에 걸쳐 높은 재료 균일성과 품질을 입증할 수 있었는데, 이는 더 큰 웨이퍼가 필요한 산업 응용 분야에 특히 중요합니다. “성장 시간을 단축함으로써 프로세스가 훨씬 더 효율적이고 산업 제작에 더 쉽게 통합될 수 있습니다. 또한 이것은 실리콘과 호환되는 저온 공정으로 2D 재료를 반도체 산업으로 더욱 발전시키는 데 유용할 수 있습니다.”라고 Zhu는 말합니다. 미래에 연구원들은 기술을 미세 조정하고 이를 사용하여 8D 트랜지스터의 많은 적층 레이어를 성장시키기를 원합니다. 또한 그들은 폴리머, 직물 또는 심지어 종이와 같은 유연한 표면을 위한 저온 성장 공정의 사용을 탐구하기를 원합니다. 이를 통해 옷이나 노트북과 같은 일상적인 물건에 반도체를 통합할 수 있습니다. "이 연구는 단층 몰리브덴 이황화물 재료의 합성 기술에서 중요한 진전을 이루었습니다. 이 연구에 참여하지 않은 University of Southern California. "XNUMX인치 스케일에서 낮은 열 예산 증가의 새로운 기능은 이 소재와 실리콘 CMOS 기술의 백엔드 통합을 가능하게 하고 미래의 전자 응용 분야를 위한 길을 열어줍니다."- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- PlatoAiStream. Web3 데이터 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 미래 만들기 w Adryenn Ashley. 여기에서 액세스하십시오.

- 출처: https://www.nanowerk.com/nanotechnology-news2/newsid=62907.php

- :있다

- :이다

- :아니

- :어디

- $UP

- 10

- 11

- 200

- 27

- 2D

- 2D 재료

- 3d

- 7

- 8

- 9

- a

- 할 수 있는

- 소개

- 위의

- 달성

- 가로질러

- 또한

- AI

- 수

- 또한

- 놀라운

- an

- 및

- 어플리케이션

- 어플리케이션

- 접근

- 구혼

- 있군요

- 약

- AS

- 준

- At

- 저자

- 작성자

- 뒤로

- BE

- 때문에

- 된다

- 된

- 전에

- 이하

- 더 나은

- 사이에

- 더 큰

- 검정

- 판

- 보물상자

- 흩어져

- 예산

- 건물

- 내장

- 비자 면제 프로그램에 해당하는 국가의 시민권을 가지고 있지만

- by

- 캘리포니아

- CAN

- 채용

- 케이스

- 원인

- 섭씨

- 센터

- 쇠사슬

- 의장

- 도전

- 방

- 잡담

- 화학

- 칩

- 칩

- 순환

- 닫기

- 의류

- 상업

- 구성

- 컴퓨터

- 컴퓨터 공학

- 컴퓨터 과학

- 전도도

- 연결

- 연결

- 건설 중의

- 대조

- 전통적인

- 구리

- 동

- 수

- 만들

- 날짜

- 일

- 수요

- 보여

- 시연

- density

- 설계

- 개발

- 디바이스

- DID

- 어려운

- 직접

- 책임자

- 하지

- 하기

- 아래 (down)

- 두

- 마다

- 초기의

- 용이하게

- 효과

- 효과적으로

- 효율적인

- 효율적으로

- 전기 공학

- 전자

- 전자

- 다른

- 신흥

- 가능

- 사용 가능

- 수

- end

- 엔지니어링

- 엔지니어

- 충분히

- 전체의

- 전적으로

- 에릭슨

- 특히

- 조차

- 일상의

- 전시

- 설명

- 탐험

- 드러난

- 매우

- 시설

- 빠른

- Film

- 영화

- 최후의

- 먼저,

- 융통성있는

- 바닥

- 층

- 흐르는

- 흐름

- 집중

- 럭셔리

- 형태

- 에

- 앞

- 충분히

- 추가

- 미래

- 가스

- 생성

- 좋은

- 졸업

- 성장

- 성장하는

- 성장한

- 성장

- 성장

- 있다

- 높은

- 고도로

- 보유

- 보유

- 수평

- 뜨거운

- 그러나

- HTTPS

- 사람의

- 이상

- if

- 영상

- 중대한

- 향상

- in

- 인치

- 증가

- 산업

- 산업

- 통합

- 통합 된

- 완성

- 통합

- 으로

- 참여

- IT

- 그

- JPG

- 키

- 알려진

- 홍콩

- 실험실

- 레인

- 언어

- 큰

- 후에

- 층

- 레이어

- 오퍼

- 처럼

- 링컨

- LINK

- 낮은

- 만든

- 주요한

- 확인

- 제작

- 유튜브 영상을 만드는 것은

- .

- 많은 사람

- 자료

- 재료

- 회원

- 금속

- 금속

- 방법

- 중간

- MIT

- 배우기

- 보다 효율적으로

- MTL

- 많은

- 여러

- 나노

- 국가의

- 자연의

- 필요

- ...도 아니고 ...도 아니다

- 신제품

- 아니

- 노트북

- 소설

- 지금

- 오크 나무

- 오크 리지 국립 연구소

- 사물

- of

- 자주

- on

- ONE

- 만

- 열 수

- or

- 유기적인

- 기타

- 기타

- 외부

- 위에

- 산소

- 꾸러미

- 서

- 서류

- 공원

- 부품

- 과거

- 사람들

- 성능

- PHP

- 자본 매출

- 플랫폼

- 플라톤

- 플라톤 데이터 인텔리전스

- 플라토데이터

- ...을 더한

- 폴리머

- 강한

- 전구 물질

- 너무 이른

- 이전에

- 문제

- 방법

- 프로세스

- 교수

- 진행

- 속성

- 푸시

- 품질

- 빠른

- 차라리

- 반응

- 반응

- 감소

- 지방

- 필수

- 필요

- 연구

- 연구원

- ROBERT

- 녹

- 같은

- 라고

- 규모

- 과학

- 반도체

- 반도체

- 크게

- 규소

- 단일

- 작은

- 스매시

- 원활하게

- So

- 일부

- 남쪽의

- 속도

- 쌓인

- 스태킹

- 표준

- 스타트

- 시작

- 최첨단

- 학생

- 성공적으로

- 표면

- 능가

- 소요

- 팀

- Technology

- 섬유

- 보다

- 감사

- 그

- XNUMXD덴탈의

- 미래

- 그들의

- 그들

- 그때

- 열의

- Bowman의

- 그들

- 일

- 생각

- 사고력

- 이

- 세

- 을 통하여

- 시간

- 에

- 너무

- 상단

- 전통적으로

- 전송

- 전송

- 투명한

- 두

- 일반적으로

- 대학

- University of Southern California

- 사용

- 사용

- 보통

- 거대한

- 수직으로

- 대단히

- 필요

- 였다

- 방법..

- we

- 잘

- 했다

- 뭐

- 언제

- 어느

- 동안

- 누구

- 의지

- 과

- 작업

- 일하는

- 항복

- 당신

- 제퍼 넷