더 작은 DRAM 셀 크기에 대한 추구는 여전히 활발하고 진행 중입니다. DRAM 셀 크기는 D0.0013 노드의 경우 2um12에 접근할 것으로 예상됩니다. DUV 또는 EUV 리소그래피 사용을 고려할 때 패터닝 문제는 중요합니다. 특히 ASML에서는 중심 간 값이 40nm에 도달하면 EUV에서도 단일 패터닝이 권장되지 않을 것이라고 보고했습니다[1]. 이 기사에서는 12nm DRAM 노드 이상의 경우 커패시터 중심 간이 40nm 미만으로 낮아질 것으로 예상되므로 다중 패턴화가 필요함을 보여줍니다.

저장 커패시터용 DRAM 셀 레이아웃

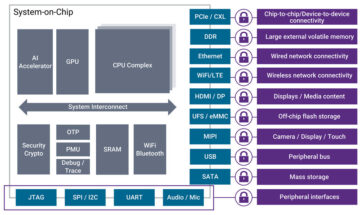

저장 커패시터는 육각형 배열로 배열됩니다(그림 1). 활성 영역 디자인 규칙은 비트 라인 피치와 워드 라인 피치에 의해 결정됩니다[2].

그림 1. DRAM 셀 그리드의 스토리지 노드(노란색) BLP=비트 라인 피치, WLP=워드 라인 피치.

38nm 비트 라인 피치와 33nm 워드 라인 피치는 38um32.9의 셀 크기와 0.001254nm 활성 영역 설계 규칙 바로 아래에 대해 중심 간 2nm 및 대각선 간 피치 12nm로 이어집니다.

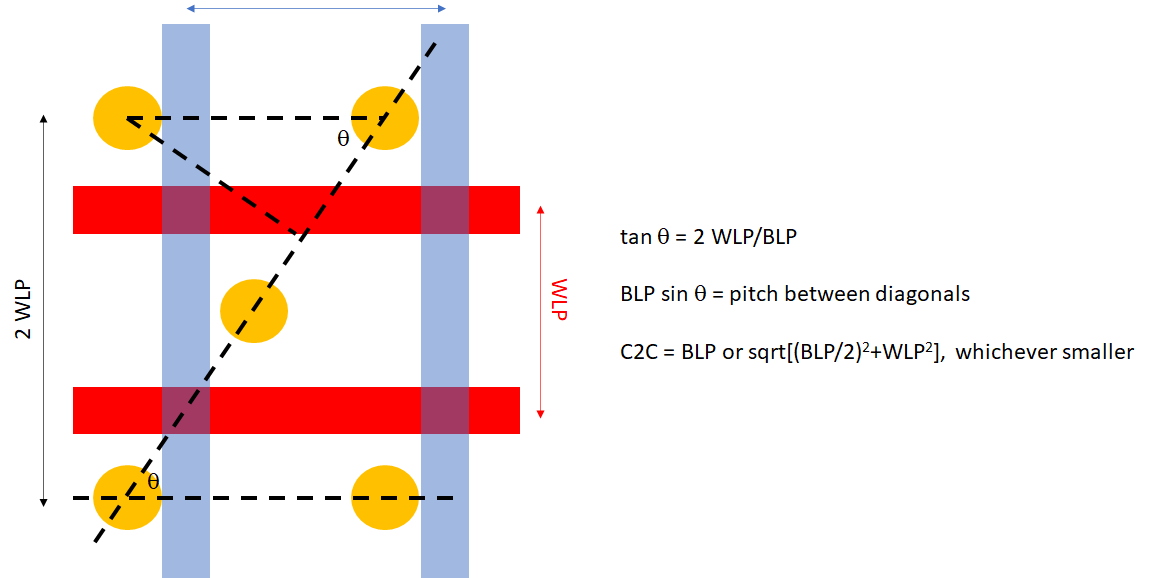

0.33 NA EUV 시스템의 경우 육각형 어레이는 2극 조명을 사용하며, 각 극은 XNUMX빔 간섭 패턴을 생성합니다(그림 XNUMX). XNUMX개의 사분면 극은 다른 두 개의 수평 극과 다른 패턴을 생성합니다. 이는 별도의 확률론을 갖는 두 개의 별도 선량 구성요소로 이어집니다. 이는 최종 복합 패턴에 추가됩니다.

그림 2. DRAM 스토리지 패턴을 위한 헥사폴 조명은 4개의 사분면 극(회색)과 XNUMX개의 수평 극(노란색)으로 구성됩니다. 조명 방향에 따라 결과적인 XNUMX빔 간섭 패턴은 특정 방향을 갖습니다.

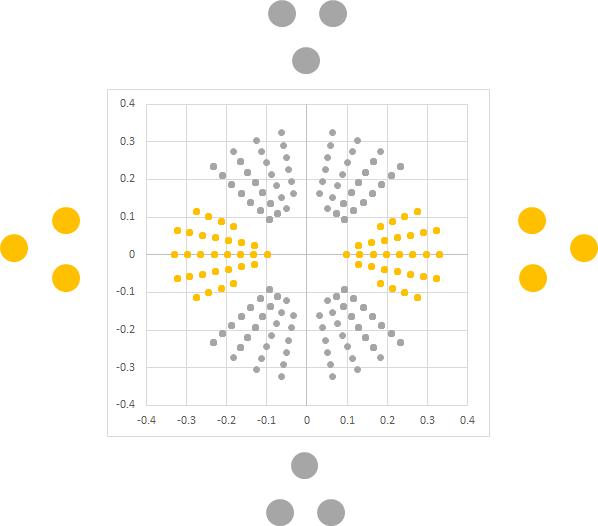

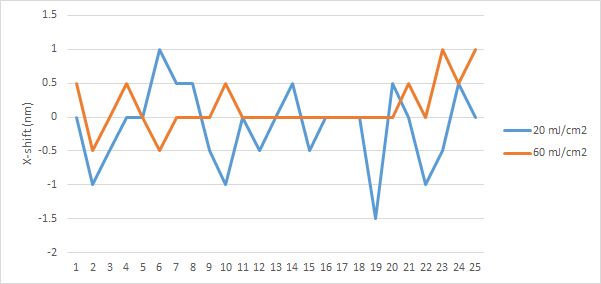

피처 가장자리에서 상당한 흡수된 광자 샷 노이즈로 인해 Ref.에서 이미 공개된 것처럼 패턴 배치 오류에 대한 확률론적 영향이 중요합니다. 1, 1nm 오버레이 사양을 쉽게 초과합니다. 낮은 흡수선량은 분명히 더 나쁜 것으로 보입니다(그림 3).

그림 3. 38 NA EUV 시스템에서 예상되는 66극 조명을 사용하는 33nm x 0.33nm 단위 셀(워드 라인 피치 = 25nm)의 중심 기둥의 확률적 배치 오류(X만). 여기에는 두 가지 흡수선량에 대한 일련의 XNUMX가지 사례가 나와 있습니다.

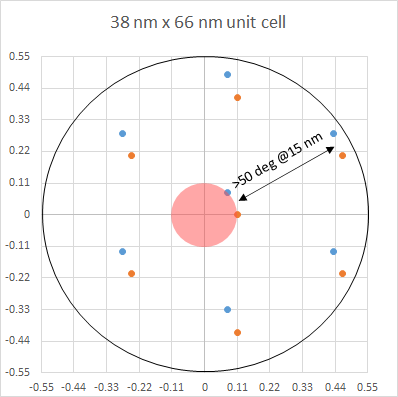

NA가 0.55로 증가하면 초점 심도가 심각하게 감소하는 문제가 추가됩니다. NA가 0.55이면 15nm 디포커스가 발생하여 가장 안쪽 회절 차수와 가장 바깥쪽 회절 차수 사이에서 50도 이상의 위상 이동이 발생하고(그림 4), 페이딩으로 인해 이미지 대비가 심각하게 감소합니다[3].

그림 4. 15 NA EUV 시스템의 0.55nm 디포커스로 인해 가장 안쪽 회절 차수와 가장 바깥쪽 회절 차수 사이에 50도 이상의 위상 변이가 발생합니다.

따라서 스토리지 노드 패턴은 두 개의 교차된 라인 패턴으로 형성되어야 할 가능성이 높습니다(그림 5). 각각의 교차된 라인 패턴은 EUV 단일 노출 또는 DUV SAQP(Self-Aligned Quadruple Patterning)에 의해 형성될 수 있습니다. 두 옵션 모두 단일 마스크 프로세스입니다. SAQP 프로세스는 더 성숙하고(EUV보다 오래 전부터) EUV의 4차 전자 확률론적 우려가 없으므로 선호되어야 합니다. 그러나 SAQP의 경우 스페이서 라인은 배치 및 선폭 거칠기 측면에서 잘 제어되어야 합니다[5].

그림 5. 저장 노드 패턴은 두 개의 교차된 선 패턴이 교차하여 형성될 수 있습니다.

라인형 SAQP 대신에 삼성[2]에서는 출발선 패턴이 있는 두 개의 마스크 대신 시작 벌집 패턴이 있는 단일 마스크를 활용하는 6D 스페이서 벌집 패터닝도 시연했습니다.

위의 경우는 38nm 비트라인 피치와 33nm 워드라인 피치를 고려하였지만, 육각형 대칭으로 인해 피치가 서로 바뀌는 경우(33nm 비트라인 피치와 38nm 워드라인 피치)에도 적용됩니다.

참고자료

[1] W. Gao 등, Proc. SPIE 11323, 113231L(2020).

[2] F. Chen, DRAM 셀 피치 간의 삼각 관계, https://www.youtube.com/watch?v=Oq6b-6iw6Zk

[3] JH. Franke, TA Brunner, E. Hendrickx, J. 마이크로/나노패턴. 교배. 메트로. 21, 030501(2022).

[4] F. Chen, EUV 확률적 결함의 근원으로서의 XNUMX차 전자 흐림 무작위성, https://www.linkedin.com/pulse/secondary-electron-blur-randomness-origin-euv-stochastic-chen/

[5] N. Bae et al., Proc. SPIE 11615, 116150B(2021).

[6] JM Park 외, IEDM 2015.

이 기사는 LinkedIn Pulse에 처음 등장했습니다. 응용 분야별 리소그래피: Sub-0.0013um2 DRAM 스토리지 노드 패터닝

다음을 통해이 게시물 공유 :

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- 플라토 블록체인. Web3 메타버스 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 출처: https://semiwiki.com/lithography/323357-application-specific-lithography-sub-0-0013-um2-dram-storage-node-patterning/

- 1

- 2020

- 2021

- 2022

- 9

- a

- 위의

- 활동적인

- 추가

- 추가

- 이미

- 중

- 및

- 등장

- 어플리케이션

- 특정 응용 프로그램

- 접근

- 지역

- 배열 된

- 배열

- 기사

- 이하

- 사이에

- 그 너머

- 비트

- 흐림

- 케이스

- 중심적인

- 과제

- 첸

- 구성 요소들

- 우려 사항

- 고려

- 치고는

- 대조

- 교차

- 시연

- 의존

- 깊이

- 디자인

- 결정된

- 다른

- 방향

- 마다

- 용이하게

- Edge

- 효과

- 오류

- 조차

- EVER

- 기대하는

- 노출 시간

- 특색

- 그림

- 최후의

- 먼저,

- 초점

- 형성

- 무료

- 에

- GAO

- Go

- 그리드

- 데

- 여기에서 지금 확인해 보세요.

- 수평

- HTTPS

- 영상

- in

- 를 받아야 하는 미국 여행자

- 교차

- 발행물

- IT

- 레이아웃

- 리드

- 지도

- 오퍼

- 아마도

- 라인

- 라인

- 링크드인

- 긴

- 마스크

- 마스크

- 성숙한

- 최대 폭

- 배우기

- 요구

- 노드

- 노드

- 노이즈

- 지속적으로

- 옵션

- 명령

- 유래

- 기타

- 공원

- 특별한

- 무늬

- 패턴

- 상

- 기둥

- 피치

- 피치

- 플라톤

- 플라톤 데이터 인텔리전스

- 플라토데이터

- 게시하다

- 선호하는

- PROC

- 방법

- 프로세스

- 생산

- 돌출한

- 펄스

- 무작위성

- 도달

- 추천

- 감소

- 감소

- 관계

- 보고

- 결과

- 결과

- 통치

- 삼성

- 보조

- 연속

- 변화

- 영상을

- 표시

- 표시

- 상당한

- 단일

- 크기

- 크기

- 작은

- So

- 구체적인

- 시작 중

- 아직도

- 저장

- 실질적인

- 체계

- 조건

- XNUMXD덴탈의

- 따라서

- 에

- 아래에

- 단위

- 사용

- 활용

- 마케팅은:

- 를 통해

- W

- 여부

- 어느

- 의지

- 워드

- 겠지

- X

- 유튜브

- 제퍼 넷