지난 달 연례 국제전자소자회의(IEDM)가 열렸습니다. 단기 과정의 프레젠테이션 중 하나는 Intel의 Matthew Metz가 진행한 것이었습니다. 무어의 법칙 지속을 위한 새로운 재료 시스템. 본질적으로 이것은 실리콘이 고갈된 후에 어떤 일이 일어날지에 대한 몇 가지 가능성을 살펴보는 것이었습니다.

![]()

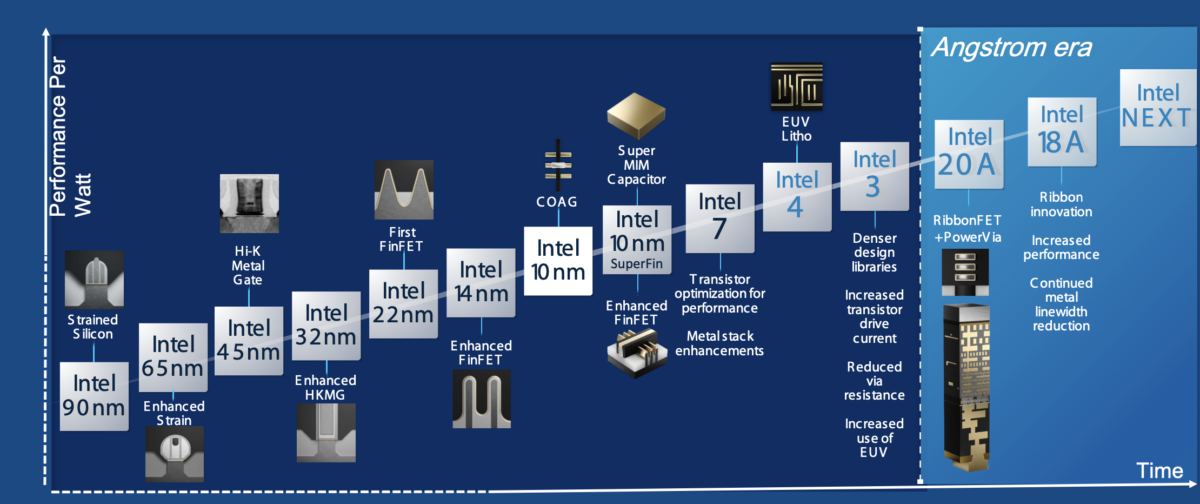

Matthew는 트랜지스터가 어떻게 세상을 변화시켰는지 살펴보는 것부터 시작했으며, 특히 수십 년 동안 Intel의 자체 프로세스 로드맵을 주도한 재료 혁신에 대해 살펴보았습니다. 90nm에서는 변형된 실리콘이 있었고 그 다음에는 HiK 금속 게이트가 있었습니다. Intel은 FinFET를 최초로 시장에 출시했습니다(당시에는 TriGate라고 불렀지만). Intel 4에서는 EUV 리소그래피가 처음 도입되었습니다.

![]()

아시다시피 인텔은 5년 동안 4개 프로세스의 기술 개발을 진행하고 있습니다. 이는 분명히 공격적이지만 여전히 모든 것이 순조롭게 진행되고 있는 것 같습니다. Intel 20A는 Intel이 RibbonFET이라고 부르는 GAA(Gate-All-Around)를 사용한 최초의 프로세스가 될 것입니다. 인텔도 공격적인 고급 패키징 로드맵을 가지고 있지만 대화의 초점은 웨이퍼를 어떻게 조립할 것인지가 아니라 미래에 웨이퍼에 무엇을 넣을 것인지였기 때문에 건너뛰겠습니다.

![]()

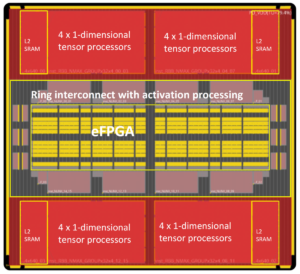

인텔만이 전면적인 접근을 시도하는 것은 아닙니다. 지난 몇 년 동안 IEDM과 같은 컨퍼런스에서 모든 주요 제조업체 및 연구 기관은 나노시트 게이트 전체 결과의 일부 버전을 발표했습니다. 위의 단면을 참조하세요.

계획된 다음의 큰 혁신은 p-트랜지스터 위에 n-트랜지스터를 사용하는 보완형 FET 또는 CFET입니다. 실제로 이것은 많은 사람들이 1.5배에서 2배의 면적 확장을 위해 CFET 제조에 대한 다양한 혁신을 발표하면서 올해 IEDM의 거의 주제였습니다.

![]()

Intel이 (다른 모든 사람들과 함께) 추구하고 있는 또 다른 혁신은 Intel이 PowerVia라고 부르는 것과 함께 뒷면 전력 공급 네트워크(뒷면 PDN)입니다. 이러한 기술을 사용하면 신호와 전원을 분리할 수 있으며 역사적으로 모든 상호 연결이 전면(최근까지 유일한 측면)에 있었던 경우처럼 더 이상 서로 간섭하지 않습니다.

가장 큰 과제는 전력 벽이다. 제곱센티미터당 100W 이상의 냉각 성능을 얻는 것은 매우 어렵습니다. 상황을 개선하는 방법에는 다양한 가능성이 있습니다.

- 기존 MOSFET 향상

- 변형된 실리콘 게르마늄(SiGe) 나노리본

- Ge 또는 InGaAs 나노리본

- 터널 FET

- Dirac FET(그래핀 및 2D)

- 네거티브 커패시턴스 NCFET

- FerroTunnel Junction 또는 FerroFET를 사용한 인메모리 컴퓨팅

![]()

2D에 집착하지 않고 3D 소재를 만드는 것에는 매력이 많습니다. 그러나 좋은 재료를 찾는 데에는 큰 어려움이 있습니다. 탄소 나노튜브(CNT)에 대해 들어보셨을 거라 확신합니다. 하지만 이러한 매력에도 불구하고 2년 동안 이를 안정적으로 제조하려는 과제에는 실질적인 진전이 없었습니다. 그래핀은 XNUMXD이지만 밴드갭이 없어 스위치를 만드는 것이 어렵습니다. 포스포렌은 고온에서 휘발성이어서 완전한 트랜지스터를 제조하는 것이 불가능합니다.

![]()

가장 매력적인 해결책은 전이금속 디칼코게나이드(TMD)의 개발인 것 같습니다. 고백컨대, 적어도 이 이름으로 이런 이름을 들어본 것은 이번이 처음이었습니다. 이는 2D 재료를 사용하는 가장 유망한 접근 방식 중 하나입니다. TMD는 단일 단층으로 우수한 게이트 제어 기능을 제공하므로 전력 소모가 적습니다. 실리콘보다 이동성이 좋기 때문에 성능도 좋습니다. 또한 밴드갭이 커서 소스-드레인 터널링이 제한됩니다.

Matthew는 TMD 2층 트랜지스터 제조, 특히 2D 단일층 트랜지스터 성장의 과제와 가능성, 그리고 이에 접근하는 방법에 대해 매우 자세히 설명했습니다. n-트랜지스터에 있어서 가장 매력적인 재료는 안티몬(Sb)과 비스무트(Bi)인 것 같습니다. p-트랜지스터의 경우 루테늄(Ru)입니다.

![]()

마지막 섹션에서는 전력 요구 사항을 축소하고 고급 스위칭, 특히 MESO(자기 전기 스핀 궤도) 장치에 대해 살펴보았습니다. 스위칭은 해당 전력 감소를 통해 약 0.1V에서 수행될 수 있습니다.

Matthew의 결론은 TMD를 사용하여 Intel에서 진행 중인 작업이 지속적인 CMOS 스케일링에 대한 가능성을 보여주며 MESO 장치는 급격한 전력 감소에 대한 많은 가능성을 가지고 있다는 것입니다. 그러나 이는 비교적 초기 연구이며 이러한 기술을 실제 현실로 만들기 위해서는 아직 해야 할 일이 많이 남아 있습니다.

또한 읽기 :

2024년 빅 레이스는 TSMC N2와 Intel 18A

IEDM Buzz – Intel, 새로운 수직형 트랜지스터 스케일링 혁신 선보여

인텔, 유리 기판으로 고급 패키징의 새로운 시대를 열다

다음을 통해이 게시물 공유 :

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- PlatoData.Network 수직 생성 Ai. 자신에게 권한을 부여하십시오. 여기에서 액세스하십시오.

- PlatoAiStream. 웹3 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 플라톤ESG. 탄소, 클린테크, 에너지, 환경, 태양광, 폐기물 관리. 여기에서 액세스하십시오.

- PlatoHealth. 생명 공학 및 임상 시험 인텔리전스. 여기에서 액세스하십시오.

- 출처: https://semiwiki.com/semiconductor-manufacturers/340336-iedm-what-comes-after-silicon/

- :있다

- :이다

- :아니

- 01

- 1

- 14

- 15%

- 2024

- 27

- 29

- 2D

- 2D 재료

- 30

- 3d

- 40

- 50

- 53

- 58

- 8

- a

- 소개

- 위의

- 전진

- 많은

- 후

- 적극적인

- All

- 수

- 거의

- 혼자

- 따라

- 또한

- 이기는하지만

- am

- an

- 및

- 발표

- 연간

- 구혼

- 있군요

- 지역

- 약

- AS

- At

- 매력

- 관광 명소

- 매력적인

- 뒤로

- BE

- 된

- 더 나은

- 큰

- 가장 큰

- 건물

- 비자 면제 프로그램에 해당하는 국가의 시민권을 가지고 있지만

- by

- 라는

- 통화

- CAN

- 탄소

- 탄소 나노 튜브

- 케이스

- 도전

- 과제

- 변경

- 제공

- 비교적

- 보완적인

- 완전한

- 계산

- 결론

- 회의

- CONTACT

- 계속

- 동

- 두

- 코스

- Cross

- 수십 년

- 배달

- 무례

- 세부 묘사

- 개발

- 디바이스

- 어려운

- 하기

- 한

- 아래 (down)

- 구동

- 마다

- 초기의

- 중

- 그렇지 않으면

- 대

- 에센스

- 사람

- 사실

- FET

- 발견

- 먼저,

- 처음으로

- 초점

- 다음에

- 럭셔리

- 앞

- 미래

- 문

- 얻을

- 기부

- 유리

- 가는

- 좋은

- 그래 핀

- 성장하는

- 했다

- 있다

- 들었다

- 높은

- 역사적으로

- 방법

- How To

- HTTPS

- i

- 불가능한

- 개선

- in

- 혁신

- 혁신

- 를 받아야 하는 미국 여행자

- 인텔

- 방해

- 국제 노동자 동맹

- 으로

- 소개

- IT

- 알아

- 넓은

- 성

- 법

- 층

- 가장 작은

- 처럼

- 제한된

- 이상

- 보기

- 롯

- 절감

- 주요한

- 확인

- 유튜브 영상을 만드는 것은

- 제조 업체

- 제조

- .

- 많은 사람

- 시장

- 재료

- 매튜

- 최대 폭

- 회의

- 금속

- 유동성

- 달

- 배우기

- 가장

- name

- 네트워크

- 신제품

- 다음 것

- 아니

- of

- on

- ONE

- 만

- or

- 조직

- 기타

- 아웃

- 위에

- 자신의

- 포장

- 특별한

- 사람들

- 용

- 성능

- 장소

- 계획

- 플라톤

- 플라톤 데이터 인텔리전스

- 플라토데이터

- 가능성

- 게시하다

- 힘

- 실용적인

- 프리젠 테이션

- 미리

- 아마

- 방법

- 프로세스

- 약속

- 약속

- 장래가 촉망되는

- 출판

- 추구하다

- 놓다

- 아주

- 경주

- 읽기

- 현실

- 현실

- 최근에

- 축소

- 요구조건 니즈

- 연구

- 결과

- 로드맵

- RU

- 실행

- 스케일링

- 화면

- 섹션

- 섹션

- 참조

- 보다

- 것

- 짧은

- 샷

- 쇼

- 측면

- 신호

- 규소

- 이후

- 단일

- So

- 해결책

- 일부

- 광장

- 시작

- 증기

- 고집하는

- 아직도

- 확인

- 시스템은

- 이야기

- 기술

- Technology

- 기술 개발

- 안색

- 보다

- 그

- XNUMXD덴탈의

- 미래

- 세계

- 그들

- 테마

- 그때

- 그곳에.

- Bowman의

- 그들

- 일

- 이

- 시간

- 제목의

- 에

- 함께

- 했다

- 선로

- 전이

- 티엠씨

- 아래에

- 까지

- 안내하다

- 사용

- 여러

- 버전

- 수직선

- 대단히

- 를 통해

- 휘발성의

- 벽

- 였다

- we

- 잘

- 갔다

- 뭐

- 언제

- 어느

- 의지

- 과

- 작업

- 세계

- 년

- 당신

- 제퍼 넷