구리의 저항은 결정 구조, 공극 부피, 결정립 경계 및 재료 인터페이스 불일치에 따라 달라지며, 이는 작은 규모에서 더욱 중요해집니다. 구리(Cu) 와이어의 형성은 전통적으로 트렌치 식각 공정을 사용하여 저유전율 이산화규소에 트렌치 패턴을 식각한 후 다마신 흐름을 통해 트렌치를 Cu로 채우는 방식으로 이루어졌습니다. 불행하게도 이 방법은 상당한 결정립계와 공극을 갖는 다결정 구조를 생성하여 Cu 와이어 저항을 증가시킵니다. 다마신 어닐링 공정 중 Cu 확산을 방지하기 위해 저항성이 높은 TaN 라이너 재료도 이 공정에 활용됩니다.

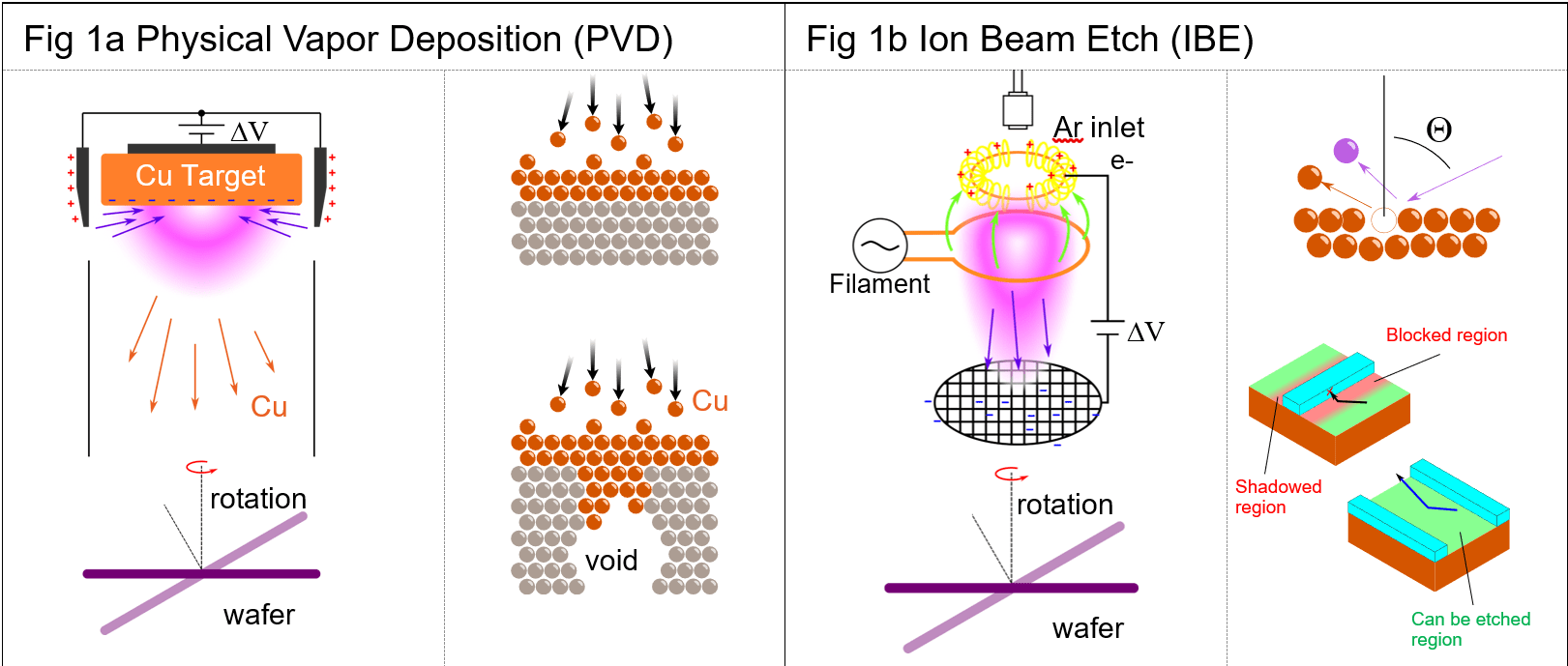

물리적 기상 증착(PVD)을 사용하면 높은 운동 에너지(10~100eV 사이)에서 구리를 증착하여 낮은 저항의 조밀한 단결정 구조를 형성할 수 있습니다. PVD의 단점은 PVD 증착의 시선이 분산되어 있고 평평한 표면에만 균일하게 증착될 수 있다는 것입니다. 깊은 구멍이나 도랑을 채우는 데는 사용할 수 없습니다(그림 1a). 고립된 와이어 모양을 형성하려면 균일한 Cu 층을 평평한 표면에 증착한 다음 이온 빔으로 물리적으로 에칭해야 합니다. Cu는 반응성 가스와 휘발성 화합물을 형성하지 않으므로 반응성 이온 식각 공정을 사용할 수 없습니다. 이온 빔 식각(IBE) 중에 생성된 가속 Ar 이온은 입사각이 매우 높을 경우 Cu를 제거할 수 있습니다. 불행하게도 마스크 그림자 효과로 인해 식각 가능한 영역이 제한됩니다. 그림 1b는 마스크가 들어오는 이온 빔에 수직일 때 재료를 에칭할 수 없는 영역(빨간색)을 보여줍니다. 이러한 에칭 실패는 방출된 원자 경로의 그림자 또는 막힘으로 인해 발생합니다. 마스크가 이온 경로와 평행하면 마스크되지 않은 모든 영역을 에칭할 수 있습니다. 따라서 이온빔 에칭은 임의로 긴 길이의 선 모양 마스크를 에칭하는 것으로 제한됩니다.

![]()

그림 1: (1a) 물리적 기상 증착(PVD); (1b) 이온빔 에칭(IBE).

공정 단계 및 가상 제작 공정

라인 저항에 대한 증착 및 식각의 영향을 이해하기 위해 이제 SEMulator3D 가시성 증착 및 식각 기능을 사용하여 PVD 및 IBE 식각 공정을 모델링합니다. PVD는 SEMulator30D에서 3도 각도 확산 가시성 증착 프로세스를 사용하여 재현되었으며, 이는 AR 이온 충격 중에 방출된 Cu 원자의 무작위 특성을 정확하게 모델링합니다. IBE는 낮은 빔 발산으로 그리드 가속 이온의 동작을 반영하기 위해 2도 각도 확산과 60도 극각 경사를 갖는 가시성 에칭을 사용하여 모델에서 재현되었습니다. 두 웨이퍼 모두 자유 회전을 한다고 가정합니다. IBE 및 PVD 제약 조건을 수용하기 위해 가상 제작 프로세스에서 다른 프로세스 단계가 조정되었습니다. 그림 2는 다마신 Cu 필(그림 2a)과 PVD/IBE 공정(그림 2b)을 모두 사용하여 생성된 동일한 구조를 보여줍니다. PVD/IBE의 특정 제한 사항을 통합하고 원하는 최종 구조에 대해 동등한 모양을 만들기 위해 추가 프로세스 단계가 포함되었습니다.

![]()

그림 2: (2a) 다마신 충진 Cu 와이어 제조; (2b) PVD/IBE Cu 와이어 제조.

그런 다음 이러한 제한 사항을 준수하면서 PVD/IBE 와이어를 사용하여 등가 16nm SRAM 회로 셀을 제작할 수 있음을 보여줍니다. 라인 중간 끝 위의 모든 금속 레이어는 평평한 표면에서 제조되므로 finFET 장치에서 볼 수 있는 복잡한 상호 연결 토폴로지와 달리 PVD/IBE 와이어에 대한 아이디어 후보가 됩니다. 그림 3은 각 금속층의 분리된 구조와 PVD/IBE를 사용하여 XNUMX개의 금속층 finFET 구조를 만드는 데 필요한 필수 단계를 보여줍니다.

![]()

그림 3: (3a) 16nm FinFET MEOL 및 3개의 금속층; (3b) PVD/IBE를 통한 단계별 금속층 제조.

저항 결과 및 결론

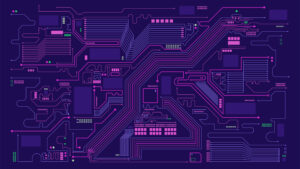

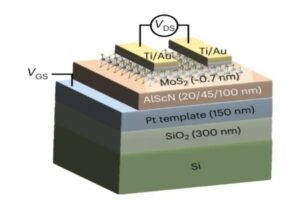

그런 다음 다마신 흐름과 물리적 기상 증착 모두에 대해 최상층 금속층부터 finFET P 및 N 채널의 비아까지 와이어의 전기 저항을 측정합니다. 그림 4는 P 및 N 채널에서 저항 측정의 시작점과 끝점을 보여줍니다(다른 모든 절연 재료는 투명함). TaN 라이너와 구리 와이어 사이의 인터페이스 저항을 보상하기 위해 TaN 인터페이스에 가장 가까운 거리의 함수로 1 nm의 지수 감쇠 상수를 사용하여 구리의 저항을 증가시켰습니다. 다마신 충진 Cu 증착은 완전한 결정질이 아닐 것으로 예상되므로 Cu의 저항률은 50% 증가했습니다. PVD/IBE 구리 공정은 TaN 라이너를 사용하지 않으므로 지수 감쇠 함수를 적용하지 않았으며, 이 모델에서는 구리의 벌크 저항률을 사용했습니다. 다마신 흐름과 PVD를 비교하는 저항률 표가 그림 4에 포함되어 있습니다.

![]()

그림 4: P 및 N 채널 저항 측정의 시작점과 끝점.

우리 모델에서 계산된 저항 값은 IBE/PVD 제조 방법을 사용하여 기존 트렌치 식각 후 다마신 증착에 비해 67%의 저항 감소를 달성할 수 있음을 나타냅니다. 이는 IBE/PVD에 TaN 라이너가 필요하지 않고 이 공정 중에 CU 저항이 낮기 때문에 발생합니다. 우리의 결과는 금속 라인 형성 중 다마신 충진에 비해 IBE/PVD를 사용함으로써 더 복잡한 제조 공정을 희생하더라도 저항률 향상을 달성할 수 있음을 나타냅니다.

티모시 양

(모든 게시물)

Timothy Yang은 Lam Research Company인 Coventor의 소프트웨어 애플리케이션 엔지니어입니다. 그는 메모리 기술에 대한 전문 지식을 바탕으로 프로세스 개발, 통합 및 수율 개선 애플리케이션 분야에서 일하고 있습니다. Coventor에서 일하기 전에 Yang은 Tokyo Electron에서 식각 방식, 포스트 리소그래피 패턴 개선 기술, SADP 및 SAQP 패터닝 애플리케이션을 위한 공정 흐름 제어, EUV 및 침지 리소그래피 포토레지스트 기술을 개발하는 일을 했습니다. Yang은 UCLA에서 물리학 학사 학위를, Chiba Institute of Technology에서 재료 과학 석사 학위를, 박사 학위를 받았습니다. 도호쿠대학교 재료과학 학사.

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- 플라토 블록체인. Web3 메타버스 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 미래 만들기 w Adryenn Ashley. 여기에서 액세스하십시오.

- 출처: https://semiengineering.com/a-deposition-and-etch-technique-to-lower-resistance-of-semiconductor-metal-lines/

- :있다

- :이다

- ][피

- 1

- 10

- 100

- a

- 위의

- 가속 된

- 수용하다

- 정확히

- 달성

- 달성

- 추가

- 조정

- All

- 모든 게시물

- 및

- 모난

- 어플리케이션

- 적용된

- AR

- 있군요

- AS

- 꾸민

- At

- 원자

- BE

- 빔

- 된다

- 된

- 사이에

- 경계

- by

- 계산 된

- CAN

- 후보자

- 어떤

- 채널

- 회사

- 비교

- 비교

- 복잡한

- 상수

- 제약

- 제어

- 전통적인

- 구리

- 비용

- 만들

- 만든

- Crystal

- 데이터

- 감소

- 깊은

- 도

- 보여

- 따라

- 예금

- 기탁 된

- 원하는

- 개발

- 개발

- 장치

- 방송

- 디스플레이

- 거리

- 분기

- 아래 (down)

- ...동안

- 마다

- 효과

- 효과

- 중

- 기사

- 동등한

- EV

- 기대하는

- 전문적 지식

- 기하 급수적 인

- 고장

- 그림

- 채우기

- 플랫

- 흐름

- 다음에

- 럭셔리

- 형태

- 형성

- 양식

- 무료

- 에

- 충분히

- 기능

- 기능

- 그리드

- 있다

- he

- 높은

- 고도로

- 구멍

- HTTPS

- 생각

- 담금

- 개량

- 개량

- in

- 사건

- 포함

- 들어오는

- 통합

- 증가

- 증가

- 표시

- 학회

- 완성

- 인터페이스

- 외딴

- IT

- 그

- JPG

- 도주

- 층

- 레이어

- 한계

- 제한된

- 라인

- 라인

- 긴

- 낮은

- 제작

- 마스크

- 마스크

- 자료

- 재료

- 최대 폭

- 측정

- 메모리

- 금속

- 방법

- 중간

- 모델

- 모델

- 배우기

- 자연

- 필요한

- 필요

- of

- on

- 주문

- 기타

- 우리의

- 평행

- 통로

- 무늬

- 물리적

- 육체적으로

- 물리학

- 플라톤

- 플라톤 데이터 인텔리전스

- 플라토데이터

- 포인트 적립

- 정반대의

- 게시하다

- 게시물

- 예방

- 이전에

- 방법

- 프로세스

- 닥치는대로의

- 접수

- 빨간색

- 반영

- 지역

- 제거

- 연구

- 저항

- 결과

- s

- 같은

- 저울

- 계획들

- 과학

- 반도체

- 셰이프

- 모양의

- 모양

- 쇼

- 시각

- 상당한

- 규소

- 이후

- 단일

- 작은

- So

- 소프트웨어

- 전파

- 시작 중

- 주 정부

- 단계

- 단계

- 구조

- 그후

- 표면

- 테이블

- 기법

- 기술

- Technology

- 그

- XNUMXD덴탈의

- Bowman의

- 세

- 미리보기

- 에

- 도쿄

- 최고의

- 전통적으로

- 투명한

- 움라

- 이해

- 대학

- 사용

- 익숙한

- 사용

- 마케팅은:

- 를 통해

- 온라인

- 가시성

- 휘발성의

- 음량

- vs

- 어느

- 동안

- 의지

- 철사

- 과

- 작업

- 일

- 일

- 수율

- 제퍼 넷