また戻ってきました 1991 ケイデンスが最初に Virtuoso 製品名を発表しましたが、32 年後の現在、この製品は生きており、非常にうまくいっていました。 Cadence の Steven Lewis が、彼らが呼ぶ新しいものについて最新情報をくれました。 ヴィルトゥオーソ スタジオ、そしてそれはすべて、現実世界のためのカスタムIC設計に関するものです。この 32 年間、私たちは半導体プロセスがムーアの法則に沿ってプレーナ CMOS を使用した 600nm から進歩し、22nm 以下の FinFET 時代にスケールダウンし、3nm ノードで GAA に達するのを見てきました。明らかに、最初のシリコンの成功を確実にするためにモデル化およびシミュレーションが必要な新しい物理的効果がより小さなノードによってもたらされたため、EDA ツールの要求が変化しました。

Cadence Virtuoso Studio の焦点は、IC 設計者が次の 6 つの領域を通じて今日の課題に取り組むのを支援することです。

- プロセスの複雑さの増加

- 数万の回路シミュレーションを処理

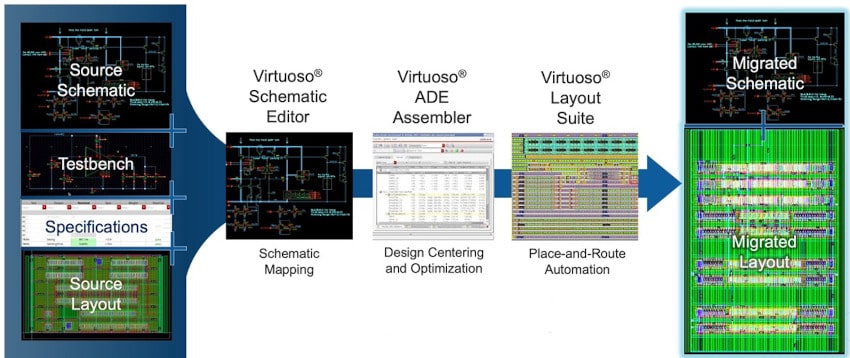

- 設計の自動化と回路の移行

- 異種統合

- AI

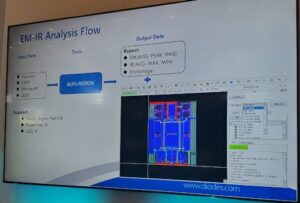

- サインオフ、設計内検証および分析

ヴィルトゥオーゾ ADE (アナログ設計環境) を使用すると、回路エンジニアは、回路図のキャプチャと回路シミュレーションを通じて、アナログ、ミックスドシグナル、RFIC の設計を検討できます。 Virtuoso ADE のアーキテクチャは、クラウドを使用してジョブ制御を改善し、RAM 使用量を削減し、シミュレーションを高速化するために刷新されました。一例として、10,000 回のシミュレーションで Spectre を実行するために必要な RAM は、シミュレーションのモニタリング用に 420MB からわずか 18MB に削減され、式の評価では 420MB の RAM からわずか 280MB に削減されました。

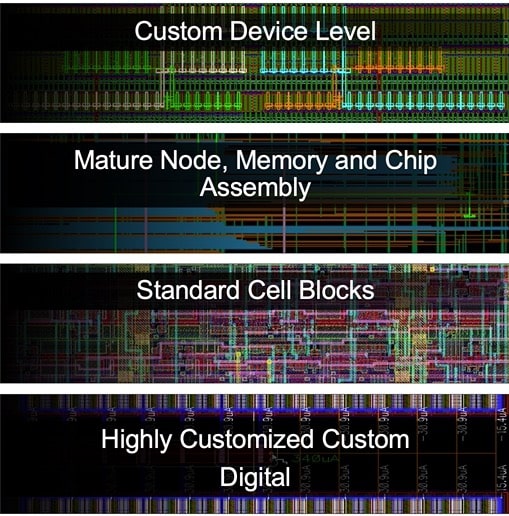

のアップデート Virtuoso レイアウト スイート 配置配線テクノロジーの 4 つの選択肢が含まれており、それぞれが Virtuoso 環境を通じて当面の固有のタスクに適しています。

4つのP&R技術

DRC および LVS の実行は物理検証の一部であり、これらをバッチ モードで実行し、修正と繰り返しを行うと、開発スケジュールが長くなります。設計内検証により、IC レイアウトの作業中に DRC と LVS を対話的に使用できるため、変更すべき点に関するフィードバックがすぐに強調表示され、生産性が向上します。 Virtuoso Layout Suite を使用するレイアウト設計者は、 Pegasus DRC および LVS テクノロジー。

チップレット、2.5D および 3D パッケージングは、PCB、パッケージ、および IC 設計ドメインという従来別々の領域にまたがっています。 Virtuoso Studio は、以下の方法でパッケージ、モジュール、IC の共同設計と検証を可能にします。

近い将来に目を向けると、アナログ回路図から機械学習と仕様に基づいたレイアウトに自動的に AI を適用する方法の詳細が明らかになることが期待できます。これらの自動生成されたトライアル レイアウトにより、非常に労働集約的なプロセスがさらに高速化されます。 AI が適用される 2 番目の開発領域は、カスタム アナログ IP を新しいプロセス ノードに移行する問題です。乞うご期待。

Virtuoso Studio の初期の顧客には、IC とパッケージの共同設計を行うアナログ デバイセズ、MediaTek の最先端 IC コンシューマ設計、ルネサスの AI ベースのプロセス移行などが含まれます。

まとめ

Virtuoso Studio は、IC 設計チームが生産性を高めるために使用できるいくつかの印象的な新機能をリリース 23.1 に導入しました。 Virtuoso インフラストラクチャは、ムーアの法則の課題に対応するために変更され、数万の回路シミュレーションによるシミュレーションが実用的で、RFIC とモジュールの 10,000D/2.5D 共同設計がサポートされ、設計内の DRC/LVS 検証にかかる時間が大幅に短縮され、AI がアナログ作業の自動化に応用されています。

関連ブログ

この投稿を共有する:- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- Platoblockchain。 Web3メタバースインテリジェンス。 知識の増幅。 こちらからアクセスしてください。

- 未来を鋳造する w エイドリエン・アシュリー。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/eda/327556-whats-new-with-cadence-virtuoso/

- :持っている

- :は

- $UP

- 1

- 10

- 3d

- a

- 私たちについて

- 加速している

- AI

- すべて

- ことができます

- 沿って

- &

- 発表の

- 適用された

- 建築

- です

- AREA

- エリア

- AS

- At

- 自動化する

- 自動的に

- オートメーション

- バック

- ベース

- BE

- き

- さ

- 以下

- 利点

- より良いです

- た

- by

- ケイデンス

- コール

- 缶

- キャプチャー

- 課題

- 変化する

- 選択肢

- はっきりと

- クラウド

- consumer

- コントロール

- カスタム

- Customers

- 中

- 需要

- 設計

- デザイナー

- デザイナー

- デザイン

- 細部

- 開発

- Devices

- すること

- ドメイン

- ダウン

- 各

- 効果

- 可能

- エンジニア

- 確保

- 環境

- 時代

- 評価

- 例

- 期待する

- 探る

- 特徴

- フィードバック

- 名

- フォーカス

- 4

- から

- さらに

- 未来

- Go

- ハンド

- 持ってる

- 助けます

- こちら

- 強調表示された

- 認定条件

- HTML

- HTTPS

- ICS

- 印象的

- in

- include

- インフラ

- 相互作用的

- IP

- ジョブ

- JPG

- 労働

- 法律

- レイアウト

- リード

- 学習

- ルイス

- 長い

- 機械

- 機械学習

- 3月

- 最大幅

- 大会

- 移行

- モード

- モジュール

- モジュール

- モニタリング

- 他には?

- 名

- 近く

- 必要とされる

- 新作

- 新しい特徴

- ノード

- of

- on

- ONE

- パッケージ

- パッケージ

- 包装

- 部

- 物理的な

- 場所

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- ポスト

- 実用的

- 現在

- 問題

- プロセス

- プロダクト

- 生産性の高い

- 生産性

- 置きます

- すぐに

- RAM

- 到達

- リアル

- 現実の世界

- 電話代などの費用を削減

- 縮小

- リリース

- の提出が必要です

- ルート

- ラン

- ランニング

- スケーリング

- 二番

- 詳細を見る

- 半導体

- 別

- シリコン

- SIX

- より小さい

- So

- 一部

- 何か

- スパン

- 仕様

- 分光

- スピード

- start

- 滞在

- 研究

- 成功

- スイート

- サポート

- 取る

- 取り

- 仕事

- タスク

- チーム

- テクノロジー

- それ

- アプリ環境に合わせて

- ボーマン

- 介して

- 時間

- 〜へ

- ツール

- 伝統的に

- トライアル

- ユニーク

- アップデイト

- 使用法

- つかいます

- Verification

- 、

- WELL

- この試験は

- while

- 意志

- ワーキング

- 世界

- 年

- ゼファーネット