今日のペースの速い世界では、半導体設計の革新が常に求められています。 より速く、より正確で、革新的なソリューションの必要性により、半導体設計開発の分野でジェネレーティブ AI (#GenerativeAI) の可能性を探求する道が開かれました。 それはできるでしょうか? そうだね! この記事シリーズでは、ジェネレーティブ AI がどのように半導体設計に革命をもたらしているかを実証する刺激的な実験について詳しく掘り下げます。

実験 1 – FSM 図から SV コードへ

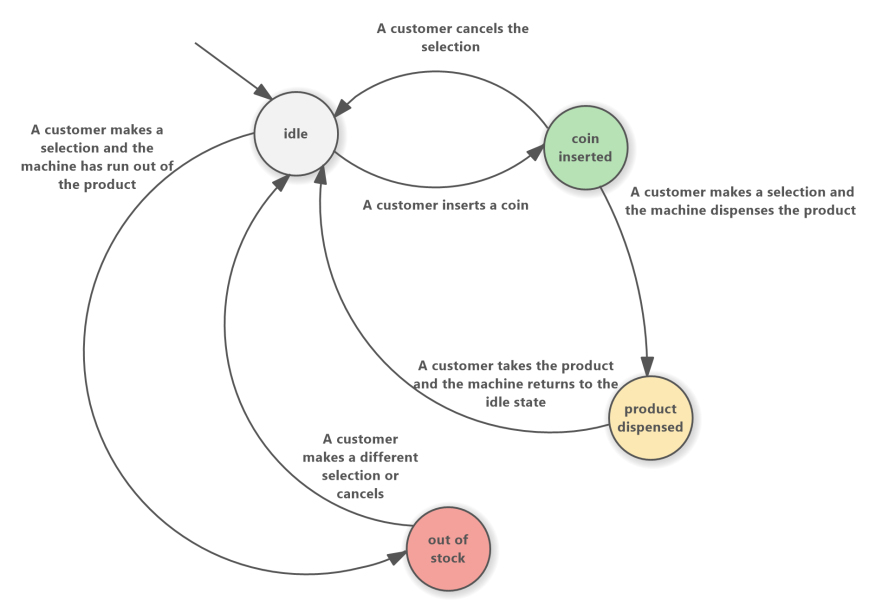

この最初の実験では、有限状態マシン (FSM) 図を SystemVerilog (SV) コードに変換することにより、生成 AI の注目すべき機能を紹介します。 この場合、Google の生成 AI モデル – BARD を使用して、表紙の写真に示されている自動販売機 FSM の SystemVerilog 実装が生成されました (出典: https://www.softwareideas.net/fsm-finite-state-machine-diagram)

生成されたコード

// 自動販売機 FSM // 免責事項: このコードは正しいかどうかテストされていません module Vending_machine ( input clk、input reset、input Coin_inserted、input product_selected、input product_dispensed、output reg dispense_product、output reg return_coin ); // 状態を定義します localparam [2:0] IDLE = 3'b000; localparam [2:0] COIN_INSERTED = 3'b001; localparam [2:0] PRODUCT_SELECTED = 3'b010; localparam [2:0] PRODUCT_DISPENSED = 3'b011; localparam [2:0] OUT_OF_STOCK = 3'b100; // レジスタ reg [2:0] current_state を定義します。 // 遷移ロジックは常に @(ポーズジ clk またはポーズジ リセット) 開始 if (リセット) 開始 current_state <= IDLE; end else begin case (current_state) IDLE: begin if (coin_inserted) begin current_state <= COIN_INSERTED; end else begin current_state <= IDLE; end end COIN_INSERTED: begin if (product_selected) begin current_state <= PRODUCT_SELECTED; end else begin current_state <= COIN_INSERTED; 終了 終了 PRODUCT_SELECTED: begin if (product_dispensed) begin current_state <= PRODUCT_DISPENSED; end else if (out_of_stock) begin current_state <= OUT_OF_STOCK; end else begin current_state <= PRODUCT_SELECTED; 終了 終了 PRODUCT_DISPENSED: 開始 current_state <= IDLE; OUT_OF_STOCK の終了: current_state <= IDLE の開始; end endcase end end // 出力ロジックは常に @(posedge clk) begin case (current_state) PRODUCT_DISPENSED: begin dispense_product <= 1'b1; デフォルト終了: 開始 dispense_product <= 1'b0; end endcase end always @(posedge clk) begin case (current_state) OUT_OF_STOCK: begin return_coin <= 1'b1; デフォルト終了: 開始 return_coin <= 1'b0; エンドエンドケース エンドエンドモジュール

FSM ダイアグラムはシリコン設計で広く使用されており、Generative AI がどのように重要な役割を果たすことができるかは次のとおりです。

- 生産性の向上: Generative AI を使用すると、図の作成と更新が簡単になります。 デザイナーは高レベルのコンセプトに集中し、AI に基礎作業を任せることができます。 これにより、開発プロセスが加速されるだけでなく、設計変更が必要な場合でも迅速な反復が可能になります。

- より高い精度: FSM 図は、ハードウェア設計における標準化されたツールとなっています。 生成 AI モデルは膨大なデータセットでトレーニングされ、これらの図を正確な SV コードに変換することに熟達します。 その結果、人的エラーが減少し、コードの品質が向上します。

- 改善されたイノベーション: Generative AI のスピードと精度により、新しい設計アイデアを迅速に探求するための扉が開かれます。 設計者は、さまざまな FSM 図をブレインストーミングして実験し、イノベーションの限界を押し上げることができます。 この機敏性により、各世代の半導体デバイスに高度な機能をより迅速に統合できます。

注意 – 現実の確認

生成 AI には大きな期待が寄せられていますが、注意が必要です。 生成されたコードは必ずしも完璧であるとは限りません。 設計者は、AI が生成したコードを実稼働環境に導入する前に、そのコードをレビューし、厳密にテストする必要があります。 最終的な半導体設計の信頼性と機能性を確保するには、徹底的な検証プロセスが不可欠です。

まとめ

ジェネレーティブ AI は、半導体設計開発における変革をもたらします。 実験 1 は、FSM 図から SV コードへの変換を簡素化し、生産性の向上、精度の向上、イノベーションの促進を実現することで、その可能性を明確に示しています。 ただし、AI によって生成されたソリューションは、創造的なプロセスを完全に置き換えるのではなく、創造的なプロセスを強化するツールとして使用されるべきであることを覚えておくことが重要です。 適切なチェックとバランスがあれば、人間の創意工夫と生成 AI の相乗効果が半導体業界の画期的な発展につながる可能性があります。

また読む:

実現可能な L4/L5 自動運転とエッジでの生成 AI 推論への長年の障害

LLM によるアサーション合成。 検証におけるイノベーション

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/artificial-intelligence/337119-generative-ai-for-silicon-design-article-1-code-my-fsm/

- :持っている

- :は

- :not

- 1

- a

- 加速する

- 精度

- 正確な

- 高度な

- AI

- AIモデル

- ことができます

- また

- 常に

- および

- です

- 記事

- AS

- At

- 自律的

- バランス

- BE

- になる

- になる

- 始まる

- の間に

- ブースト

- 境界

- ブレインストーム

- 焙煎が極度に未発達や過発達のコーヒーにて、クロロゲン酸の味わいへの影響は強くなり、金属を思わせる味わいと乾いたマウスフィールを感じさせます。

- by

- 缶

- 機能

- 場合

- 注意

- 変更

- 小切手

- はっきりと

- コード

- コンセプト

- 定数

- 変換

- 変換

- カバー

- 作成

- クリエイティブ

- 重大な

- デフォルト

- 定義します

- 掘り下げる

- 需要

- 実証

- 展開する

- 設計

- デザイナー

- 開発

- 進展

- Devices

- 図

- 免責事項

- do

- 行われ

- ドア

- 運転

- 各

- ほかに

- end

- 高めます

- 巨大な

- 確保

- 完全に

- 環境

- エラー

- 本質的な

- エキサイティング

- 運動

- 実験

- 実験

- 探査

- 探る

- テンポの速い

- 特徴

- ファイナル

- 名

- フォーカス

- 機能性

- ゲームチェンジャー

- 生成する

- 生成された

- 世代

- 生々しい

- 生成AI

- Googleの

- 画期的な

- 下地

- Hardware

- ハードウェア設計

- 持ってる

- ハイレベル

- より高い

- 保持している

- 認定条件

- しかしながら

- HTTPS

- 人間

- 考え

- アイドル

- if

- 説明する

- 実装

- in

- 増加した

- 産業を変えます

- 独創性

- 革新的手法

- 革新的な

- 統合

- に

- IT

- 繰り返し

- ITS

- つながる

- う

- ロジック

- 機械

- 作成

- マーケット

- 最大幅

- 五月..

- モデル

- モジュール

- 他には?

- しなければなりません

- my

- 必要

- 新作

- 今

- of

- 提供すること

- on

- の

- 開いた

- or

- 出力

- 完璧

- 電話

- 画像

- 極めて重要な

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- プレイ

- ポスト

- 潜在的な

- プロセス

- 生産

- 生産性

- 約束

- 押す

- 品質

- より速い

- 急速な

- 読む

- 現実

- realm

- 再充電

- 電話代などの費用を削減

- 登録

- レジスタ

- 信頼性

- 顕著

- 覚えています

- replace

- の提出が必要です

- 結果

- レビュー

- 革命

- 右

- 職種

- 半導体

- シリーズ

- すべき

- 示す

- シリコン

- 単純化

- ソリューション

- 調達

- スピード

- 標準化されました

- 都道府県

- 米国

- SWIFT

- 相乗効果

- 合成

- test

- テスト

- それ

- それら

- ボーマン

- この

- 介して

- 〜へ

- 今日の

- ツール

- 豊富なツール群

- 訓練された

- 遷移

- 更新

- 中古

- さまざまな

- 広大な

- 、

- 実行可能な

- 極めて重要な

- ました

- 仕方..

- we

- いつ

- 広く

- 世界

- ゼファーネット