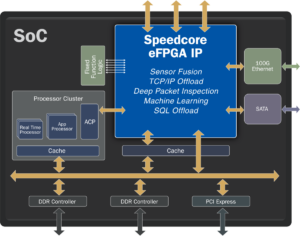

TSMC מציעה שירותי יציקה מאז 1987, והצומת הראשון שלהם ב-3 ננומטר נקרא N3 והופיע לראשונה ב-2022; עכשיו יש להם צומת 3nm משופר המכונה N3E שהושק. כל צומת חדש דורש אז IP שתוכנן בקפידה, מאופיין ומאומת בסיליקון כדי להבטיח שמפרטי ה-IP עומדים וניתן להשתמש בו בבטחה בעיצובי SoC. IP חדש זה חייב לכסות מגוון רחב של פונקציות, כמו ממשק, זיכרון והיגיון. לסינופסיס יש צוות IP גדול שהתמודד עם האתגר על ידי יצירת IP חדש עבור הצומת TSMC N3E והשגת הצלחת סיליקון במעבר ראשון.

Chiplet Interconnect

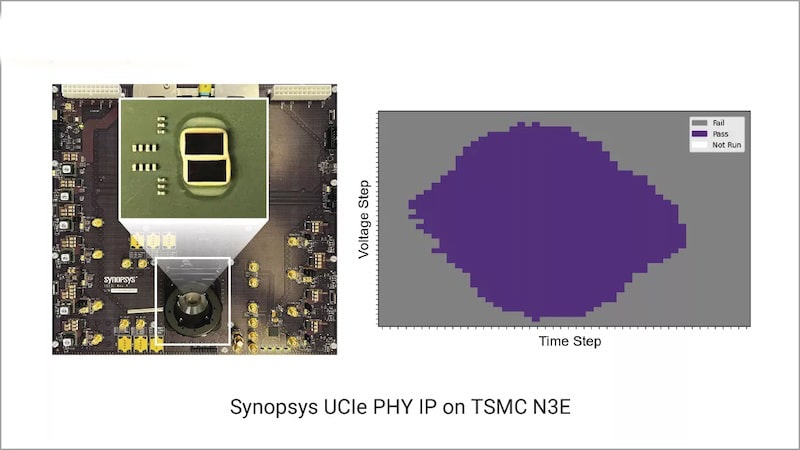

מערכות המורכבות מצ'יפלטים דורשות תקשורת למוות, וכאן נכנס תקן UCIeo לשחק. Synopsys הוא חבר תורם ב- קונסורציום UCIe, והם מציעים IP עבור שניהם א UCIe Cמפעיל ו-UCIe PHY בצומת TSMC N3E.

השמיים UCIe PHY IP היו תוצאות סיליקון ראשונות באוגוסט 2023, שהציגו קצבי נתונים של 16GB/s וניתנים להרחבה ל-24GB/s לערוץ. יעילות החשמל היא 0.3 pJ/bit.

PHY IP

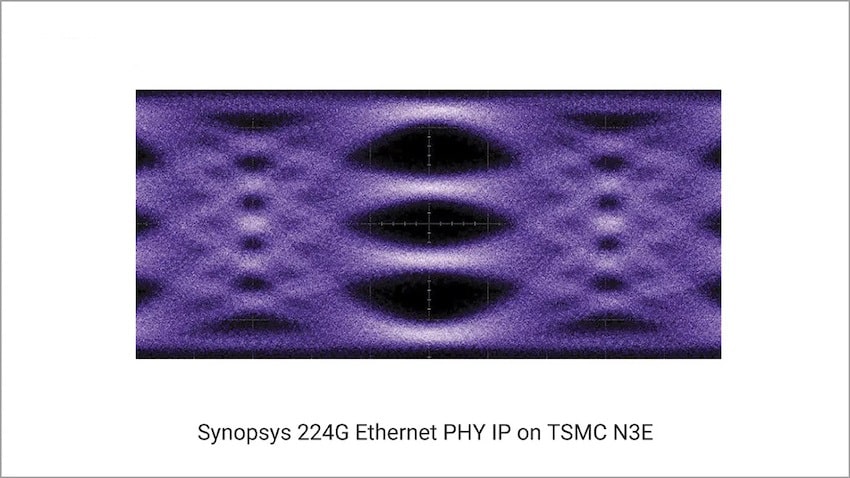

ה-IEEE אישר את תקן 802.3 עבור Ethernet בחזרה 1983, הסטנדרט המורחב למדי, בעוד ש-Synopsys 224G Ethernet PHY IP זכה להצלחה ראשונה בסיליקון אוגוסט 2023. מהנדסי רשת מסתכלים בתרשים העין כדי לראות את קידוד PAM-4. רמות הריצוד עלו על מפרטי התקן IEEE 802.3 ו-OIF.

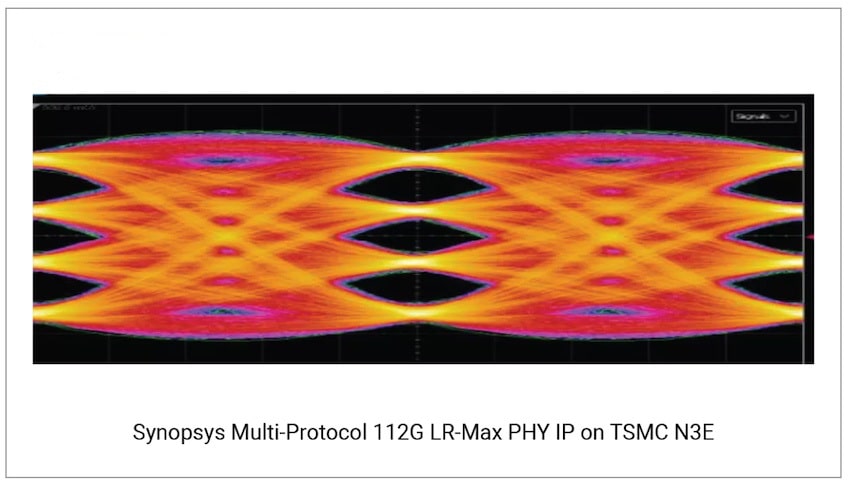

תמיכה בתקנים כמו PCI Express 6.0, 400G/800G Ethernet, CCIX, CXL2.0/3.0, JESD204 ו-CPRI יש את Synopsys Multi-Protocol 112G PHY IP. מהנדסים יכולים לשלב את ה-PHY IP הזה עם MAC ו-PCS כדי לבנות בלוק Ethernet של 200G/400G/800G.

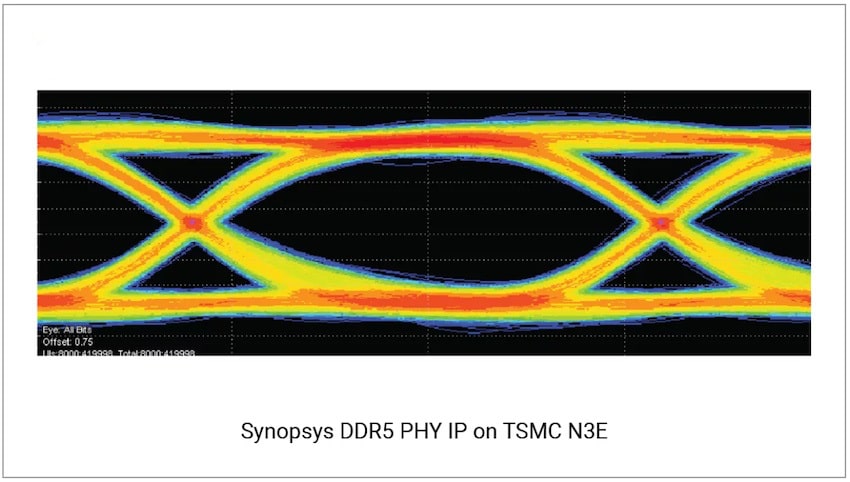

SDRAM ומודולי זיכרון יכולים להשתמש ב Synopsys DDR5 PHY IP ב-TSMC N3E כדי להשיג קצבי העברה של עד 8400Mbps. אתה יכול לראות את העין הפקוחה לרווחה ואת השוליים הברורים עבור IP זה פועל במהירות.

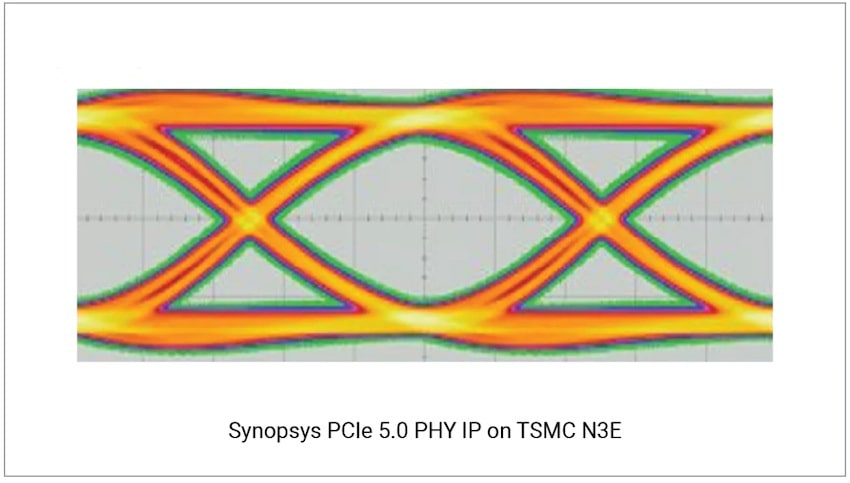

תקן PCI Express החל את דרכו בשנת 2003 והוא עודכן ללא הרף כדי לעמוד בדרישות ההולכות וגדלות של מחשוב ענן, אחסון ובינה מלאכותית. PCIe 5.0 נתמך כעת באמצעות Synopsys PCIe 5.0 PHY IP. הסיליקון הראשון ב-TSMC N3E הראה מהירויות פעולה של 32 GT / s, והוא עבר את בדיקות התאימות.

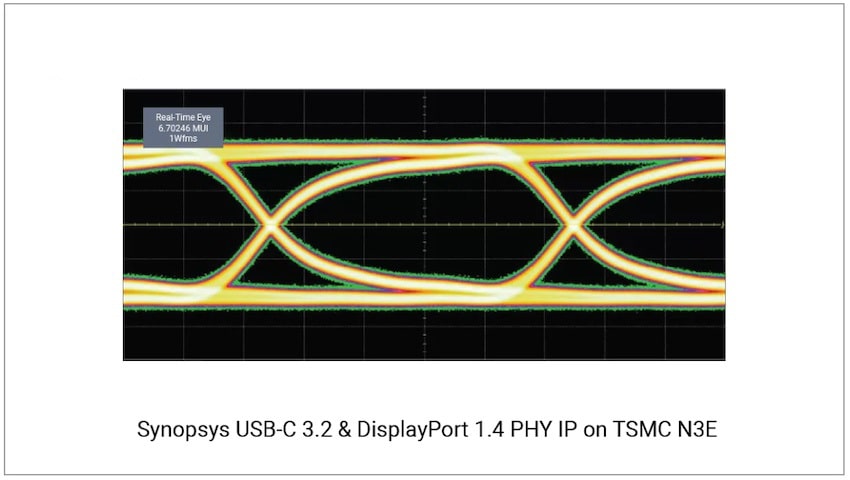

אני משתמש ב-USB-C ב-MacBook Pro, iPad Pro וטלפון אנדרואיד שלי כבר שנים. Synopsys תומך כעת USB-C 3.2 ו-DisplayPort 1.4 PHY IP בתהליך ה-TSMC האחרון. עם IP זה משתמשים יכולים לחבר עד 8K צגי Ultra High Definition.

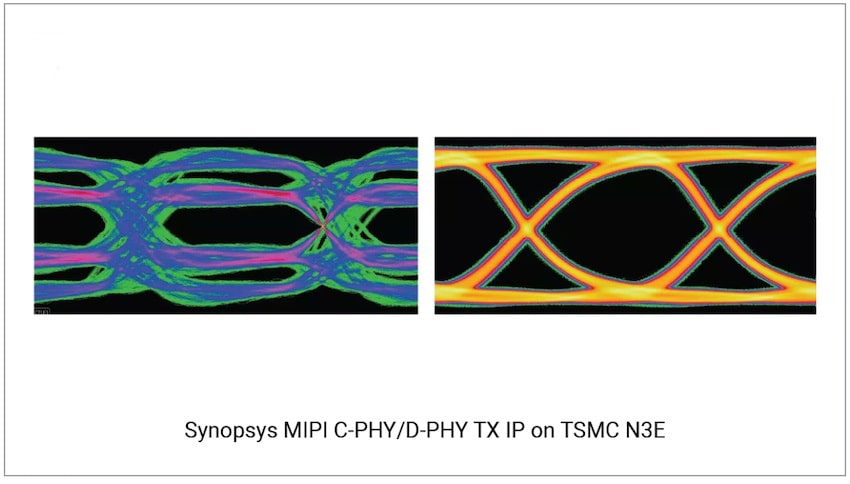

חברות סמארטפונים תקנו את פרוטוקול MIPI לפני שנים כדרך יעילה לחיבור מצלמות Synopsys MIPI C-PHY IP/D-PHY IP יכול לפעול במהירות של 6.5Gb/s לנתיב ו-6.5Gs/s לשלישה. ה-C-PHY IP תומך בגרסה 2.0, וה-D-PHY IP2.1.

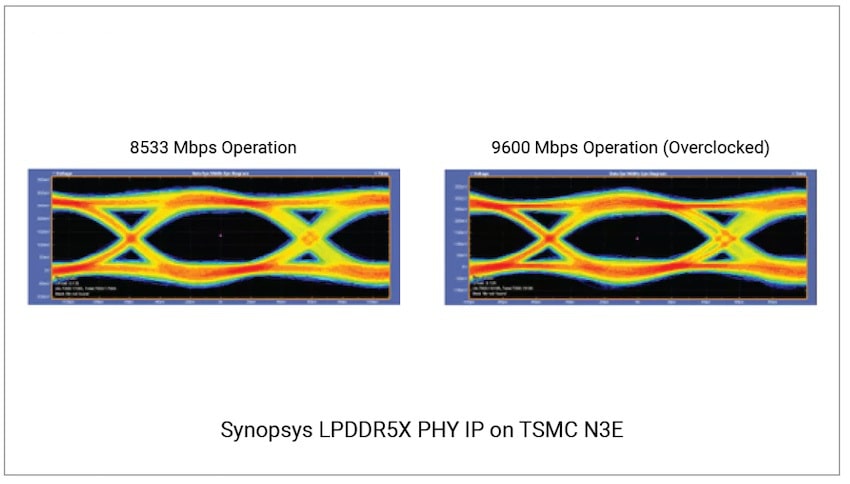

המפרט העדכני ביותר של בקר DRAM סינכרוני הוא LPDDR5X, התומך במהירויות העברת נתונים של עד 8533Mbps, שיפור של 33% לעומת זיכרון LPDDR5. ה בקר Synopsys LPDDR5X/5/4X מוכח בסיליקון ומוכן לעיצוב איתו.

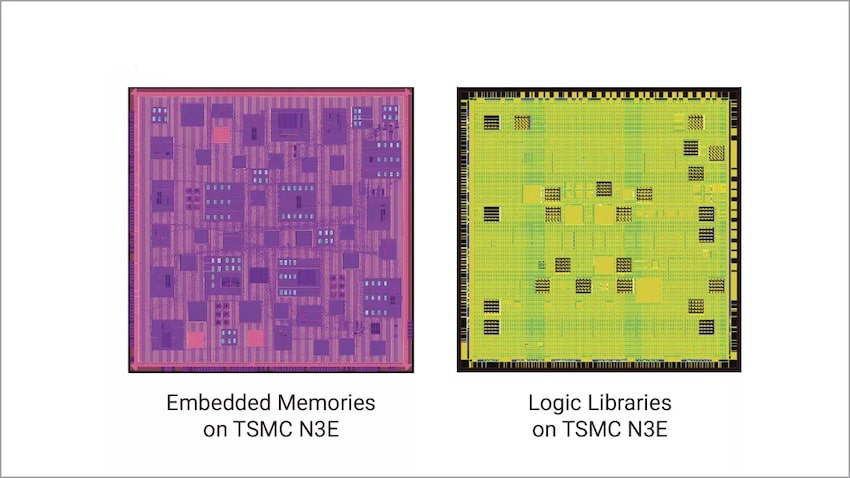

ספריות וזיכרונות לוגיקה

עד חצי מהשטח של SoC יכול להיות זיכרונות, אז החדשות הטובות הן שה IP של קרן סינופסיס מאפשר לך להוסיף זיכרונות ותאי ספריית לוגיקה במהירות לתוך עיצוב חדש. להלן דיאגרמות שבבי הבדיקה של Synopsys בצומת TSMC N3E עבור זיכרונות וספריות לוגיקה.

<br> סיכום

TSMC ו-Synopsys שיתפו פעולה בצורה טובה למדי לאורך השנים, והשותפות הזו משתרעת כעת לצומת N3E שבו מעצבי SoC יכולים למצוא IP שנבדק בסיליקון עבור ממשקים, זיכרונות והיגיון. כוח, ביצועים ותפוקה נראים אטרקטיביים עבור N3E, כך שהטכנולוגיה מוכנה לעיצובים התובעניים ביותר שלך. התחלת עיצוב עם N3E גם מספקת לך נתיב מהיר יותר למעבר לתהליך N3P.

במקום ליצור את כל ה-IP שלך מאפס, מה שיאריך את לוח הזמנים שלך, ידרוש משאבים הנדסיים נוספים ויגדיל את הסיכון, למה שלא תסתכל על מה שיש ל-Synopsys להציע במגוון רחב של בלוקי IP שמוכחים בסיליקון.

בלוגים קשורים

שתף את הפוסט הזה באמצעות:

- הפצת תוכן ויחסי ציבור מופעל על ידי SEO. קבל הגברה היום.

- PlatoData.Network Vertical Generative Ai. העצים את עצמך. גישה כאן.

- PlatoAiStream. Web3 Intelligence. הידע מוגבר. גישה כאן.

- PlatoESG. פחמן, קלינטק, אנרגיה, סביבה, שמש, ניהול פסולת. גישה כאן.

- PlatoHealth. מודיעין ביוטכנולוגיה וניסויים קליניים. גישה כאן.

- מקור: https://semiwiki.com/ip/336595-tsmc-n3e-is-ready-for-designs-thanks-to-ip-from-synopsys/

- :יש ל

- :הוא

- :לֹא

- :איפה

- $ למעלה

- 1

- 2022

- 2023

- 8k

- a

- להשיג

- השגתי

- להוסיף

- לִפנֵי

- AI

- תעשיות

- מאפשר

- גם

- an

- ו

- דְמוּי אָדָם

- מאושר

- ARE

- AREA

- AS

- At

- מושך

- אוגוסט

- בחזרה

- BE

- היה

- להיות

- לחסום

- אבני

- שניהם

- לִבנוֹת

- by

- נקרא

- מצלמות

- CAN

- בזהירות

- תאים

- לאתגר

- ערוץ

- מאופיין

- שבב

- ברור

- ענן

- ענן מחשוב

- שיתף פעולה

- לשלב

- מגיע

- תקשורת

- חברות

- הענות

- מחשוב

- לְחַבֵּר

- תמיד

- תורם

- בקר

- לכסות

- יוצרים

- נתונים

- לראשונה

- הגדרה

- תובעני

- דרישות

- עיצוב

- מעוצב

- מעצבים

- עיצובים

- דיאגרמות

- מציג

- דיבוב

- יְעִילוּת

- יעיל

- הנדסה

- מהנדסים

- משופר

- לְהַבטִיחַ

- כל

- אקספרס

- משתרע

- עין

- ראשון

- בעד

- קרן

- בית היציקה

- החל מ-

- פונקציות

- טוב

- גדל

- היה

- חצי

- יש

- כאן

- גָבוֹהַ

- HTML

- HTTPS

- IEEE

- השבחה

- in

- להגדיל

- מִמְשָׁק

- ממשקים

- אל תוך

- IP

- iPad

- IT

- jpg

- נתיב

- גָדוֹל

- האחרון

- הושק

- רמות

- ספריות

- סִפְרִיָה

- כמו

- לינקדין

- הגיון

- נראה

- הסתכלות

- מק

- MacBook

- עשוי

- שולי

- max-width

- לִפְגוֹשׁ

- חבר

- זכרונות

- זכרון

- נפגש

- נודד

- דקות

- מודולים

- יותר

- רוב

- צריך

- my

- רשת

- חדש

- חדשות

- צומת

- עַכשָׁיו

- of

- הַצָעָה

- הצעה

- on

- לפתוח

- להפעיל

- פועל

- הַחוּצָה

- יותר

- שֶׁלוֹ

- שותפות

- עבר

- נתיב

- מחשבים

- עבור

- ביצועים

- טלפון

- PHP

- אפלטון

- מודיעין אפלטון

- אפלטון נתונים

- לְשַׂחֵק

- הודעה

- כּוֹחַ

- מִקצוֹעָן

- תהליך

- פרוטוקול

- מספק

- מהר

- מהירות

- דַי

- רכס

- תעריפים

- מוכן

- לדרוש

- דורש

- משאבים

- תוצאות

- רייזן

- הסיכון

- בבטחה

- להרחבה

- לוח זמנים

- לגרד

- לִרְאוֹת

- שירותים

- הראה

- הצגה

- סיליקון

- since

- So

- מפרטים

- מְהִירוּת

- מהירויות

- תֶקֶן

- תקנים

- החל

- החל

- אחסון

- הצלחה

- מסייע

- תומך

- עלתה על

- לקחת

- נבחרת

- טכנולוגיה

- מבחן

- בדיקות

- תודה

- זֶה

- השמיים

- האזור

- שֶׁלָהֶם

- אז

- שם.

- הֵם

- זֶה

- ל

- יַחַד

- להעביר

- שלישיה

- tsmc

- Ultra

- מְעוּדכָּן

- USB

- USB-C

- להשתמש

- מְשׁוּמָשׁ

- משתמשים

- באמצעות

- תוקף

- באמצעות

- היה

- דֶרֶך..

- טוֹב

- מה

- אשר

- בזמן

- למה

- רָחָב

- טווח רחב

- יצטרך

- עם

- שנים

- תְשׁוּאָה

- אתה

- זפירנט