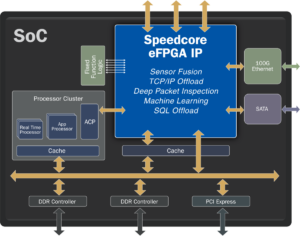

בניאס לאבס היא חברת מוליכים למחצה המפתחת פתרונות תשתית לתקשורת מהדור הבא. שוק היעד שלה הוא שוק תשתיות המחשוב בעלות ביצועים גבוהים, כולל מרכז נתונים בקנה מידה גבוה, רשתות, AI, מודול אופטי ו-SoCs מתגי Ethernet עבור עיצובי מחשוב בעלי ביצועים גבוהים. SoCs אלה דורשים עיצובי Ethernet במהירות גבוהה ופתרונות עם אחזור נמוך כדי לספק ביצועי מערכת מוגברים ולהאיץ את זמן היציאה לשוק. החברה פיתחה DSP SoC אופטי בטכנולוגיית תהליך 5nm כדי לענות על הדרישות של שוק זה.

![]()

SoC אופטי DSP הוא סוג מיוחד של מערכת-על-שבב (SoC) המיועד לשימוש במערכות תקשורת אופטיות מהירות. בנוסף ל-DSP, ה-DSP האופטי SoC כולל בדרך כלל בלוקי IP של ממשק מהיר, כגון Ethernet PHY IP, PCIe IP ובקרי זיכרון DDR. סוגים אלה של SoCs מאפשרים העברות נתונים במהירות גבוהה בהשהיות נמוכות לעיבוד אותות בזמן אמת. הם נועדו גם למזער את צריכת החשמל, מה שהופך אותם לאידיאליים עבור יישומים הדורשים פעולה יעילה עם בעיות תרמיות מופחתות. עם היתרונות מגיעים גם אתגרים. הדרישות המיוחדות של מערכות תקשורת אופטי הופכות את תכנון SoC אופטי DSP למאתגר יותר מאשר תכנון SoC רגיל.

אתגרי יישום

האתגרים נעים סביב מורכבות העיצוב, דרישות הכוח והביצועים המחמירות והצורך לעמוד בתקנים שונים בתעשייה. השילוב של מספר בלוקים של IP כולל מעבד DSP, Ethernet PHY IP ובלוקים מותאמים אישית אחרים דורש תכנון ואימות קפדניים. ממשקים מהירים נוספים כגון PCIe ו-DDR מוסיפים עוד למורכבות העיצוב. הממשקים המהירים ובלוקי ה-IP המרובים במערכת יכולים ליצור עיוות אות, דיבור צולב והפרעות אלקטרומגנטיות, שיכולות להשפיע על ביצועי המערכת ואמינותם. יש לבצע ניתוח ואופטימיזציה של שלמות אותות והספק מוקדם במחזור התכנון כדי להבטיח שהמערכת תוכל לעמוד בדרישות הביצועים והאמינות שלה. לבסוף, עמידה בדרישות הזמן לשוק עשויה להיות מאתגרת. שוק תשתיות המחשוב עתירות הביצועים מתפתח במהירות, וצוותי פיתוח SoC צריכים לספק את העיצובים שלהם במהירות כדי להקדים את המתחרים.

איך מגיעים ל-First Pass Silicon Success

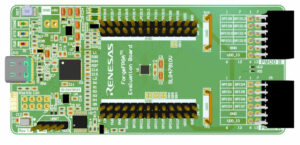

התגברות על האתגרים שהוזכרו לעיל דורשת גישה מקיפה. אחד המרכיבים הקריטיים של פתרונות בעלי ביצועים גבוהים עם זמן אחזור נמוך הוא ה-Ethernet PHY IP. ה-Ethernet PHY IP אחראי על ממשק השכבה הפיזית בין ה-SoC לרשת ה-Ethernet. ה-IP חייב לתמוך בממשקי Ethernet מהירים, כולל 10G, 25G, 40G, 50G, 100G, 200G, 400G ו-800G, ולספק זמן אחזור נמוך וצריכת חשמל נמוכה. בנוסף, ה-IP חייב לתמוך בתקנים שונים, כולל IEEE 802.3 ו-Ethernet Alliance. מרכיב חשוב נוסף הוא חבילת העיצוב של EDA. חבילת העיצוב של EDA חייבת לספק פתרון מקיף לתכנון ואימות ה-SoC, כולל אופטימיזציה של הספק, ניתוח ביצועים, אופטימיזציה של שטח וניתוח תפוקה. במידה, חבילת העיצוב של EDA כוללת תכונות מתקדמות, כגון בינה מלאכותית (AI) ולמידת מכונה (ML), מה טוב יותר עבור פרודוקטיביות משופרת וזמן יציאה לשוק מופחת.

Synopsys מאיץ את הצלחת הסיליקון הראשונה

Synopsys מציעה פתרונות הנותנים מענה לאתגרים הייחודיים של פיתוח SoCs עבור שוק תשתיות המחשוב עתירות הביצועים. החברה מספקת פתרון IP מקיף הכולל בדיקת היתכנות ניתוב, הנחיות מצע אריזה, מודלים של שלמות אותות והספק, וניתוח הצלבות יסודי. זה הכרחי כדי להתמודד עם אתגרי האותות ושלמות ההספק העומדים בפניהם בעת פיתוח SoC DSP אופטי. 112G Ethernet PHY IP של Synopsys מציע זמן אחזור נמוך, אורכי הגעה גמישים ובגרות בטכנולוגיית תהליך של 5nm, מה שהופך אותו לפתרון אידיאלי עבור מרכז נתונים בקנה מידה גבוה, רשתות, AI, מודול אופטי ו-SoCs מתגי Ethernet. בנוסף, Synopsys מציעה חבילת עיצוב של EDA שמספקת תוצאות באיכות גבוהה עם אופטימיזציה של הספק, ביצועים, שטח ותפוקה. חבילת ה-EDA Design מונעת בינה מלאכותית של Synopsys מספקת פתרונות להגברת ביצועי המערכת ולהאצת זמן היציאה לשוק, מה שהופך אותה למרכיב חיוני בפתרון מוצלח לשוק תשתיות המחשוב עתירות הביצועים.

<br> סיכום

Synopsys מספקת פתרונות בעלי ביצועים גבוהים עם אחזור נמוך, המאיצים את הפיתוח של מתג Ethernet ורשתות SoC מתקדמים. למידע נוסף על פתרונות ה-IP המקיפים של Synopsys, ה-EDA Design Suite המקיף שלהם וחבילת ה-AI-Enhanced EDA שלהם, בקר בעמודים הבאים.

פתרונות ה-IP המקיפים של Synopsys

חבילת עיצוב EDA מונעת בינה מלאכותית של Synopsys

גם לקרוא:

מערכות ריבוי מתים: ההפרעה הגדולה ביותר בתחום המחשוב מזה שנים

הוצאת הסיכון מפיתוח מעבד RISC-V משלך עם אופטימיזציה מהירה, מונחה ארכיטקטורה, PPA

להזין את הרעב הגובר ברוחב פס עם Ethernet במהירות גבוהה

שתף את הפוסט הזה באמצעות:

- הפצת תוכן ויחסי ציבור מופעל על ידי SEO. קבל הגברה היום.

- Platoblockchain. Web3 Metaverse Intelligence. ידע מוגבר. גישה כאן.

- הטבעת העתיד עם אדריאן אשלי. גישה כאן.

- מקור: https://semiwiki.com/ip/327703-synopsys-accelerates-first-pass-silicon-success-for-banias-labs-networking-soc/

- :יש ל

- :הוא

- a

- אודות

- מֵעַל

- להאיץ

- מאיץ

- תוספת

- נוסף

- בנוסף

- כתובת

- מתקדם

- יתרונות

- קדימה

- AI

- אליאנס

- גם

- an

- אנליזה

- ו

- אחר

- יישומים

- גישה

- ARE

- AREA

- סביב

- מלאכותי

- בינה מלאכותית

- בינה מלאכותית (AI)

- AS

- At

- רוחב פס

- BE

- מוטב

- בֵּין

- הגדול ביותר

- אבני

- לְהַגבִּיר

- CAN

- זהיר

- מרכז

- האתגרים

- אתגר

- איך

- תקשורת

- תקשורת

- חברה

- תחרות

- מורכבות

- רְכִיב

- רכיבים

- מַקִיף

- מחשוב

- צְרִיכָה

- לִיצוֹר

- קריטי

- מנהג

- מחזור

- נתונים

- מרכז נתונים

- למסור

- מספק

- עיצוב

- מעוצב

- תכנון

- עיצובים

- מפותח

- מתפתח

- צעצועי התפתחות

- מפתחת

- התפוררות

- מוקדם

- יעיל

- מתעורר

- לאפשר

- משופר

- לְהַבטִיחַ

- חיוני

- מתפתח

- מתמודד

- מהר

- תכונות

- בסופו של דבר

- ראשון

- גמיש

- הבא

- בעד

- החל מ-

- נוסף

- גדל

- הנחיות

- ביצועים גבוהים

- באיכות גבוהה

- HTML

- HTTPS

- רעב

- אידאל

- IEEE

- תמונה

- פְּגִיעָה

- הֶכְרֵחִי

- חשוב

- in

- כולל

- כולל

- גדל

- תעשייה

- תקני התעשייה

- תשתית

- השתלבות

- שלמות

- מוֹדִיעִין

- מִמְשָׁק

- ממשקים

- IP

- בעיות

- IT

- שֶׁלָה

- מעבדות

- חֶבִיוֹן

- שכבה

- לִלמוֹד

- למידה

- נמוך

- מכונה

- למידת מכונה

- לעשות

- עשייה

- שוק

- בגרות

- max-width

- לִפְגוֹשׁ

- מפגש

- זכרון

- מוּזְכָּר

- ML

- מודלים

- מודול

- יותר

- מספר

- צורך

- רשת

- רשתות

- הדור הבא

- of

- המיוחדות שלנו

- on

- ONE

- מבצע

- אופטימיזציה

- אופטימיזציה

- אחר

- שֶׁלוֹ

- אריזה

- לעבור

- ביצועים

- גופני

- אפלטון

- מודיעין אפלטון

- אפלטון נתונים

- הודעה

- כּוֹחַ

- תהליך

- תהליך

- מעבד

- פִּריוֹן

- לספק

- מספק

- מהירות

- מהר

- לְהַגִיעַ

- חומר עיוני

- זמן אמת

- מופחת

- רגיל

- אמינות

- לדרוש

- דרישות

- דורש

- אחראי

- תוצאות

- הסיכון

- סמיקונדקטור

- לאותת

- סיליקון

- פִּתָרוֹן

- פתרונות

- מיוחד

- תקנים

- להשאר

- לימוד

- הצלחה

- מוצלח

- כזה

- מערכת

- תמיכה

- מתג

- מערכת

- מערכות

- יעד

- צוותי

- טכנולוגיה

- מֵאֲשֶׁר

- זֶה

- השמיים

- שֶׁלָהֶם

- אותם

- תרמי

- אלה

- הֵם

- זֶה

- ל

- גַם

- העברות

- סוגים

- בדרך כלל

- ייחודי

- להשתמש

- אימות

- שונים

- אימות

- באמצעות

- לְבַקֵר

- אשר

- עם

- תְשׁוּאָה

- זפירנט