Alat, metodologi, dan alur yang telah ada sejak awal desain semikonduktor mulai mengalami kegagalan, namun saat ini tidak banyak peneliti yang dapat menemukan solusi potensial. Industri ini sendirian dalam merumuskan ide-ide tersebut, dan itu akan membutuhkan banyak kerja sama antara perusahaan EDA, pabrik, dan desainer, yang sebelumnya tidak menjadi keunggulan mereka.

Sulit untuk mengoptimalkan sesuatu jika Anda tidak dapat menganalisisnya, dan analisis menjadi jauh lebih sulit karena banyak masalah dalam produk semikonduktor besar bersifat multi-fisika, atau merupakan kombinasi perangkat keras dan perangkat lunak, sistem, papan. , paket IC, interposer, chip, dan blok IP. Di masa lalu, pendekatan pemecah belah dan taklukkan merupakan cara yang digunakan untuk menyelesaikan permasalahan. Terkadang hal ini dilakukan secara hierarki, seperti memverifikasi blok sepenuhnya sebelum diintegrasikan, atau terkadang dengan mengisolasi masalah, misalnya dengan melintasi domain jam.

Namun, semakin banyak permasalahan yang menolak pendekatan semacam ini, dan industri ini masih belum menemukan solusi yang mudah. Misalnya, masalah seperti keamanan adalah masalah tingkat sistem. Hal yang sama berlaku untuk banyak masalah kinerja atau daya. Bahkan masalah seperti integritas sinyal dan daya harus ditangani dengan hierarki yang mencakup IP hingga sistem, melalui interkoneksi kompleks yang terdiri dari banyak lapisan, yang masing-masing secara tradisional telah disesuaikan dengan seperangkat alat yang berbeda.

Hal ini menciptakan serangkaian masalah pemodelan baru dan mengharuskan beberapa alat yang ada mengambil peran yang jauh lebih besar dibandingkan sebelumnya. Alternatifnya, industri harus serius dalam menerapkan batasan pada desain, sehingga analisis dapat dilakukan. Meskipun industri ini mulai menyadari masalah ini, saat ini mereka menanganinya sedikit demi sedikit. Sejauh ini, belum ada yang mengusulkan solusi umum yang dapat diterapkan di masa depan.

Ini adalah permainan angka. “Jika Anda memperhitungkan keseluruhan sistem, jumlah tikungan akan meningkat pesat,” kata Shekhar Kapoor, direktur senior pemasaran di Synopsys. “Saat ini, pendekatannya masih kembali ke cara membagi dan menaklukkan secara hierarkis dalam melakukan sesuatu, dan juga menemukan cara untuk mengurangi jumlah skenario yang harus Anda hadapi. Tanpa itu, kebutuhan komputasi akan sangat besar. Dan agar Anda dapat keluar dari sistem, jalurnya akan jauh lebih panjang.”

Pendekatan hierarki masih berguna untuk beberapa hal. “Prinsip abstraksi digunakan di tempat-tempat yang kompleksitas fundamental analisisnya terlalu rumit,” kata Prakash Narain, presiden dan CEO Real Intent. “Dalam simulasi, kami menggunakannya dalam model fungsional bus, dan analisis waktu statis. Kami menggunakannya dengan membuat model pengaturan waktu tingkat I/O, penyeberangan domain jam, teknik sign-off statis untuk penyeberangan domain jam, penyeberangan domain ulang. Ini semua adalah tempat di mana kami berhasil memanfaatkan teknik hierarki.”

Pengurangan sudut sering kali melibatkan keputusan desain. “Mengapa tidak menghindari penyeberangan domain,” kata Kapoor dari Synopsys. “Jaga agar desainnya tidak sinkron, di mana setiap bagian memiliki waktunya sendiri-sendiri. Dengan begitu, Anda dapat mengatur jumlah sudut untuk bagian tertentu. Kemudian Anda juga bisa menggunakan teknik pengurangan sudut. Dengan pendekatan hierarki untuk analisis waktu, kami mengatur waktu setiap bagian secara terpisah, lalu keduanya digabungkan dengan batasannya, dan melakukan penggabungan sudut.”

Yang dimaksud dengan jalan bertambah dimana-mana. “Banyak orang ingin melakukan analisis sistem multi-die,” kata Mick Posner, direktur senior HPC IP di Synopsys. “Solusi integritas sinyal dan daya digunakan untuk fokus pada cetakan, melalui paket, hingga PCB. Sekarang sudah menjadi die, untuk interposer, untuk mengemas, menjadi PCB. Hal ini terutama berlaku untuk antarmuka berkinerja tinggi, seperti 112G, dan antarmuka memori, di mana terdapat banyak fokus pada dampak interposer tersebut, atau lapisan perutean. Kita harus mencari cara untuk mengemas informasi tersebut dengan IP, yang terkadang tidak mungkin dilakukan karena kita tidak tahu bagaimana IP tersebut digunakan. Kami dapat memberikan alur referensi yang menunjukkan cara mereka melakukan analisis tersebut.”

Masalahnya adalah sulitnya melakukan beberapa abstraksi yang diperlukan. “Persyaratan abstraksi sangat spesifik untuk aplikasi,” kata Narain dari Real Intent. “Mereka bergantung pada teknologi, dan mereka berbeda dari produk ke produk bahkan untuk aplikasinya. Mereka bergantung pada teknologi yang digunakan oleh setiap produk untuk mengimplementasikan fungsionalitas tersebut. Maka Anda harus mempertimbangkan tingkat akurasi yang Anda cari. Ini akan sangat spesifik untuk aplikasi dan teknologinya, dan standarnya akan menyusul nanti karena itu adalah proses yang sangat sulit untuk dicapai.”

Posner memberikan contoh spesifik. “Untuk HBM3, kami mengemas desain referensi. Ini adalah desain referensi dari chip pengujian kami sendiri. Kami mengembangkan PHY, tetapi saat kami melakukan pengujian chip, kami juga harus mengembangkan interposer yang terhubung ke tumpukan HBM. Kami harus melakukan segala sesuatu dengan cara yang serupa dengan apa yang harus dilakukan pelanggan. Kemudian mereka dapat memanfaatkan aliran itu. Tapi, tentu saja, itu adalah chip pengujian kami. Mereka dapat menggunakan kembali alur tersebut, namun data sebenarnya akan spesifik untuk cara mereka menyusun interposer tersebut.”

Masalah pemodelan

Alasan dari kesulitan-kesulitan ini adalah kurangnya model dan sarana untuk menghasilkan model-model tersebut. Model adalah trade-off antara fidelitas, akurasi, dan kinerja. Model dengan akurasi tinggi cenderung memiliki fidelitas yang baik tetapi dieksekusi dengan lambat, sedangkan model yang dieksekusi lebih cepat kehilangan sesuatu dalam hal akurasi, fidelitas, atau keduanya. Model yang dibutuhkan adalah model fungsional dan non fungsional.

Kami telah menangani masalah dalam domain fungsional selama beberapa waktu, namun diperlukan lebih banyak pekerjaan. “Untuk verifikasi fungsional, kami membuat beberapa model,” kata Neil Hand, direktur strategi teknologi verifikasi desain di EDA Siemens. “Kami memiliki siklus yang akurat, set instruksi yang akurat, dan sebagainya. Namun Anda ingin memiliki cara yang mudah untuk berpindah di antara keduanya. Dengan pemodelan hibrid, Anda memiliki kemampuan yang mereka sebut berjalan cepat, kemudian berjalan akurat. Saat bepergian, Anda harus bisa mengganti model. Misalnya, seseorang mungkin mem-boot sistem operasi pada model yang kurang akurat dan berjalan cepat, lalu mengubah status desain menjadi model yang berjalan akurat. Sekarang mereka dapat melangkah maju dari titik tersebut dengan lebih banyak rincian dan lebih banyak ketelitian dalam model itu sendiri. Kami perlu mengembangkan kemampuan yang lebih besar untuk beralih antar fidelitas saat Anda membutuhkannya.”

Saat ini, metodologi serupa digunakan untuk verifikasi tingkat blok dan integrasi. “Saat Anda membeli inti Arm, Anda tidak memverifikasi fungsionalitas inti Arm,” kata Simon Davidmann, pendiri dan CEO untuk Perangkat Lunak Imperas. “Anda memverifikasi integrasinya. Di sinilah perusahaan seperti Breker berperan. Anda mempunyai hambatan-hambatan ini, tetapi bagaimana Anda memastikan bahwa mereka semua berbicara baik satu sama lain? Anda tidak melakukannya dengan cara yang sama seperti Anda memverifikasi blok dengan UVM atau Verilog, yang Anda gunakan untuk verifikasi tingkat blok. Hierarki dalam verifikasi adalah membuat semua blok Anda berfungsi, mengujinya satu per satu, lalu menyatukannya dan mengkhawatirkan pengujian integrasi. Namun hal tersebut memerlukan metodologi yang berbeda.”

Permasalahannya adalah pembuatan model-model ini membutuhkan waktu dan usaha, dan setiap model harus diverifikasi untuk memastikan konsistensi. “Untuk arsitektur, Anda juga memerlukan properti non-fungsional, seperti detail waktu,” kata Tim Kogel, insinyur utama pembuatan prototipe virtual untuk Synopsys. “Ini memerlukan lebih banyak upaya untuk membangun model. Meskipun industri telah menetapkan tingkat abstraksi yang lebih tinggi, namun belum berhasil menciptakan alat untuk membangun model kinerja non-fungsional ini. Misalnya, perangkat lunak melihat elemen pemrosesan sebagai unit sumber daya yang lebih abstrak, dan kemudian Anda mungkin memiliki model interkoneksi dan subsistem memori yang lebih rinci, atau jaringan antara chip yang berbeda. Arteris dan Arm menyediakan ini untuk jaringan yang koheren, untuk berbagai jenis IP interkoneksi, dan juga untuk pengontrol memori, yang merupakan bagian penting dari integrasi.”

Diperlukan lebih banyak alat pembuatan model. “Saat Anda menganalisis desain menggunakan pola tertentu, Anda memiliki kemampuan untuk membuat model abstrak,” kata Malik Vasirikala, direktur dan spesialis produk untuk ansys. “Misalnya, ketika saya menganalisis bagian dalam sebuah chip, saya juga mengetahui bagaimana perilakunya dari perspektif antarmuka. Saya dapat membuat model seolah-olah saya melihat keseluruhan bagian ini dari pinggiran, atau pada batas chip ke dunia luar. Kemudian ketika menganalisis chip lain yang terhubung dengannya, saya tidak memerlukan detail internal chip tersebut. Saya cukup memasukkan model perilaku itu ke dalam analisis ini dan selesai.”

Namun ada kesenjangan. “Bagian yang hilang adalah integrasi dan pertukaran data yang lebih baik antara dunia fisik dan dunia virtual,” kata Kogel dari Synopsys. “Kami memerlukan model arsitektur berdasarkan informasi denah lantai yang dipelajari, geometri yang dipelajari, yang ketika dipindahkan ke tingkat prototipe virtual akan membantu Anda memvalidasi kinerja, daya, dan termal berdasarkan aktivitas aplikasi nyata.”

Kapan kamu selesai?

Penyelesaian adalah salah satu masalah dalam tugas analisis apa pun. Sudahkah Anda meliput kasus-kasus penting? Metrik cakupan ada untuk verifikasi fungsional tingkat blok, namun ini adalah model lain yang perlu dimigrasikan ke tingkat abstraksi yang lebih tinggi, dan ke domain non-fungsional. “Jika Anda menjalankan sebagian verifikasi Anda di ranah RTL, dan beberapa di prototipe virtual, bagaimana Anda menggabungkan item cakupan tersebut?” tanya Tangan Siemens. “Saat ini hal tersebut dilakukan melalui cakupan fungsional, namun terdapat peluang – terutama ketika Anda melihat pada pembangkitan stimulus, ketika Anda menggunakan AI pada sisi cakupan – untuk mulai menyimpulkan informasi dari berbagai jenis cakupan.”

Dunia perangkat lunak sangat lemah dalam hal ini. “Saya rasa tidak ada pendekatan atau metodologi standar untuk peliputan,” kata Davidmann dari Imperas. “Sepengetahuan saya, belum ada otomatisasi yang dilakukan orang-orang pada perangkat lunak yang setara dengan titik cakupan dan kelompok cakupan dalam HDL. Pemeriksa protokol memang ada untuk verifikasi dan analisis. Dan Anda dapat membuat statistik, tempat Anda dapat melihat fungsinya, atau melihat akses ke variabel. Mengingat kurangnya standarisasi, kami menyediakan peralatan yang diperlukan, namun pengguna harus membuatnya sendiri.”

Setelah Anda memiliki gagasan tentang cakupan, maka Anda dapat memikirkan untuk mengoptimalkan verifikasi. “Baik itu stimulus portabel dalam bentuk saat ini, atau sesuatu yang didasarkan pada gagasan tersebut, kita memerlukan pembuatan skenario di tingkat sistem,” kata Hand. “Dapatkah kita mengambil hal tersebut dan melangkah lebih tinggi dengan menggunakan prototipe virtual dan pemodelan sistem serta menghasilkan skenario pada sistem yang kuat? Hal ini akan menjadi semakin penting seiring dengan semakin terintegrasinya sistem.”

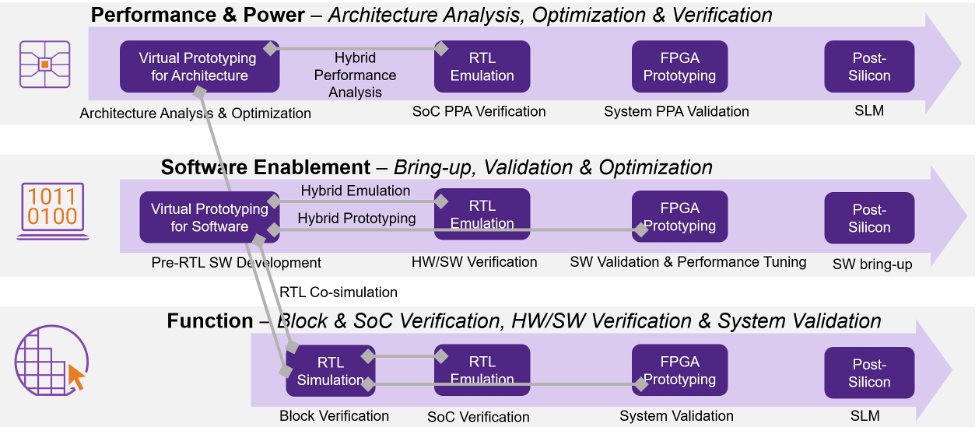

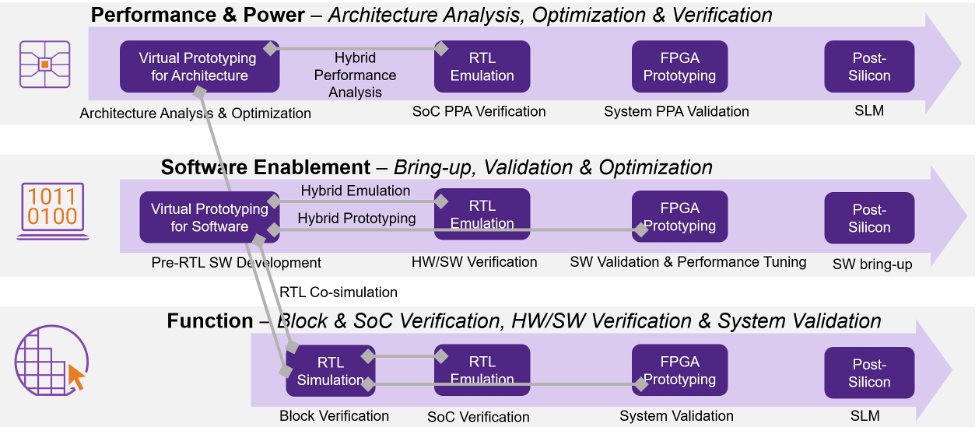

Yang lain setuju. “Anda ingin memiliki kesinambungan antara tingkat IP, tingkat SoC, dan kemudian verifikasi dalam silikon,” kata Kogel. “Stimulus portabel adalah salah satu pendekatan untuk mencapai hal tersebut. Anda kemudian juga dapat menjalankan kasus uji yang diabstraksi, seperti program pada inti yang tertanam, lalu di prototipe virtual. Dalam arti luas, inilah verifikasi konsep arsitektur. Nanti, Anda menjalankan RTL dengan perangkat lunak di emulator, pada prototipe FPGA, dan itu bisa digunakan untuk validasi performa karena lebih seperti, 'Apa yang Anda lihat adalah apa yang Anda dapatkan.' Ini bukan model virtual tingkat tinggi.”

Gambar 1: Berbagai tingkat model dan tujuan verifikasi. Sumber: Sinopsis

Cara lain untuk mendekati verifikasi integrasi adalah melalui kepatuhan fungsional. “Ada upaya di Arm yang disebut 'sistem siap' untuk mendefinisikan apa artinya menjadi patuh dan mampu mem-boot sistem operasi,” kata Nick Heaton, insinyur terkemuka dan arsitek verifikasi SoC di Irama. “Jika implementasi Anda berhasil, Anda tidak perlu memodifikasi rilis OS Red Hat, atau apa pun. Mereka hanya akan melakukan hal itu. Ini adalah kontrak antara perangkat lunak dan perangkat keras. Stimulus portabel mencoba melakukan hal tersebut dengan cara yang lebih umum, dan kami menyebutnya VIP karena ini merupakan konten out-of-the-box yang kami berikan, misalnya, pada tingkat koherensi. Kami menguji semua permutasi koherensi, dan pada dasarnya kami dapat menerapkannya ke platform apa pun, apakah itu Arm atau RISC-V atau apa pun.”

Masalah debug

Mampu menjalankan suatu model adalah satu hal, tetapi menemukan dan memperbaiki masalah dalam suatu model atau cara model tersebut digunakan merupakan tingkat kerumitan yang berbeda. “Jika Anda melakukan debug perangkat lunak pada perangkat keras atau FPGA, Anda mendapatkan gdb yang terhubung ke perangkat tersebut, dan Anda dapat melakukan satu langkah aliran instruksi prosesor,” kata Davidmann. “Tetapi masalahnya muncul ketika mereka memiliki 10 prosesor atau lebih, dan mereka perlu mengetahui kapan 'ini' menulis ke 'itu', seperti apa tampilannya? Analisis dan debug harus dilakukan secara holistik agar Anda dapat melihat semuanya. Ini harus melibatkan tumpukan perangkat lunak sehingga Anda dapat melihat perilaku platform.”

Ini adalah serangkaian tuntutan yang berbeda dari sekadar men-debug perangkat keras. “Saat kami mulai melakukan pengujian integrasi perangkat keras/perangkat lunak, kami mulai melihat lebih banyak kemampuan debugging perangkat lunak yang terintegrasi ke dalam lingkungan debugging prototipe virtual,” kata Hand. “Saat kami mulai menyediakannya bagi perancang sistem, ada peluang bagi kami untuk melihat model penggunaan, dan lingkungan desain apa yang ingin dikerjakan oleh tim tersebut? Bagaimana kita bisa menerapkannya? Anda ingin perancang sistem berinteraksi dengan prototipe virtual dengan cara yang bermakna bagi mereka. Ini semua tentang mengidentifikasi pengguna akhir dan memetakan model penggunaan kepada mereka. Ini adalah area di mana ada banyak hal yang bisa kami lakukan, dan ada banyak hal yang harus kami lakukan.”

Alat dan metodologi harus sesuai dengan kebutuhan di setiap tingkat. “Orang yang melakukan verifikasi integrasi bukanlah orang yang mengetahui setiap blok,” kata Heaton dari Cadence. “Waktu untuk melakukan debug atau waktu penyelesaian menjadi semakin penting. Jumlah siklus debug yang dapat Anda jalankan dalam sehari sangatlah bermasalah. Jika alat tersebut dapat mengarahkan Anda ke tempat pesanan pertama, hal ini dapat menghemat waktu debug. Kami berada di awal perjalanan ini. Pembelajaran sedang berlangsung, dan cara kami menggunakan alat-alat tersebut akan menjadi lebih baik.”

AI mungkin bisa membantu. “Meskipun manusia memiliki jaringan saraf terbaik, I/O kita masih bersifat serial,” kata Matt Graham, direktur grup teknik produk di Cadence. “Mungkin kami bisa menangani dua atau tiga jalur paralel, tapi yang pasti tidak lebih dari itu. Mesin dapat mempertimbangkan semua hal ini secara paralel. Mereka mungkin menggunakan algoritme sederhana, atau seperangkat AI sederhana, untuk melakukan sesuatu yang sangat paralel dan sangat terintegrasi. Tapi itu berbeda dengan apa yang bisa kita lakukan sendiri. Mungkin hal-hal seperti terakhir kali kami melakukan revisi atau apa yang berubah, atau mengidentifikasi perbedaan perilaku, atau parameter apa yang diubah dalam IP.”

Kesimpulan

Kompleksitas sistem membebani banyak alat dan metodologi yang ada saat ini. Teknik-teknik yang digunakan di masa lalu, meski masih bernilai, tidaklah cukup. Industri telah melihat banyak permasalahan ini dalam bidang verifikasi fungsional, namun hal tersebut hanyalah puncak gunung es. Mengingat betapa sedikitnya kemajuan yang dicapai di bidang yang paling dipahami dengan baik, kemajuan mungkin tidak akan terjadi dengan cepat di banyak bidang lainnya – khususnya yang didorong oleh pengemasan yang canggih.

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- Platoblockchain. Intelijen Metaverse Web3. Pengetahuan Diperkuat. Akses Di Sini.

- Sumber: https://semiengineering.com/design-and-verification-methodologies-breaking-down/

- 1

- 10

- a

- Sanggup

- Tentang Kami

- ABSTRAK

- Akun

- ketepatan

- tepat

- Mencapai

- di seluruh

- kegiatan

- maju

- AI

- algoritma

- Semua

- selalu

- analisis

- menganalisa

- menganalisis

- dan

- Lain

- Aplikasi

- pendekatan

- pendekatan

- arsitektur

- arsitektur

- DAERAH

- daerah

- ARM

- sekitar

- Otomatisasi

- tersedia

- kembali

- berdasarkan

- Pada dasarnya

- karena

- menjadi

- menjadi

- menjadi

- sebelum

- Awal

- makhluk

- TERBAIK

- Lebih baik

- antara

- lebih besar

- Memblokir

- Blok

- papan

- Melanggar

- membawa

- luas

- membangun

- Bangunan

- membangun

- bis

- membeli

- Irama

- panggilan

- bernama

- kemampuan

- mampu

- kasus

- kasus

- ceo

- Pasti

- memeriksa

- keping

- Keripik

- KOHEREN

- kombinasi

- bagaimana

- kedatangan

- Perusahaan

- kompleks

- kompleksitas

- pemenuhan

- compliant

- konsep

- terhubung

- menghubungkan

- Mempertimbangkan

- kendala

- Konten

- kontrak

- kerja sama

- Core

- Sudut

- sudut

- Tentu saja

- menutupi

- liputan

- tercakup

- membuat

- menciptakan

- membuat

- terbaru

- pelanggan

- siklus

- data

- hari

- transaksi

- berurusan

- keputusan

- menyampaikan

- mengantarkan

- tuntutan

- tergantung

- Mendesain

- desainer

- desain

- rinci

- terperinci

- rincian

- mengembangkan

- dikembangkan

- Mati

- berbeda

- sulit

- kesulitan

- Kepala

- Terkemuka

- melakukan

- domain

- domain

- Dont

- turun

- didorong

- setiap

- mudah

- usaha

- antara

- elemen

- tertanam

- insinyur

- Teknik

- memastikan

- Lingkungan Hidup

- lingkungan

- Setara

- terutama

- mapan

- Bahkan

- segala sesuatu

- contoh

- Pasar Valas

- menjalankan

- ada

- memperpanjang

- luar

- Fashion

- FAST

- lebih cepat

- beberapa

- kesetiaan

- Ara

- Menemukan

- temuan

- Pertama

- Memperbaiki

- aliran

- Mengalir

- Fokus

- mengikuti

- bentuk

- Depan

- pendiri

- Pendiri dan CEO

- FPGA

- dari

- sepenuhnya

- fungsionil

- fungsi

- fungsi

- mendasar

- masa depan

- permainan

- Umum

- menghasilkan

- generasi

- mendapatkan

- Memberikan

- diberikan

- Go

- Anda

- akan

- baik

- lebih besar

- Kelompok

- Grup

- menangani

- Perangkat keras

- topi

- membantu

- hirarki

- tingkat tinggi

- kinerja tinggi

- lebih tinggi

- sangat

- holistik

- JAM

- Seterpercayaapakah Olymp Trade? Kesimpulan

- How To

- HPC

- HTTPS

- besar

- Manusia

- Hibrida

- ide-ide

- mengidentifikasi

- Dampak

- melaksanakan

- implementasi

- penting

- memaksakan

- mustahil

- in

- menggabungkan

- meningkatkan

- makin

- Secara individual

- industri

- informasi

- terpadu

- integrasi

- integritas

- maksud

- berinteraksi

- Antarmuka

- interface

- intern

- melibatkan

- IP

- isu

- masalah

- IT

- item

- Diri

- perjalanan

- Kapoor

- Menjaga

- kunci

- Jenis

- Tahu

- pengetahuan

- Kekurangan

- besar

- Terakhir

- lapisan

- lapisan

- belajar

- pengetahuan

- Tingkat

- adalah ide yang bagus

- Leverage

- Mungkin

- sedikit

- lagi

- melihat

- terlihat seperti

- Lot

- Mesin

- terbuat

- Membuat

- mengelola

- cara

- banyak

- pemetaan

- Marketing

- secara besar-besaran

- Cocok

- max-width

- berarti

- cara

- Memori

- Bergabung

- penggabungan

- metodologi

- Metodologi

- Metrik

- mungkin

- hilang

- model

- pemodelan

- model

- memodifikasi

- lebih

- paling

- bergerak

- beberapa

- perlu

- Perlu

- kebutuhan

- jaringan

- jaringan

- saraf

- saraf jaringan

- New

- Gagasan

- jumlah

- nomor

- ONE

- operasi

- sistem operasi

- Kesempatan

- Optimize

- mengoptimalkan

- urutan

- OS

- Lainnya

- sendiri

- paket

- pengemasan

- Paralel

- parameter

- bagian

- tertentu

- khususnya

- melewati

- lalu

- path

- pola

- Konsultan Ahli

- prestasi

- perspektif

- fisik

- bagian

- potongan-potongan

- Tempat

- Tempat

- Platform

- plato

- Kecerdasan Data Plato

- Data Plato

- Titik

- poin

- kolam

- mungkin

- potensi

- kekuasaan

- Prakash

- presiden

- Utama

- prinsip

- Masalah

- masalah

- proses

- pengolahan

- prosesor

- Produk

- Produk

- program

- Kemajuan

- properties

- diusulkan

- protokol

- prototipe

- prototipe

- prototyping

- memberikan

- menyediakan

- nyata

- dunia

- alasan

- mengenali

- Merah

- Red Hat

- menurunkan

- desain referensi

- Pers

- membutuhkan

- wajib

- Persyaratan

- membutuhkan

- peneliti

- sumber

- kuat

- Peran

- Run

- berjalan

- sama

- Save

- skenario

- keamanan

- melihat

- pencarian

- melihat

- semikonduktor

- senior

- rasa

- serial

- serius

- set

- harus

- Pertunjukkan

- menandatangani

- Sinyal

- mirip

- Simon

- Sederhana

- simulasi

- sejak

- tunggal

- Perlahan

- So

- sejauh ini

- Perangkat lunak

- larutan

- Solusi

- beberapa

- Seseorang

- sesuatu

- sumber

- rentang

- spesialis

- tertentu

- tumpukan

- Tumpukan

- standar

- standar

- awal

- Mulai

- Negara

- statistika

- Langkah

- Masih

- rangsangan

- Penyelarasan

- aliran

- kuat

- sukses

- berhasil

- seperti itu

- cukup

- menyediakan

- Beralih

- sistem

- sistem

- disesuaikan

- Mengambil

- Dibutuhkan

- pembicaraan

- tugas

- tim

- teknik

- Teknologi

- istilah

- uji

- pengujian

- tes

- Grafik

- Daerah

- Masa depan

- mereka

- diri

- panas

- hal

- hal

- tiga

- Melalui

- Tim

- waktu

- Waktunya

- waktu

- ujung

- untuk

- hari ini

- bersama

- terlalu

- alat

- puncak

- terhadap

- secara tradisional

- benar

- jenis

- dipahami

- Sedang berlangsung

- unit

- us

- menggunakan

- Pengguna

- Pengguna

- dimanfaatkan

- Memanfaatkan

- MENGESAHKAN

- pengesahan

- Berharga

- berbagai

- Verifikasi

- diverifikasi

- memeriksa

- memverifikasi

- VIP

- maya

- dunia maya

- Menonton

- cara

- Apa

- apakah

- yang

- sementara

- SIAPA

- akan

- tanpa

- Kerja

- bekerja

- kerja

- dunia

- dunia

- akan

- penulisan

- Anda

- zephyrnet.dll