A tervezőknek számos módja van a RISC-V megoldások megkülönböztetésére. Az egyik útvonal a specifikációnak megfelelő különféle RISC-V-mag testreszabásokba és bővítményekbe indul. Egy másik az IP-blokkok kiválasztására és összeállítására összpontosít egy vagy több RISC-V mag körül egy teljes rendszer-chip (SoC) kialakításban. Egy harmadik is kialakulóban van: a RISC-V magok és más IP-blokkok összekapcsolása hálózaton-chipen (NoC) az egyszerű buszstruktúra helyett. És ez nem csak a csúcskategóriákban érvényes – a RISC-V magok és a NoC-k párosítása számos SoC tervezési kihívásra ad választ, ahol az adatoknak hatékonyan kell áramolniuk bármilyen munkaterhelés mellett, bármilyen chip-protokollt használva.

A teljesítményszintek a fejlett összekapcsolási sémákkal változnak

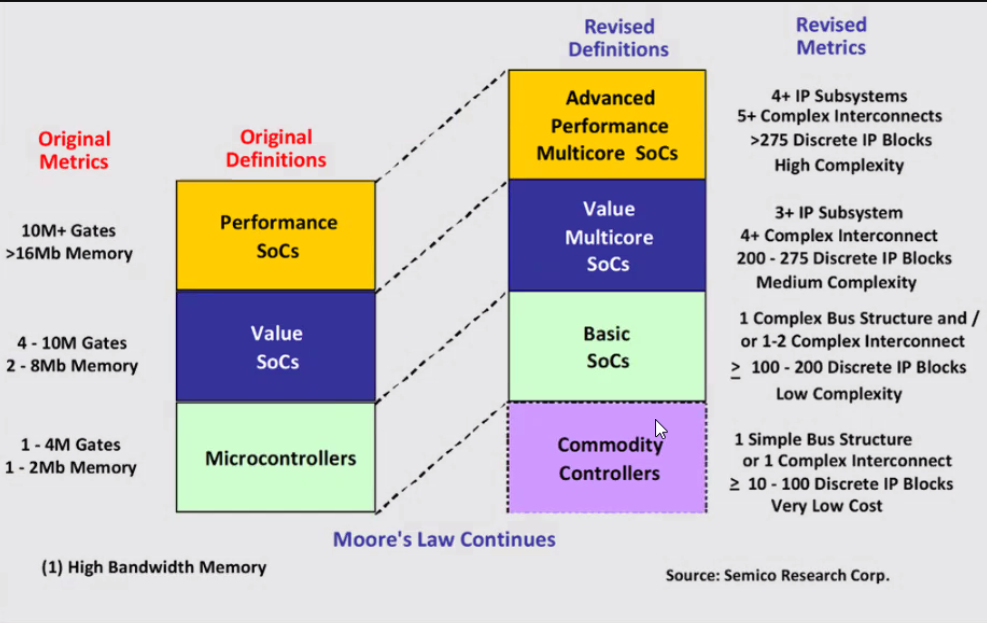

A kapuk, magok és perifériablokkok egyszerű számlálása már nem írja le az SoC-tervezésben rejlő teljesítménypotenciált. A Semico Research szerint az összekapcsolási sémák határozzák meg az SoC teljesítményszintek közötti vonalakat, és megnyílt egy új szint, ahol az összekapcsolások az egyszerű buszstruktúrákról a kifinomultabb sémákra változnak.

A Semico frissített definíciója három működő erőt ismer fel: a többmagos tervezések elterjedtségét, egy magasabb lécet az összetettnek tartott tervezéshez, és az ezt követő elmosódó határvonalat a „mikrokontroller” és a „SoC” között. A Semico legújabb nézetében a kapunak számító mérőszám fogalma eltűnik, mivel egy modern processzormag több kaput is magával húzhat. A komplexitás az összekapcsolások függvényévé válik, amely alrendszerekkel és különféle IP-blokkokkal változik.

SoC teljesítményszintek, kép a Semico Research Corp. jóvoltából.

Ahol egy egyszerű busz megteszi, valószínűleg egyetlen processzormaggal és alacsony terhelésű perifériákkal rendelkező alkatrészt, amely nem folyamatosan verseng a buszért, ott a Semico áruvezérlő réteget lát. Minden ezen felül SoC lesz, feltehetően legalább néhány perifériával, amely a chipen belüli sávszélességért és a processzormag(ok) figyeleméért küzd. A magasabb SoC szintek több maggal és több IP-alrendszerrel rendelkeznek, mindegyik hangolt összekapcsolási technológiával.

A NoC-k több protokollt és alrendszert vesznek fel

A RISC-V gyorsan feljebb lépett ezeken a teljesítményszinteken, ahogy egyre erősebb magok jelentek meg, és nem kevésbé alkalmazható a Semico skála alsó végén. Előfordulhat azonban, hogy a RISC-V tervezői kevesebb tapasztalattal rendelkeznek a magasabb szinteken látható összetett összekapcsolási sémák terén. „A TileLink lehet az első gondolat a RISC-V összekapcsolásnál, de bonyolultabb forgatókönyvekben nehéz lehet használni” – mondja Frank Schirrmeister, az Arteris megoldásokért és üzletfejlesztésért felelős alelnöke.

A NoC szuperereje abban rejlik, hogy különböző protokollokat használva képes alrendszereket összekapcsolni, és az SoC tervezők valószínűleg több, akár közepes bonyolultságú protokollba is belefutnak. Az AXI kiegyenlítette a játékteret az egyszerű IP-blokk-kapcsolatok számára. A többmagos megoldások közös feldolgozási blokkokkal gyorsítótár-koherenciát követelnek meg, így létrejön a CHI protokoll. Az I/O memóriamegosztás elősegítette a gyorsabb CXL összeköttetés kialakítását. „Amikor eljött az ideje, hogy együtt optimalizáljuk a számítást és az átvitelt különféle alrendszerekkel és protokollokkal, a NoC jobb megoldás” – folytatja Schirrmeister.

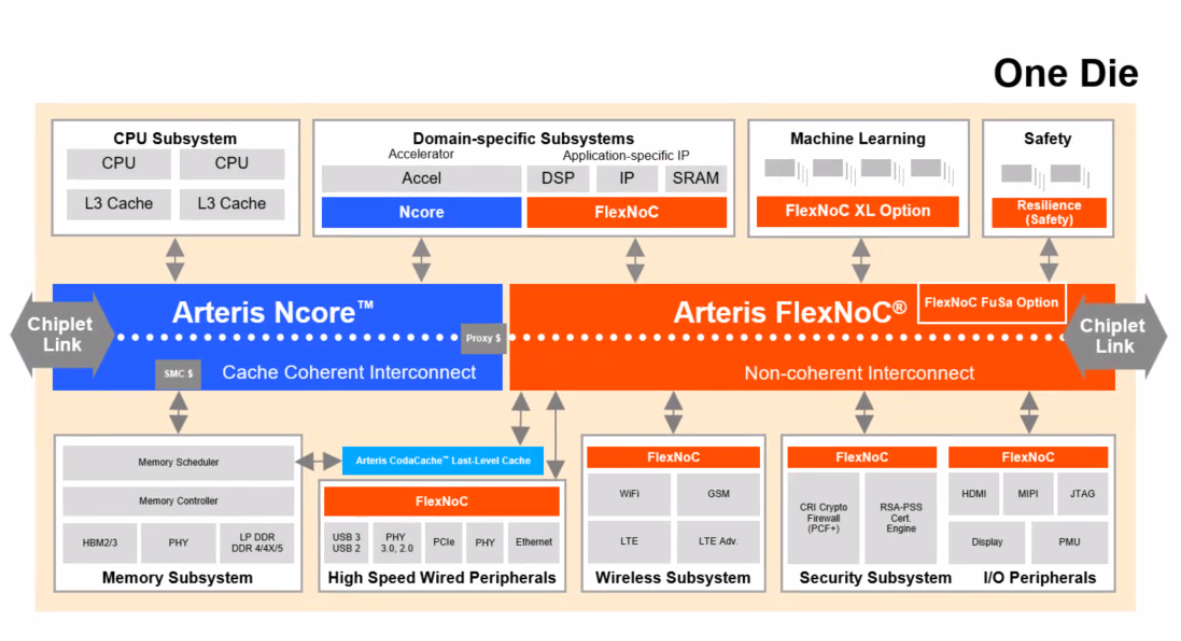

Hogyan nézhet ki a RISC-V magok és a NoC-k párosítása? Az Arteris ügyfele, a Tenstorrent bepillantást enged a lehetőségekbe. A közelmúltban egy újrafelhasználható chiplet létrehozására törekedtek, amely egyesíti a RISC-V magokat, a gépi tanulási gyorsító IP-címet és a sok szélső AI-alkalmazásban megtalálható szabványos perifériákat. Méretben az egyformájú megvalósítás az alábbi diagramhoz hasonlóan nézhet ki, az Arteris Ncore gyorsítótár-koherens összeköttetést és az Arteris FlexNoC nem koherens összeköttetés több szegmensét használva.

kép az Arteris jóvoltából

Az intelligens memóriavezérlő (SMC) nagy teljesítményű, szerver szintű memóriakapcsolatot biztosít a memóriaigényes alkalmazásokban. A névtelen „chiplet link” lehet az UCIe, egy viszonylag új specifikáció, amelyet szorosabb chiplet-integrációra optimalizáltak. Amikor új alrendszer-összeköttetések jelennek meg, a NoC egy részének adaptálása jobban kezelhető, mint a teljes chip-szintű struktúra feldarabolása.

A RISC-V magok és a NoC-k párosítása csökkenti a kockázatot és a forgalomba hozatali időt

Ha ez a diagram bonyolultnak tűnik, és adott, akkor talán a legtöbb RISC-V alkalmazás jelenleg nem olyan bonyolult, gondolja át a következőt: a chipletek már sokkal magasabbra késztetik az integrációt. A mai fejlett RISC-V többmagos alkatrész a jövő évi SoC értéke lesz, ahogy az innováció felgyorsul.

Az Arteris Ncore és Arteris FlexNoC fejlesztőeszközök RTL-t adnak ki a megvalósításhoz, számos előnnyel. A fizikai NoC-becslés egyszerű az EDA-munkafolyamatokban. A NoC paraméterek beállításai, például a folyamatszakaszok száma szintén néhány kattintással elérhetők az EDA eszközökben. Az alrendszer-protokoll hozzáadásához fent említett módosítások szintén könnyen végrehajthatók. „A csúcskategóriában a felhasználók azonnal hozzáférhetnek a NoC-szakértelemhez” – mondja Schirrmeister. „Eszközeink a legalacsonyabb szinten könnyen használhatók az első lépéses siker érdekében, és növekedési pályát biztosítanak az ambiciózusabb jövőbeli projektekhez, összetett összeköttetésekkel.”

A RISC-V magok és a NoC-k párosítása csökkenti annak kockázatát, hogy még egy IP-blokk kerüljön be a tervezésbe, és az összekapcsolás újratervezésének hullámzását idézze elő a chipen. Lecsökkenti a komplex SoC-konstrukciók forgalomba hozatali idejét is a barkácsolható összekapcsoló struktúrákhoz képest. Itt nem tárgyaltuk a NoC-k egyéb előnyeit, például a sávszélességet és az energiagazdálkodást, de a RISC-V-konstrukciókban a NoC-k esete erős, ha figyelembe vesszük a változatos protokollkeveréket.

Látogassa meg az Arteris weboldalát további információkért a NoC-okról és egyéb termékek.

Oszd meg ezt a bejegyzést ezen keresztül:

- SEO által támogatott tartalom és PR terjesztés. Erősödjön még ma.

- PlatoData.Network Vertical Generative Ai. Erősítse meg magát. Hozzáférés itt.

- PlatoAiStream. Web3 Intelligence. Felerősített tudás. Hozzáférés itt.

- PlatoESG. Carbon, CleanTech, Energia, Környezet, Nap, Hulladékgazdálkodás. Hozzáférés itt.

- PlatoHealth. Biotechnológiai és klinikai vizsgálatok intelligencia. Hozzáférés itt.

- Forrás: https://semiwiki.com/ip/arteris/336086-pairing-risc-v-cores-with-nocs-ties-soc-protocols-together/

- :van

- :is

- :nem

- :ahol

- $ UP

- a

- képesség

- felett

- gyorsulás

- hozzáférés

- megvalósítható

- Szerint

- át

- hozzáadásával

- kiigazítások

- fejlett

- előnyei

- AI

- már

- Is

- becsvágyó

- an

- és a

- Másik

- válaszok

- bármilyen

- bármi

- megjelenik

- alkalmazások

- VANNAK

- körül

- AS

- At

- figyelem

- el

- Sávszélesség

- bár

- BE

- válik

- Előnyök

- Jobb

- között

- Blokk

- Blocks

- busz

- üzleti

- üzlet fejlesztés

- de

- TUD

- eset

- kihívások

- változik

- változó

- csip

- kombinálása

- árucikk

- képest

- teljes

- bonyolult

- bonyolultság

- Kiszámít

- Csatlakozás

- kapcsolat

- kapcsolatok

- Fontolja

- figyelembe vett

- figyelembe véve

- tovább

- folyamatosan

- ellenőr

- Mag

- Corp

- tudott

- számolás

- létrehozása

- vevő

- dátum

- meghatározott

- definíció

- Kereslet

- Design

- tervezők

- tervek

- Fejlesztés

- fejlesztési eszközök

- különböző

- nehéz

- tárgyalt

- számos

- do

- vezetés

- minden

- könnyű

- él

- eredményesen

- felmerül

- csiszolókő

- végén

- belépés

- Egész

- Még

- tapasztalat

- szakvélemény

- kiterjesztések

- gyorsabb

- kevés

- mező

- harcoló

- vezetéknév

- áramlási

- Összpontosít

- koncentrál

- következő

- A

- erők

- talált

- őszinte

- ból ből

- funkció

- jövő

- Nyereség

- Gates

- Giving

- megpillant

- megadott

- Növekedés

- Legyen

- segített

- itt

- Magas

- nagy teljesítményű

- <p></p>

- azonban

- HTTPS

- kép

- azonnali

- végrehajtás

- in

- információ

- Innováció

- helyette

- integráció

- összekötő

- összeköti

- bele

- IP

- IT

- ITS

- éppen

- legutolsó

- elindítja

- legkevésbé

- kevesebb

- mint

- Valószínű

- vonal

- vonalak

- hosszabb

- néz

- hasonló

- MEGJELENÉS

- Elő/Utó

- alacsonyabb

- vezetés

- sok

- max-width

- Lehet..

- talán

- Memory design

- említett

- metrikus

- keverje

- közepesen

- modern

- Módosítások

- több

- a legtöbb

- áthelyezve

- sok

- többszörös

- kell

- Új

- következő

- nem

- fogalom

- Most

- szám

- of

- on

- ONE

- nyitott

- optimalizált

- or

- Más

- mi

- teljesítmény

- Béke

- párosítás

- paraméter

- rész

- ösvény

- mert

- teljesítmény

- kerületi

- perifériák

- fizikai

- vedd

- választás

- csővezeték

- Plató

- Platón adatintelligencia

- PlatoData

- játszani

- játék

- lehetőségek

- állás

- potenciális

- hatalom

- erős

- Processzor

- Termékek

- projektek

- protokoll

- protokollok

- ad

- biztosít

- amely

- gyorsan

- készségesen

- új

- elismeri

- újratervezés

- csökkenti

- viszonylag

- kutatás

- újrahasználható

- jobb

- Ripple

- Emelkedik

- Kockázat

- futás

- s

- azt mondja,

- Skála

- forgatókönyvek

- rendszerek

- Rész

- látott

- lát

- szegmensek

- kiválasztása

- számos

- Alak

- megosztás

- Egyszerű

- óta

- egyetlen

- okos

- megoldások

- Megoldások

- néhány

- kifinomult

- leírás

- állapota

- standard

- egyértelmű

- erős

- struktúra

- struktúrák

- későbbi

- siker

- ilyen

- szuperhatalom

- Technológia

- mint

- hogy

- A

- azok

- Ezek

- Harmadik

- ezt

- gondoltam

- három

- tier

- Ties

- szorosabb

- idő

- nak nek

- mai

- együtt

- szerszámok

- szállítható

- kioldás

- NÉVTELEN

- frissítve

- használ

- Felhasználók

- segítségével

- érték

- különféle

- változó

- keresztül

- Megnézem

- vp

- we

- weboldal

- Mit

- Mi

- amikor

- lesz

- val vel

- Munka

- munkafolyamat

- zephyrnet