A Banias Labs egy félvezetőgyártó cég, amely infrastrukturális megoldásokat fejleszt a következő generációs kommunikációhoz. Célpiaca a nagy teljesítményű számítástechnikai infrastruktúra piaca, beleértve a hiperskálájú adatközpontokat, hálózatokat, mesterséges intelligenciát, optikai modulokat és Ethernet switch SoC-ket a feltörekvő nagy teljesítményű számítástechnikai tervekhez. Ezek az SoC-k nagy sebességű Ethernet-terveket és alacsony késleltetésű megoldásokat igényelnek a nagyobb rendszerteljesítmény és a piacra kerülés felgyorsítása érdekében. A vállalat egy optikai DSP SoC-t fejlesztett ki 5 nm-es folyamattechnológián, hogy megfeleljen a piac követelményeinek.

![]()

Az optikai DSP SoC egy speciális típusú rendszer-chip (SoC), amelyet nagy sebességű optikai kommunikációs rendszerekben való használatra terveztek. A DSP-n kívül az optikai DSP SoC jellemzően nagy sebességű interfész IP-blokkokat tartalmaz, például Ethernet PHY IP, PCIe IP és DDR memóriavezérlőket. Az ilyen típusú SoC-k nagy sebességű adatátvitelt tesznek lehetővé alacsony késleltetési idővel a valós idejű jelfeldolgozás érdekében. Úgy tervezték, hogy minimálisra csökkentsék az energiafogyasztást, így ideálisak olyan alkalmazásokhoz, amelyek hatékony működést igényelnek, csökkentett hőmérsékleti problémákkal. Az előnyökkel kihívások is járnak. Az optikai kommunikációs rendszerek speciális követelményei az optikai DSP SoC tervezését nagyobb kihívást jelentenek, mint a hagyományos SoC tervezését.

Megvalósítási kihívások

A kihívások a tervezés összetettsége, a szigorú teljesítmény- és teljesítménykövetelmények, valamint a különféle iparági szabványok teljesítésének szükségessége körül forognak. Több IP blokk integrálása, beleértve a DSP processzort, az Ethernet PHY IP-t és más egyedi blokkokat, gondos tervezést és érvényesítést igényel. További nagy sebességű interfészek, mint például a PCIe és a DDR, tovább bonyolítják a tervezést. A rendszerben található nagy sebességű interfészek és több IP-blokk jeltorzítást, áthallást és elektromágneses interferenciát okozhat, ami hatással lehet a rendszer teljesítményére és megbízhatóságára. A jel- és teljesítményintegritás-elemzést és -optimalizálást a tervezési ciklus korai szakaszában el kell végezni annak biztosítása érdekében, hogy a rendszer megfeleljen teljesítmény- és megbízhatósági követelményeinek. Végezetül, a piacra jutási idő követelményeinek teljesítése kihívást jelenthet. A nagy teljesítményű számítástechnikai infrastruktúra piaca gyorsan fejlődik, és az SoC fejlesztőcsapatoknak gyorsan kell elkészíteniük terveiket, hogy a versenytársak előtt maradjanak.

A First Pass Silicon siker elérése

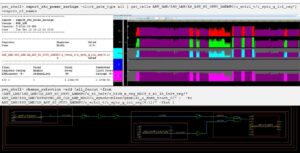

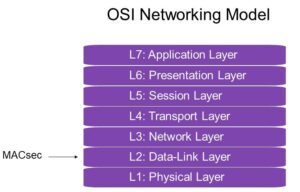

A fent említett kihívások leküzdése átfogó megközelítést igényel. A nagy teljesítményű, alacsony késleltetésű megoldások egyik kritikus összetevője az Ethernet PHY IP. Az Ethernet PHY IP felelős az SoC és az Ethernet hálózat közötti fizikai réteg interfészért. Az IP-nek támogatnia kell a nagy sebességű Ethernet interfészeket, beleértve a 10G, 25G, 40G, 50G, 100G, 200G, 400G és 800G-t, valamint alacsony késleltetést és alacsony energiafogyasztást kell biztosítania. Ezenkívül az IP-nek támogatnia kell különféle szabványokat, beleértve az IEEE 802.3-at és az Ethernet Alliance-t. Egy másik fontos elem az EDA tervezési csomag. Az EDA tervezési csomagjának átfogó megoldást kell nyújtania az SoC tervezésére és ellenőrzésére, beleértve a teljesítményoptimalizálást, a teljesítményelemzést, a területoptimalizálást és a hozamelemzést. Az EDA tervezési csomagja bizonyos mértékig olyan fejlett funkciókat tartalmaz, mint a mesterséges intelligencia (AI) és a gépi tanulás (ML), amelyek jobbak a termelékenység növeléséhez és a piacra kerülési idő csökkentéséhez.

A Synopsys felgyorsítja az első lépéses szilícium sikerét

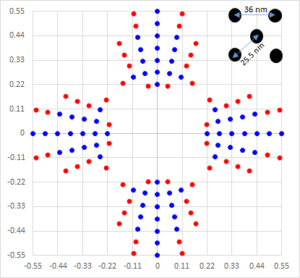

A Synopsys olyan megoldásokat kínál, amelyek megfelelnek a nagy teljesítményű számítástechnikai infrastruktúra piacán a SoC-ok fejlesztésének egyedi kihívásainak. A vállalat átfogó IP-megoldást kínál, amely magában foglalja az útválasztási megvalósíthatósági tanulmányt, a csomagolási hordozóra vonatkozó irányelveket, a jel- és tápegység-integritási modelleket, valamint az áthallás alapos elemzését. Ez elengedhetetlen az optikai DSP SoC fejlesztése során felmerülő jel- és energiaintegritási kihívások megoldásához. A Synopsys 112G Ethernet PHY IP alacsony késleltetést, rugalmas elérési hosszt és érettséget kínál az 5nm-es folyamattechnológiához, így ideális megoldást jelent a hyperscale adatközpontokhoz, hálózatokhoz, mesterséges intelligenciához, optikai modulokhoz és Ethernet switch SoC-okhoz. Ezenkívül a Synopsys egy EDA Design Suite-ot is kínál, amely kiváló minőségű eredményeket biztosít optimalizált teljesítmény, teljesítmény, terület és hozam mellett. A Synopsys mesterséges intelligencia által vezérelt EDA Design Suite megoldásokat kínál a rendszer teljesítményének növelésére és a piacra kerülés felgyorsítására, így a nagy teljesítményű számítástechnikai infrastruktúra piacán a sikeres megoldás elengedhetetlen elemévé válik.

Összegzésként

A Synopsys nagy teljesítményű, alacsony késleltetésű megoldásokat kínál, amelyek felgyorsítják a fejlett Ethernet-kapcsolók és hálózati SoC-k fejlesztését. Ha többet szeretne megtudni a Synopsys átfogó IP-megoldásairól, az átfogó EDA Design Suite-ról és az AI-Enhanced EDA Suite-ról, látogassa meg a következő oldalakat.

A Synopsys átfogó IP megoldásai

A Synopsys AI-vezérelt EDA Design Suite

Is Read:

Multi-Die Systems: Évek óta a legnagyobb zavar a számítástechnikában

A sávszélesség iránti növekvő éhség táplálása a nagy sebességű Ethernettel

Oszd meg ezt a bejegyzést ezen keresztül:

- SEO által támogatott tartalom és PR terjesztés. Erősödjön még ma.

- Platoblockchain. Web3 metaverzum intelligencia. Felerősített tudás. Hozzáférés itt.

- A jövő pénzverése – Adryenn Ashley. Hozzáférés itt.

- Forrás: https://semiwiki.com/ip/327703-synopsys-accelerates-first-pass-silicon-success-for-banias-labs-networking-soc/

- :van

- :is

- a

- Rólunk

- felett

- gyorsul

- gyorsul

- mellett

- További

- Ezen kívül

- cím

- fejlett

- előnyei

- előre

- AI

- Szövetség

- Is

- an

- elemzés

- és a

- Másik

- alkalmazások

- megközelítés

- VANNAK

- TERÜLET

- körül

- mesterséges

- mesterséges intelligencia

- Mesterséges intelligencia (AI)

- AS

- At

- Sávszélesség

- BE

- Jobb

- között

- Legnagyobb

- Blocks

- fellendítésére

- TUD

- óvatos

- Központ

- kihívások

- kihívást

- hogyan

- közlés

- távközlés

- vállalat

- verseny

- bonyolultság

- összetevő

- alkatrészek

- átfogó

- számítástechnika

- fogyasztás

- teremt

- kritikai

- szokás

- ciklus

- dátum

- Adatközpont

- szállít

- szállít

- Design

- tervezett

- tervezés

- tervek

- fejlett

- fejlesztése

- Fejlesztés

- fejleszt

- Zavar

- Korai

- hatékony

- csiszolókő

- lehetővé

- fokozott

- biztosítására

- alapvető

- fejlődik

- szembe

- GYORS

- Jellemzők

- Végül

- vezetéknév

- rugalmas

- következő

- A

- ból ből

- további

- Növekvő

- irányelvek

- nagy teljesítményű

- jó minőségű

- HTML

- HTTPS

- éhség

- ideális

- IEEE

- kép

- Hatás

- parancsoló

- fontos

- in

- magában foglalja a

- Beleértve

- <p></p>

- ipar

- ipari szabványok

- Infrastruktúra

- integráció

- sértetlenség

- Intelligencia

- Felület

- interfészek

- IP

- kérdések

- IT

- ITS

- Labs

- Késleltetés

- réteg

- TANUL

- tanulás

- Elő/Utó

- gép

- gépi tanulás

- csinál

- Gyártás

- piacára

- érettség

- max-width

- Találkozik

- találkozó

- Memory design

- említett

- ML

- modellek

- modul

- több

- többszörös

- Szükség

- hálózat

- hálózatba

- következő generációs

- of

- Ajánlatok

- on

- ONE

- működés

- optimalizálás

- optimalizált

- Más

- saját

- csomagolás

- elhalad

- teljesítmény

- fizikai

- Plató

- Platón adatintelligencia

- PlatoData

- állás

- hatalom

- folyamat

- feldolgozás

- Processzor

- termelékenység

- ad

- biztosít

- gyorsan

- gyorsan

- el

- Olvass

- real-time

- Csökkent

- szabályos

- megbízhatóság

- szükség

- követelmények

- megköveteli,

- felelős

- Eredmények

- Kockázat

- félvezető

- Jel

- Szilícium

- megoldások

- Megoldások

- specializált

- szabványok

- tartózkodás

- Tanulmány

- siker

- sikeres

- ilyen

- kíséret

- támogatás

- kapcsoló

- rendszer

- Systems

- cél

- csapat

- Technológia

- mint

- hogy

- A

- azok

- Őket

- termikus

- Ezek

- ők

- ezt

- nak nek

- is

- transzferek

- típusok

- jellemzően

- egyedi

- használ

- érvényesítés

- különféle

- ellenőrzése

- keresztül

- Látogat

- ami

- val vel

- Hozam

- A te

- zephyrnet