Si l’on regarde l’expansion de l’industrie des semi-conducteurs au cours des 25 dernières années, l’adoption de la conception IP dans chaque application semble être l’un des principaux facteurs de succès, avec un développement incroyable de la technologie du silicium d’un facteur x100, passant de 250 nm en 2018 à 3 nm (si et non 2 nm) en 2023. Nous prévoyons que le passage à une architecture basée sur des chipsets jouera bientôt le même rôle que l'architecture basée sur des puces SoC et l'utilisation massive de la conception IP ont joué dans les années 2000.

La question est de savoir comment prédire avec précision le calendrier d’adoption des chipsets et quels seront les principaux catalyseurs de cette révolution. Nous verrons si la diffusion de la théorie de l’innovation peut être utile pour affiner une prédiction et déterminer quel type d’application en sera le moteur. Les spécifications standard du protocole d'interconnexion puce à puce permettant une adoption rapide par l'industrie, la conduite d'applications telles que l'IA ou le processeur d'application pour smartphone semblent rapidement être le principal catalyseur, mais l'efficacité des outils EDA ou l'emballage de nouvelles technologies et la création d'usines dédiées, entre autres, sont certainement essentiels.

Introduction : émergence de la technologie chiplet

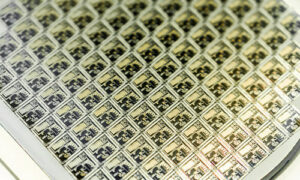

Au cours de la décennie 2010, les avantages de la loi de Moore ont commencé à s'effondrer. La loi de Moore stipulait que la densité des transistors doublait tous les deux ans, le coût du calcul diminuerait d'un montant correspondant de 50 %. Le changement dans la loi de Moore est dû à la complexité accrue de la conception et à l'évolution de la structure des transistors, des dispositifs planaires aux Finfets. Les Finfets ont besoin de plusieurs motifs pour la lithographie afin d'atteindre des dimensions de dispositif inférieures à 20 nm.

À la fin de cette décennie, les besoins informatiques ont explosé, principalement en raison de la prolifération des centres de données et de la quantité de données générées et traitées. En fait, l’adoption de l’intelligence artificielle (IA) et de techniques telles que l’apprentissage automatique (ML) est désormais utilisée pour traiter un nombre toujours croissant de données et a conduit les serveurs à augmenter considérablement leur capacité de calcul. Les serveurs ont ajouté beaucoup plus de cœurs de processeur, ont intégré des GPU plus grands utilisés exclusivement pour le ML, qui ne sont plus utilisés pour les graphiques, et ont intégré des accélérateurs d'IA ASIC personnalisés ou un traitement d'IA complémentaire basé sur FPGA. Les premières conceptions de puces d'IA ont été mises en œuvre à l'aide de SoC monolithiques plus grands, certains d'entre eux atteignant la limite de taille imposée par le réticule, environ 700 mm.2.

À ce stade, la désagrégation en un SoC plus petit ainsi que divers chipsets de calcul et d’E/S semble être la bonne solution. Plusieurs fabricants de puces, comme Intel, AMD ou Xilinx, ont choisi cette option pour les produits entrant en production. Dans l'excellent livre blanc du Linley Group, « Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small », il a été démontré que cette option entraîne de meilleurs coûts par rapport aux SoC monolithiques, en raison de l'impact sur le rendement d'un SoC plus grand. Ces fabricants de puces ont conçu des chipsets homogènes, mais l'émergence et l'adoption de normes d'interconnexion telles que l'IP Universal Chiplet Interconnect Express (UCIe) facilitent l'adoption de chipsets hétérogènes.

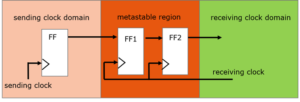

L’évolution des normes de protocole les plus récentes et plus rapides s’accélère alors que l’industrie continue de demander des performances plus élevées. Malheureusement, les différentes normes ne sont pas synchronisées par une seule organisation. Les nouvelles normes PCIe peuvent arriver un an (ou plus) plus tôt ou plus tard que la nouvelle norme de protocole Ethernet. L'utilisation d'une intégration hétérogène permet aux fournisseurs de silicium de s'adapter à un marché en évolution rapide en modifiant uniquement la conception du chipset concerné. Étant donné que la fabrication de conceptions de SoC avancées nécessite des dépenses d'investissement massives pour les nœuds de processus de 5 nm, 4 nm ou 3 nm, l'impact des architectures de puces est énorme pour stimuler l'innovation future dans le domaine des semi-conducteurs.

La conception hétérogène des chiplets nous permet de cibler différentes applications ou segments de marché en modifiant ou en ajoutant uniquement les chiplets pertinents tout en gardant le reste du système inchangé. De nouveaux développements pourraient être lancés plus rapidement sur le marché, avec des investissements nettement inférieurs, car la refonte n'impactera que le substrat du boîtier utilisé pour loger les chipsets. Par exemple, le chipset de calcul peut être repensé de TSMC 5 nm à TSMC 3 nm pour intégrer un cache L1 plus grand ou un processeur ou un nombre de cœurs de processeur plus performants, tout en gardant le reste du système inchangé. Les chipsets intégrant SerDes peuvent être repensés pour des débits plus rapides sur de nouveaux nœuds de processus offrant plus de bande passante IO pour un meilleur positionnement sur le marché.

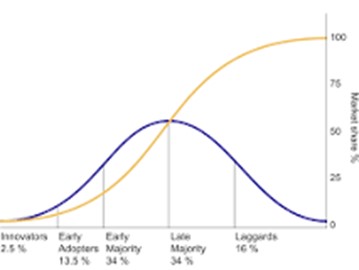

L'utilisation d'un chiplet hétérogène offrira un meilleur délai de mise sur le marché (TTM) lors de la mise à jour du système, en réutilisant la partie du système sans modification si elle est conçue en chiplet. Ce sera également un moyen de minimiser les coûts en conservant certains chipsets fonctionnels sur des nœuds moins avancés, moins chers que les plus avancés. Mais la principale question est de savoir quand la technologie des chipsets créera un segment important du marché des semi-conducteurs ? Nous passerons en revue l’historique de l’adoption de la propriété intellectuelle, car le chiplet et la propriété intellectuelle sont similaires, les deux doivent briser le syndrome des NIH pour réussir. Nous extrairons les principales causes de l'adoption des chiplets et construirons une prévision, en utilisant la théorie de l'innovation et la catégorie définie (Innovateurs, Early Adopters, etc. voir la figure ci-dessous).

Nous examinerons l’adoption de l’IP des processeurs ARM de 1991 à 2018 et l’historique de l’adoption de l’IP de 1995 à 2027, et vérifierons comment ce taux d’adoption colle à la théorie de l’innovation.

Nous expliquerons pourquoi l'adoption des chiplets sera stimulée, en passant en revue les raisons liées à la technologie et au marketing :

- Du SoC basé sur IP au système basé sur chiplet

- Interopérabilité, grâce à la norme de protocole privilégiée d'interconnexion chiplet

- Expliquer pourquoi les interfaces IP haut de gamme sont essentielles à l'adoption des Chiplets

- Défis liés au design à résoudre.

- Enfin et surtout, l'investissement réalisé par la fonderie

Enfin, nous pouvons élaborer une prévision provisoire de l’adoption des chipsets, basée sur la théorie de l’innovation. Il suffit de mentionner que le secteur vient de passer à la phase des « Early Adopters », voyant de nombreux fournisseurs d'IP et de chipsets servir le HPC et l'IA.

Si vous téléchargez le papier blanc, vous apprécierez tout le texte et les nombreuses images, dont certaines ont été créées exclusivement pour cet ouvrage.

By Eric Estève (PhD.) Analyste, Propriétaire IPnest

Alphawave a sponsorisé la création de ce livre blanc, mais les opinions et analyses sont celles de l'auteur. L'article peut être trouvé ici :

https://awavesemi.com/resource/will-chiplet-adoption-to-mimic-ip-adoption/

Lisez aussi:

Interface IP en 2022 : 22 % de croissance sur un an toujours axée sur les données

Partagez cet article via:

- Contenu propulsé par le référencement et distribution de relations publiques. Soyez amplifié aujourd'hui.

- PlatoData.Network Ai générative verticale. Autonomisez-vous. Accéder ici.

- PlatoAiStream. Intelligence Web3. Connaissance Amplifiée. Accéder ici.

- PlatonESG. Carbone, Technologie propre, Énergie, Environnement, Solaire, La gestion des déchets. Accéder ici.

- PlatoHealth. Veille biotechnologique et essais cliniques. Accéder ici.

- La source: https://semiwiki.com/chiplet/339927-will-chiplet-adoption-mimic-ip-adoption/

- :possède

- :est

- :ne pas

- $UP

- 1

- 1995

- 200

- 2018

- 2022

- 2023

- 25

- a

- A Propos

- accélérateurs

- atteindre

- adapter

- ajoutée

- ajoutant

- adopteurs

- Adoption

- Avancée

- AI

- Données d'IA

- Tous

- Permettre

- permet

- aussi

- AMD

- parmi

- montant

- selon une analyse de l’Université de Princeton

- analyste

- ainsi que

- A PART

- apparaît

- Application

- applications

- architecture

- SONT

- BRAS

- article

- artificiel

- intelligence artificielle

- Intelligence artificielle (AI)

- AS

- ase

- demandant

- At

- auteur

- Bande passante

- basé

- BE

- devenez

- a commencé

- va

- ci-dessous

- avantages.

- Améliorée

- Big

- Boosté

- tous les deux

- Pause

- construire

- mais

- by

- cachette

- CAN

- Compétences

- capital

- Catégories

- les causes

- Assurément

- globaux

- Change

- en changeant

- moins chère

- vérifier

- puce

- chips

- comment

- par rapport

- complémentaire

- complexité

- calcul

- informatique

- considérant

- Correspondant

- Prix

- Costs

- pourriez

- Processeur

- engendrent

- créée

- création

- Customiser

- données

- décennie

- dévoué

- défini

- densité

- Conception

- un

- Avec nos Bagues Halo

- Déterminer

- Développement

- développements

- Compatibles

- différent

- La diffusion

- dimensions

- Doublé

- download

- motivation

- driver

- conduite

- deux

- pendant

- Plus tôt

- "Early Bird"

- adopteurs précoces

- assouplissement

- risque numérique

- efficace

- intégré

- émergence

- activateur

- permettant

- fin

- jouir

- etc

- de plus en plus

- Chaque

- évolution

- exemple

- excellent

- uniquement au

- avec des données

- Expliquer

- express

- extrait

- fait

- facteur

- facteurs

- Automne

- RAPIDE

- plus rapide

- Figure

- Pour

- Prévision

- prévoir

- trouvé

- fpga

- De

- fonctionnel

- avenir

- Gain

- généré

- obtention

- aller

- GPU

- graphique

- Réservation de groupe

- Croissance

- Vous avez

- utile

- ici

- Haut de gamme

- augmentation

- Histoire

- Villa

- Comment

- How To

- hpc

- HTTPS

- ia

- if

- Impact

- mis en œuvre

- imposé

- in

- increased

- croissant

- l'incroyable

- industrie

- Innovation

- innovateurs

- intégrer

- des services

- Intégration

- l'intégration

- Intel

- Intelligence

- Interfaces

- développement

- un investissement

- IP

- IT

- jpg

- juste

- en gardant

- ACTIVITES

- plus importantes

- Nom de famille

- plus tard

- lancé

- Droit applicable et juridiction compétente

- Conduit

- apprentissage

- au

- LED

- moins

- comme

- LIMIT

- plus long

- Style

- baisser

- click

- machine learning

- LES PLANTES

- Entrée

- majeur

- Décideurs

- de nombreuses

- Marché

- Stratégie

- massif

- mentionner

- minimiser

- ML

- Monolithique

- PLUS

- (en fait, presque toutes)

- la plupart

- Bougez

- déménagé

- plusieurs

- Besoin

- Besoins

- Nouveauté

- Les nouvelles technologies

- Plus récent

- NIH

- aucune

- nœuds

- maintenant

- nombre

- nombreux

- of

- code

- offrant

- on

- ONE

- uniquement

- Avis

- Option

- or

- organisation

- Autres

- propriétaire

- paquet

- l'emballage

- Papier

- partie

- performant

- effectuer

- phase

- phd

- PHP

- cueillette

- PHOTOS

- Platon

- Intelligence des données Platon

- PlatonDonnées

- Jouez

- joué

- plus

- Point

- positionnement

- Post

- Alimentation

- précisément

- prévoir

- prédiction

- préféré

- processus

- traité

- traitement

- Processeur

- Vidéo

- Produits

- protocole

- fournisseurs

- question

- plus rapidement

- vite.

- Nos tests de diagnostic produisent des résultats rapides et précis sans nécessiter d'équipement de laboratoire complexe et coûteux,

- Tarif

- Tarifs

- atteindre

- Lire

- Les raisons

- reconcevoir

- redessiné

- en relation

- pertinent

- rappel

- a besoin

- REST

- Avis

- examen

- Révolution

- bon

- Rôle

- même

- sur le lien

- voir

- semble

- clignotant

- segments

- Sélectionner

- semi-conducteur

- serveurs

- service

- plusieurs

- montré

- significative

- de façon significative

- Silicium

- similaires

- unique

- Taille

- faibles

- smartphone

- sur mesure

- RÉSOUDRE

- quelques

- disponible

- Space

- caractéristiques

- vitesse

- Sponsorisé

- Standard

- Normes

- A déclaré

- bâton

- Encore

- structure

- succès

- réussi

- combustion propre

- Système

- Target

- techniques

- Les technologies

- Technologie

- texte

- que

- à

- qui

- La

- leur

- Les

- théorie

- Ces

- this

- ceux

- Avec

- calendrier

- à

- les outils

- top

- énorme

- TSMC

- deux

- type

- malheureusement

- Universel

- la mise à jour

- us

- utilisé

- d'utiliser

- en utilisant

- divers

- fournisseurs

- via

- était

- Façon..

- we

- ont été

- Quoi

- quand

- tout en

- blanc

- papier blanc

- why

- sera

- comprenant

- activités principales

- pourra

- an

- années

- Rendement

- you

- zéphyrnet