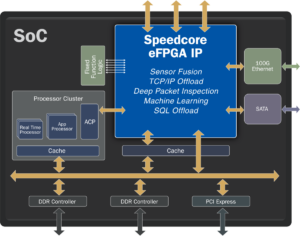

TSMC propose des services de fonderie depuis 1987 et son premier nœud 3 nm s'appelait N3 et a fait ses débuts en 2022 ; ils disposent désormais d'un nœud amélioré de 3 nm baptisé N3E qui a été lancé. Chaque nouveau nœud nécessite ensuite une IP soigneusement conçue, caractérisée et validée sur silicium pour garantir que les spécifications IP sont respectées et peuvent être utilisées en toute sécurité dans les conceptions SoC. Cette nouvelle IP doit couvrir un large éventail de fonctions, comme l'interface, la mémoire et la logique. Synopsys dispose d'une grande équipe IP qui a relevé le défi en créant une nouvelle IP pour le nœud TSMC N3E et en obtenant un succès de premier passage sur le silicium.

Interconnexion de chipsets

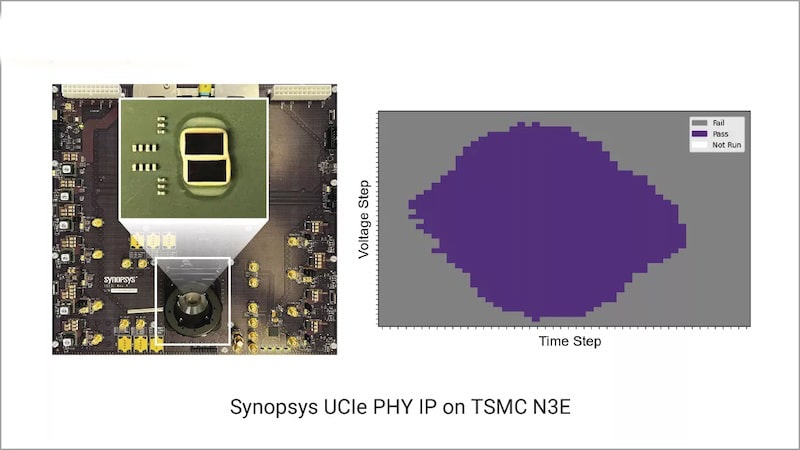

Les systèmes constitués de chipsets nécessitent une communication die-to-die, et c'est là qu'intervient la norme UCIe.o jouer. Synopsys est membre contributeur du Consortium UCIe, et ils offrent une propriété intellectuelle à la fois pour un UCIe Cpoussette et un UCIe PHY dans le nœud TSMC N3E.

Le IP PHY UCIe a obtenu ses premiers résultats sur silicium en août 2023, affichant des débits de données de 16 Go/s et évolutifs jusqu'à 24 Go/s par canal. L'efficacité énergétique est de 0.3 pJ/bit.

IP physique

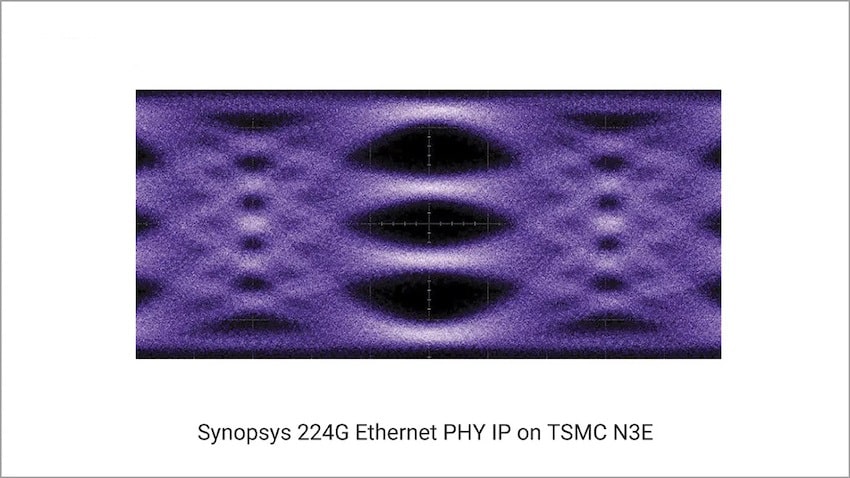

L'IEEE a approuvé la norme 802.3 pour Ethernet en 1983, une norme assez étendue, tandis que le Synopsys 224G Ethernet PHY IP a connu son premier succès en matière de silicium Août 2023. Les ingénieurs réseau examinent le diagramme de l'œil pour voir le codage PAM-4. Les niveaux de gigue ont dépassé les spécifications des normes IEEE 802.3 et OIF.

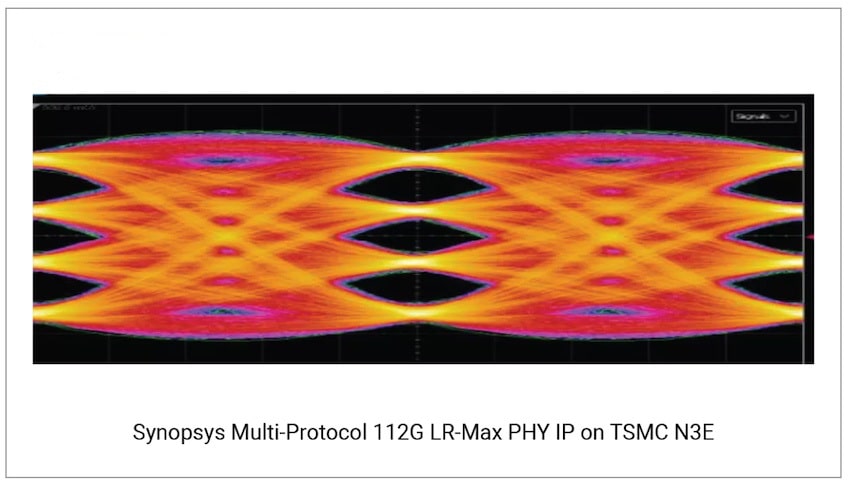

Prenant en charge les normes telles que PCI Express 6.0, Ethernet 400G/800G, CCIX, CXL2.0/3.0, JESD204 et CPRI, il existe le Synopsys IP PHY multiprotocole 112G. Les ingénieurs peuvent combiner cette IP PHY avec un MAC et un PCS pour créer un bloc Ethernet 200G/400G/800G.

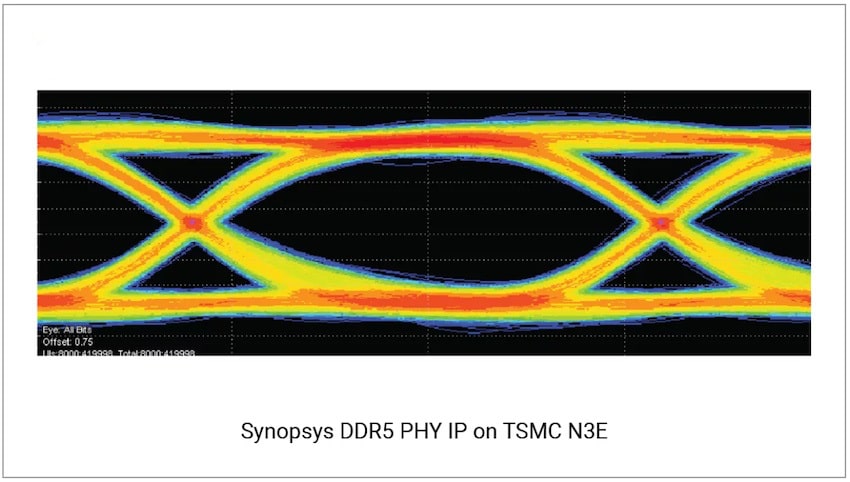

La SDRAM et les modules de mémoire peuvent utiliser le Synopsys DDR5 PHY-IP sur TSMC N3E pour atteindre des taux de transfert allant jusqu'à 8400 XNUMX Mbps. Vous pouvez voir l’œil grand ouvert et les marges claires pour cette IP fonctionnant à grande vitesse.

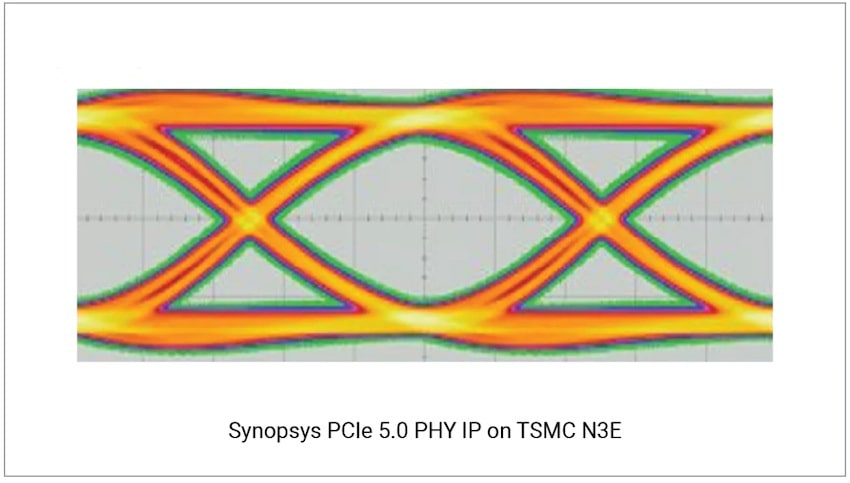

La norme PCI Express a débuté en 2003 et a été continuellement mise à jour pour répondre aux demandes croissantes du cloud computing, du stockage et de l'IA. PCIe 5.0 est désormais pris en charge à l'aide de l'IP PHY Synopsys PCIe 5.0. Le premier silicium sur TSMC N3E a montré des vitesses de fonctionnement de 32 GT / s, et il a réussi les tests de conformité.

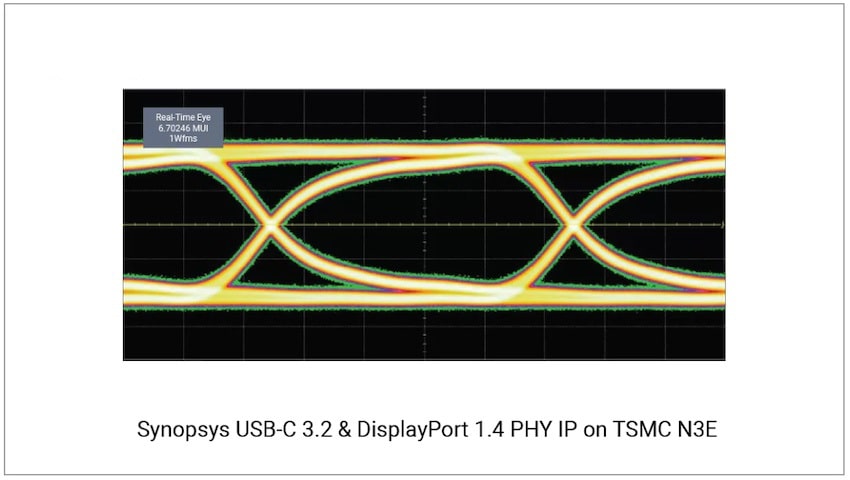

J'utilise l'USB-C sur mon MacBook Pro, iPad Pro et mon téléphone Android depuis des années maintenant. Synopsys prend désormais en charge USB-C 3.2 et DisplayPort 1.4 PHY-IP dans le dernier processus TSMC. Avec cette IP, les utilisateurs peuvent connecter jusqu'à des écrans 8K Ultra Haute Définition.

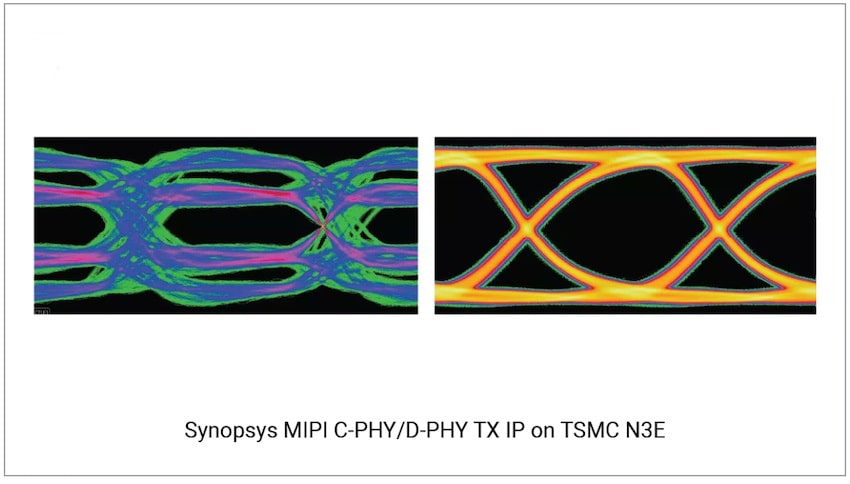

Les fabricants de smartphones ont standardisé le protocole MIPI il y a des années comme moyen efficace de connecter des caméras, et le Synopsys MIPI C-PHY IP/D-PHY IP peut fonctionner à 6.5 Gb/s par voie et 6.5 Gb/s par trio. Le C-PHY IP prend en charge la version 2.0 et le D-PHY IP2.1.

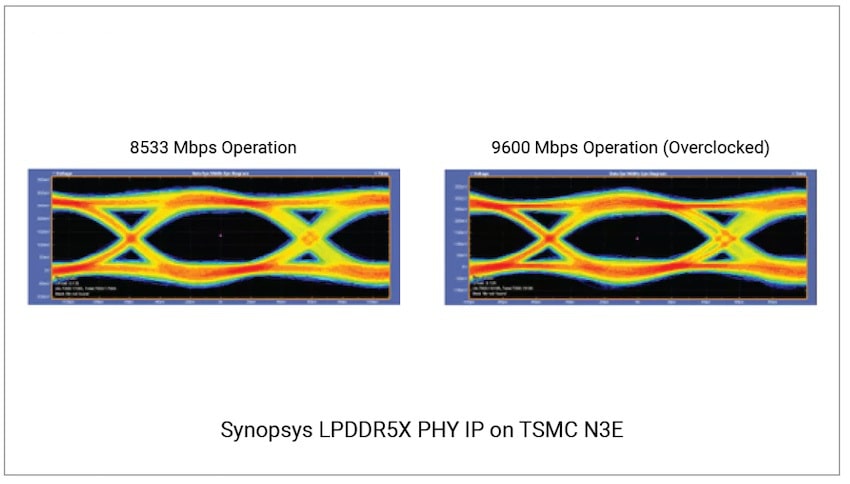

La dernière spécification du contrôleur DRAM synchrone est LPDDR5X, prenant en charge des vitesses de transfert de données allant jusqu'à 8533 33 Mbps, soit une amélioration de 5 % par rapport à la mémoire LPDDRXNUMX. Le Contrôleur Synopsys LPDDR5X/5/4X est éprouvé en silicium et prêt à être conçu avec.

Bibliothèques logiques et mémoires

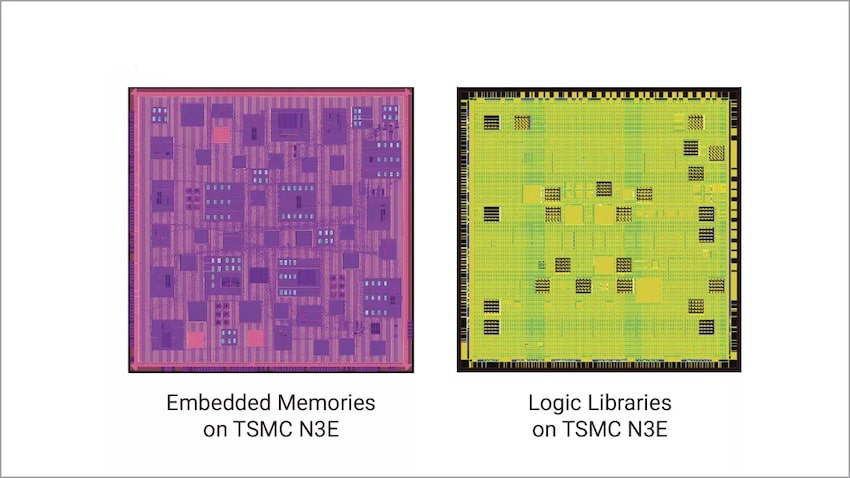

Jusqu'à la moitié de la surface d'un SoC peut être constituée de mémoires. La bonne nouvelle est donc que la IP de la Fondation Synopsys vous permet d'ajouter rapidement des mémoires et des cellules de bibliothèque logique dans une nouvelle conception. Voici les schémas des puces de test de Synopsys sur le nœud TSMC N3E pour les mémoires et les bibliothèques logiques.

Résumé

TSMC et Synopsys ont très bien collaboré au fil des ans, et ce partenariat s'étend désormais au nœud N3E où les concepteurs de SoC peuvent trouver une IP testée sur silicium pour les interfaces, les mémoires et la logique. La puissance, les performances et le rendement semblent attrayants pour le N3E, la technologie est donc prête pour vos conceptions les plus exigeantes. Démarrer une conception avec N3E vous offre également un chemin plus rapide pour migrer vers le processus N3P.

Au lieu de créer toute votre propre IP à partir de zéro, ce qui allongera votre calendrier, nécessitera plus de ressources d'ingénierie et augmentera les risques, pourquoi ne pas jeter un œil à ce que Synopsys a à offrir dans une large gamme de blocs IP éprouvés sur silicium.

Blogs connexes

Partagez cet article via:

- Contenu propulsé par le référencement et distribution de relations publiques. Soyez amplifié aujourd'hui.

- PlatoData.Network Ai générative verticale. Autonomisez-vous. Accéder ici.

- PlatoAiStream. Intelligence Web3. Connaissance Amplifiée. Accéder ici.

- PlatonESG. Carbone, Technologie propre, Énergie, Environnement, Solaire, La gestion des déchets. Accéder ici.

- PlatoHealth. Veille biotechnologique et essais cliniques. Accéder ici.

- La source: https://semiwiki.com/ip/336595-tsmc-n3e-is-ready-for-designs-thanks-to-ip-from-synopsys/

- :possède

- :est

- :ne pas

- :où

- $UP

- 1

- 2022

- 2023

- 8k

- a

- atteindre

- la réalisation de

- ajouter

- depuis

- AI

- Tous

- permet

- aussi

- an

- et les

- android

- ,

- SONT

- Réservé

- AS

- At

- attrayant

- Août

- RETOUR

- BE

- était

- va

- Block

- Blocs

- tous les deux

- construire

- by

- appelé

- de CAMÉRAS de surveillance

- CAN

- prudemment

- Cellules

- challenge

- Développement

- caractérisé

- puce

- clair

- le cloud

- le cloud computing

- collaboré

- combiner

- vient

- Communication

- Sociétés

- conformité

- informatique

- NOUS CONTACTER

- continuellement

- contributeur

- contrôleur

- couverture

- La création

- données

- a fait ses débuts

- définition

- exigeant

- demandes

- Conception

- un

- designers

- Avec nos Bagues Halo

- diagrammes

- affiche

- doublé

- efficace

- efficace

- ENGINEERING

- Les ingénieurs

- améliorée

- assurer

- Chaque

- express

- S'étend

- œil

- Trouvez

- Prénom

- Pour

- Fondation

- Fonderie

- De

- fonctions

- Bien

- Croissance

- ait eu

- Half

- Vous avez

- ici

- Haute

- HTML

- HTTPS

- IEEE

- amélioration

- in

- Améliore

- Interfaces

- interfaces

- développement

- IP

- iPad

- IT

- jpg

- Voie

- gros

- Nouveautés

- lancé

- niveaux

- bibliothèques

- Bibliothèque

- comme

- logique

- Style

- recherchez-

- mac

- macbook

- LES PLANTES

- marges

- largeur maximale

- Découvrez

- membre

- Souvenirs

- Mémoire

- la ficelle d'étiquettes/étiquettes volantes en carton

- émigrer

- m.

- Modules

- PLUS

- (en fait, presque toutes)

- must

- my

- réseau et

- Nouveauté

- nouvelles

- nœud

- maintenant

- of

- code

- offrant

- on

- ouvert

- fonctionner

- d'exploitation

- ande

- plus de

- propre

- Partenariat

- passé

- chemin

- PC

- /

- performant

- Téléphone

- PHP

- Platon

- Intelligence des données Platon

- PlatonDonnées

- Jouez

- Post

- power

- Pro

- processus

- protocole

- fournit

- plus rapidement

- vite.

- assez

- gamme

- Tarifs

- solutions

- exigent

- a besoin

- Resources

- Résultats

- Ressuscité

- Analyse

- en toute sécurité

- évolutive

- calendrier

- gratter

- sur le lien

- Services

- montré

- montrant

- Silicium

- depuis

- So

- caractéristiques

- vitesse

- vitesses

- Standard

- Normes

- j'ai commencé

- Commencez

- storage

- succès

- Appuyer

- Les soutiens

- surpassé

- Prenez

- équipe

- Technologie

- tester

- Essais

- à

- qui

- Le

- La Région

- leur

- puis

- Là.

- l'ont

- this

- à

- ensemble

- transférer

- trio

- TSMC

- Ultra

- a actualisé

- usb

- USB-C

- utilisé

- d'utiliser

- utilisateurs

- en utilisant

- validé

- via

- était

- Façon..

- WELL

- Quoi

- qui

- tout en

- why

- large

- Large gamme

- sera

- comprenant

- années

- Rendement

- you

- Votre

- zéphyrnet