Actualités : Fournisseurs

5 mai 2021

Axus Technology de Chandler, AZ, États-Unis - un fournisseur de solutions de polissage/planarisation chimico-mécanique (CMP), d'amincissement de tranche et de traitement de surface) - a travaillé pour développer et améliorer les performances du processus CMP et la capacité matérielle pour le carbure de silicium à une seule tranche (SiC) Applications CMP. L'objectif principal de ces efforts comprend : (1) la fiabilité de la manipulation des plaquettes minces/fragiles, (2) la planéité du substrat de qualité supérieure (variation d'épaisseur totale, ou TTV), (3) la qualité de la surface du substrat et (4) la réduction du coût de possession (CoO ).

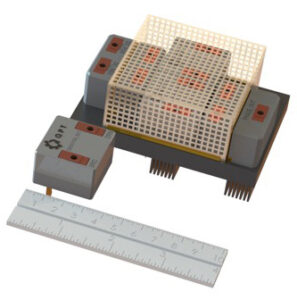

Basé sur l'architecture du système Capstone CMP, associé au support Crystal de la société spécialement conçu pour la manipulation de plaquettes fragiles et le contrôle de profil avancé, Axus a démontré des performances de processus qui ont jusqu'à présent atteint ou dépassé toutes les spécifications des clients.

Axus a manipulé et traité avec succès des substrats SiC de 150 mm de diamètre d'une épaisseur SEMI-standard de 350 µm à 175 µm, sans avoir besoin d'un collage temporaire ou de manipuler des tranches pour supporter ces substrats, comme le montre la Figure 1.

Figure 1. Le balayage du diamètre de la plaquette dans l'image du haut montre un substrat SiC de 150 mm avec une épaisseur moyenne de 171 µm avant CMP. Le balayage du diamètre de la plaquette dans l'image du bas montre la même plaquette avec une épaisseur moyenne de 170.4 µm post-CMP. Le TTV est réduit pendant le CMP.

Comme le montre également la figure 1, en plus de la capacité de manipulation de plaquettes fragiles, les supports Crystal offrent également la possibilité de contrôler avec précision le profil d'enlèvement de matière pendant le CMP, permettant aux clients de réduire le TTV pré-CMP et de produire un TTV submicronique de qualité supérieure. substrats. La demande du marché pour de tels substrats continuera de stimuler le haut de gamme des prix des tranches de SiC et les marges bénéficiaires des fournisseurs, déclare Axus.

Dans d'autres cas, Axus a démontré sa capacité à réduire la TTV du substrat de plusieurs microns lors du traitement CMP complet (face Si et face C) lors de démonstrations de processus client.

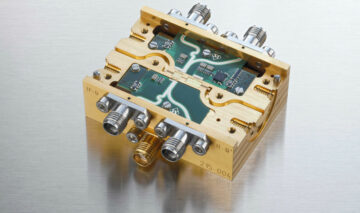

Pour l'optimisation de la qualité de surface, Axus travaille en étroite collaboration sur le développement des consommables CMP et l'optimisation des processus sur Capstone. Ces efforts ont permis de générer une finition de surface inférieure à Angström (Ra) avec un processus en une seule étape (voir la figure 2).

Figure 2. Image AFM sur la face Si après un polissage en une seule étape montrant une finition de surface de 0.8 Angstrom Ra.

Capstone est considéré comme le seul outil CMP avancé sur le marché qui prend en charge à la fois le traitement à une seule tranche et à deux tranches. Il a été démontré que le traitement à double plaquette réduit le CoO des consommables CMP jusqu'à 50 % par rapport aux processus d'enregistrement existants utilisés sur des outils CMP plus matures.

Étant donné que la réduction de SiC CMP CoO nécessite des taux d'élimination plus rapides et un débit de processus correspondant, les processus SiC CMP fonctionnent généralement à des pressions de tranche et des vitesses de rotation plus élevées - également appelées valeur PV (pression x vitesse) - par rapport à d'autres applications CMP plus matures telles que le silicium. La température du procédé devient un facteur limitant à mesure que la valeur PV augmente.

Axus a développé un système de refroidissement de processus propriétaire qui permet des processus CMP à valeur PV élevée qui augmentent considérablement le taux d'enlèvement de matière sans dépasser les limites de température maximales des autres composants du processus CMP, en particulier le tampon de polissage (voir Figure 3).

Figure 3. La différence de température de processus avec et sans la technologie de refroidissement de processus développée par Axus (basée sur la température de surface du tampon mesurée par pyromètre), à une pression de plaquette de 5 psi.

Le contrôle de la température du processus permet en outre un traitement à deux tranches pour gérer la température du processus dans les scénarios de processus à tranche unique et à deux tranches. Sur la base de l'architecture Capstone, les deux plateaux peuvent effectuer simultanément un traitement à deux tranches, ce qui entraîne un traitement parallèle de quatre tranches simultanément. Capstone est considéré comme le seul outil CMP avancé sur le marché capable de traiter autant de plaquettes en parallèle, améliorant encore son avantage en matière de débit.

Des améliorations récentes du procédé ont permis d'obtenir un taux d'enlèvement de matière supérieur à 10 µm par heure sur la face en silicium. En tant que percée pour le CMP en carbure de silicium à tranche unique, Axus fournit aux fournisseurs de tranches de SiC ce qui est considéré comme le système CMP le plus avancé du marché et des avantages de performances inégalés. Le système Capstone CMP, associé au support Crystal de la société (spécialement conçu pour la manipulation de tranches fragiles et le contrôle de profil avancé), fournit des substrats SiC de qualité supérieure avec un TTV inférieur au micron et une finition de surface inférieure à Angstrom. Le résultat net pour les utilisateurs de Capstone est un débit plus élevé tout en réduisant considérablement l'utilisation des consommables et le coût de possession (CoO).

Source : http://www.semiconductor-today.com/news_items/2021/may/axus-050521.shtml

- Avantage

- Tous

- Permettre

- applications

- architecture

- cas

- continuer

- roucouler

- Cristal

- Clients

- Demande

- développer

- Développement

- Visage

- Figure

- Focus

- plein

- Maniabilité

- Matériel

- Haute

- image

- Améliore

- Marché

- net

- Autre

- performant

- Premium

- la parfaite pression

- ajustements

- Profil

- Profit

- qualité

- Tarifs

- réduire

- Courir

- balayage

- So

- Solutions

- fournisseurs

- Support

- Les soutiens

- Surface

- combustion propre

- Technologie

- temporaire

- top

- États-Unis

- utilisateurs

- Plus-value

- Rapidité

- Qu’est ce qu'

- vos contrats