Kaksi viimeaikaista ohjelmistopohjaista algoritmitekniikkaa – autonominen ajo (ADAS/AD) ja generatiivinen tekoäly (GenAI) – pitävät puolijohdesuunnitteluyhteisön hereillä öisin.

Vaikka ADAS tasoilla 2 ja 3 ovat raiteilla, AD tasoilla 4 ja 5 ovat kaukana todellisuudesta, mikä aiheuttaa riskipääomainnostuksen ja -rahojen laskua. Nykyään GenAI saa huomion, ja riskipääomayritykset sijoittavat innokkaasti miljardeja dollareita.

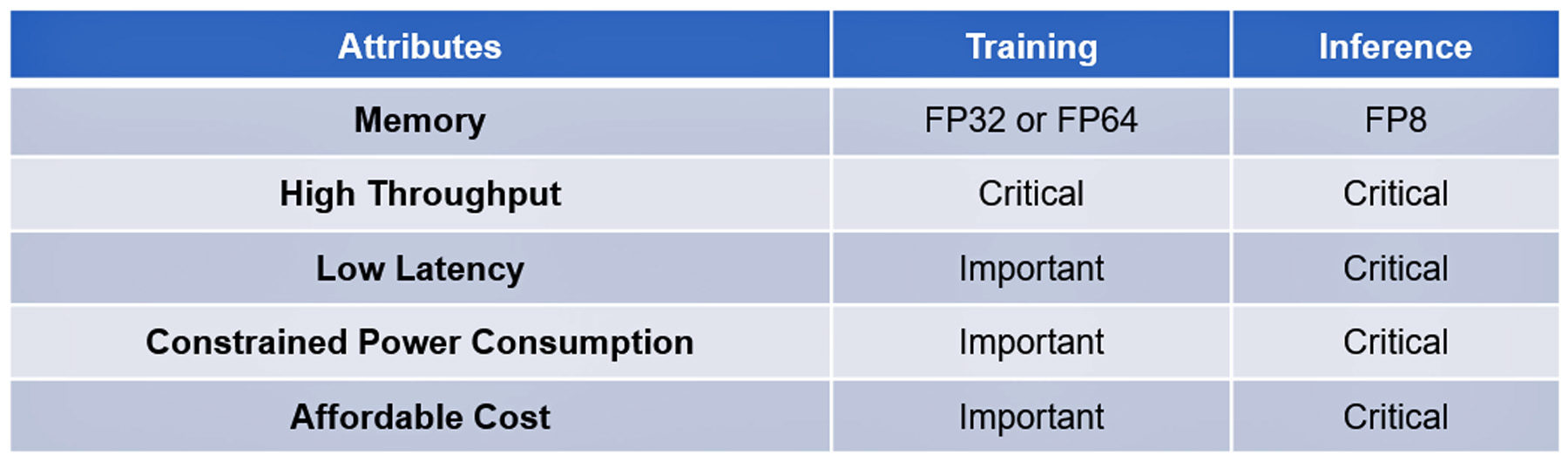

Molemmat tekniikat perustuvat nykyaikaisiin, monimutkaisiin algoritmeihin. Heidän koulutuksensa ja päätelmiensä käsittelyssä on muutamia yhteisiä ominaisuuksia, joista jotkut ovat kriittisiä, toiset tärkeitä, mutta eivät välttämättömiä: Katso taulukko I.

Näiden teknologioiden huomattavaa ohjelmistokehitystä ei ole toistaiseksi toistettu algoritmisten laitteistojen edistyksillä niiden suorittamisen nopeuttamiseksi. Esimerkiksi huippuluokan algoritmiset prosessorit eivät pysty vastaamaan ChatGPT-4-kyselyihin yhdessä tai kahdessa sekunnissa hintaan 2 ¢ kyselyä kohden, Google-haun määrittämä vertailukohta, tai käsitellä valtavia tietoja. AD-anturit keräävät alle 20 millisekunnissa.

Siihen asti, kunnes ranskalainen startup VSORA sijoitti aivovoimaa korjatakseen muistimuurina tunnetun muistin pullonkaulan.

Muistin seinä

CPU:n muistiseinän kuvasivat ensimmäisen kerran Wulf ja McKee vuonna 1994. Siitä lähtien muistin käyttö on muodostunut tietojenkäsittelyn suorituskyvyn pullonkaulaksi. Prosessorin suorituskyvyn edistyminen ei ole näkynyt muistin käytön edistymisessä, mikä saa prosessorit odottamaan yhä pidempään muistien toimittamaa dataa. Loppujen lopuksi prosessorin hyötysuhde putoaa alle 100 %.

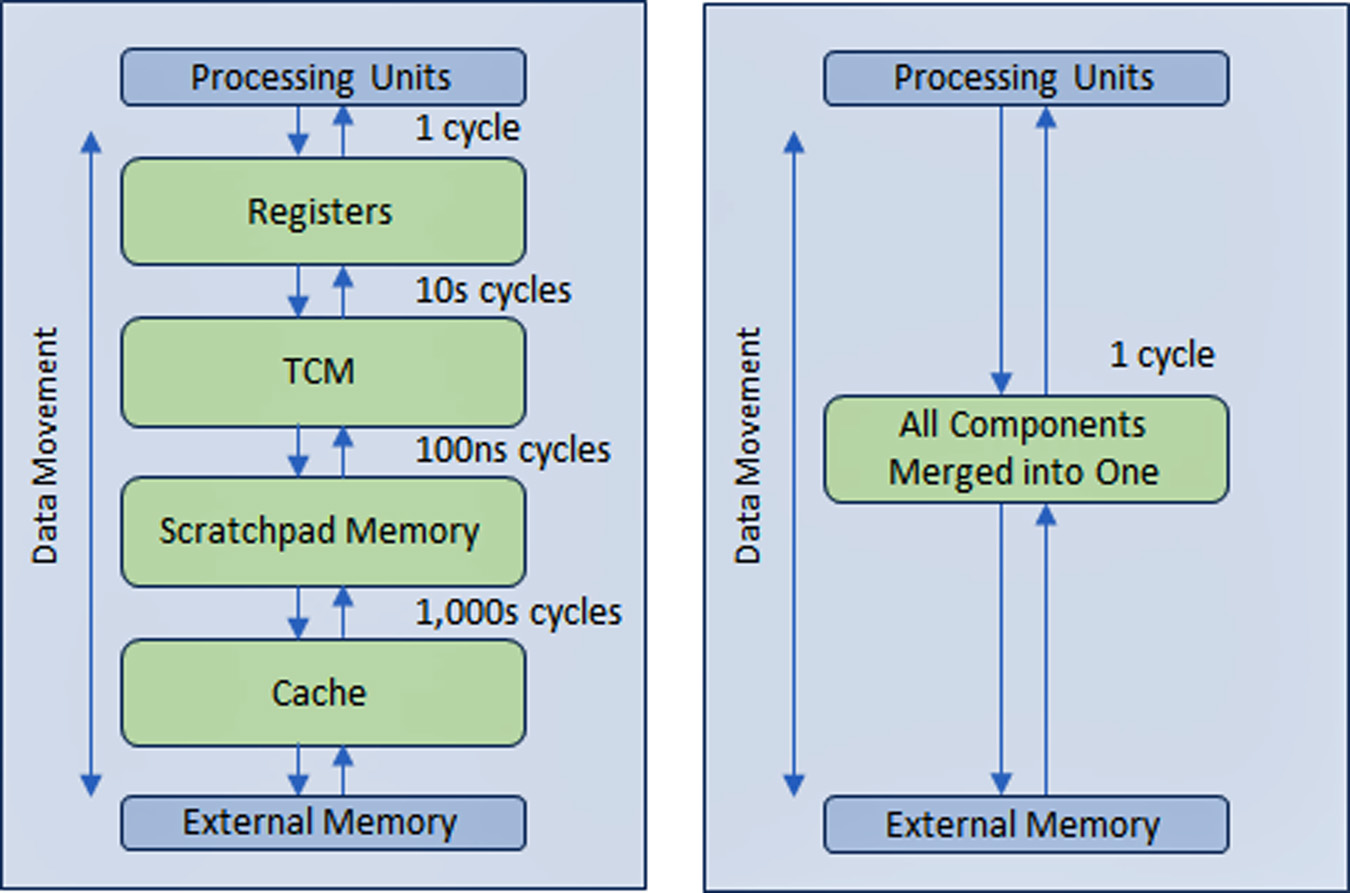

Ongelman ratkaisemiseksi puolijohdeteollisuus loi monitasoisen hierarkkisen muistirakenteen, jossa on useita välimuistitasoja lähempänä prosessoria, mikä vähentää liikenteen määrää hitaampien pää- ja ulkoisten muistien kanssa.

AD- ja GenAI-prosessorien suorituskyky riippuu enemmän kuin muun tyyppisten tietokonelaitteiden laajasta muistin kaistanleveydestä.

VSORA, joka perustettiin vuonna 2015 kohdistamaan 5G-sovelluksiin, keksi patentoidun arkkitehtuurin, joka kokoaa hierarkkisen muistirakenteen suureksi, laajakaistaiseksi, tiiviisti kytkettyksi muistiksi (TCM), jota käytetään yhdellä kellojaksolla.

Prosessoriytimien näkökulmasta TCM näyttää ja toimii kuin rekistereiden meri, jonka määrä on megatavua verrattuna todellisten fyysisten rekisterien kilotavuihin. Mahdollisuus käyttää mitä tahansa TMC:n muistisolua yhdellä jaksolla tuottaa suuren suoritusnopeuden, pienen viiveen ja alhaisen virrankulutuksen. Se vaatii myös vähemmän piialuetta. Uuden tiedon lataaminen ulkoisesta muistista TCM:ään nykyisten tietojen käsittelyn aikana ei vaikuta järjestelmän suorituskykyyn. Periaatteessa arkkitehtuuri mahdollistaa 80+% prosessointiyksiköiden käytön suunnittelunsa kautta. Silti on mahdollisuus lisätä välimuistia ja scratchpad-muistia, jos järjestelmän suunnittelija niin haluaa. Katso kuva 1.

Rekisterimäisen muistirakenteen ansiosta, joka on toteutettu käytännössä kaikissa muisteissa kaikissa sovelluksissa, VSORA-muistilähestymistavan etua ei voi yliarvioida. Tyypillisesti huippuluokan GenAI-prosessorit tarjoavat yksinumeroisen prosentuaalisen tehokkuuden. Esimerkiksi GenAI-prosessori, jonka nimellisteho on yksi Petaflopsin nimellissuorituskyky, mutta jonka hyötysuhde on alle 5 %, tuottaa käyttökelpoisen suorituskyvyn alle 50 teraflopsia. Sen sijaan VSORA-arkkitehtuurilla saavutetaan yli 10 kertaa suurempi tehokkuus.

VSORA:n algoritmiset kiihdytit

VSORA esitteli kaksi algoritmikiihdytinluokkaa – Tyr-perheen AD-sovelluksiin ja Jotunn-perhe GenAI-kiihdytykseen. Molemmat tarjoavat loistavan suorituskyvyn, minimaalisen latenssin ja alhaisen virrankulutuksen pienessä piijalanjäljessä.

Jopa kolmen petaflopsin nimellissuorituskyvyn ansiosta niiden tyypillinen toteutustehokkuus on 50-80 % algoritmityypistä riippumatta ja huippuvirrankulutus 30 wattia/petaflops. Nämä ovat huippuominaisuuksia, joita mikään kilpaileva tekoälykiihdytin ei ole vielä raportoinut.

Tyr ja Jotunn ovat täysin ohjelmoitavia ja integroivat AI- ja DSP-ominaisuudet, vaikkakin eri määrin, ja tukevat aritmeettisen valinnan lennossa 8-bittisestä 64-bittiseen joko kokonaisluku- tai liukulukupohjaiseen. Niiden ohjelmoitavuus mahdollistaa algoritmien universumin, mikä tekee niistä algoritmien agnostikkoja. Useita erilaisia harvoin tyyppejä tuetaan myös.

VSORA-prosessorien attribuutit ajavat ne kilpailevan algoritmisen prosessoinnin eturintamassa.

VSORA-tukiohjelmisto

VSORA suunnitteli ainutlaatuisen käännös-/validointialustan, joka on räätälöity sen laitteistoarkkitehtuuriin varmistaakseen, että sen monimutkaisilla ja tehokkailla SoC-laitteilla on runsaasti ohjelmistotukea.

Tarkoituksena on laittaa algoritminen suunnittelija ohjaamoon. Hierarkkiset varmennus-/validointitasot – ESL, hybridi, RTL ja portti – antavat painikepalautteen algoritmi-insinöörille vastauksena suunnittelun avaruustutkimuksiin. Tämä auttaa häntä valitsemaan parhaan kompromissin suorituskyvyn, latenssin, tehon ja alueen välillä. Korkealla abstraktiotasolla kirjoitettu ohjelmointikoodi voidaan kohdistaa eri käsittelyytimiin läpinäkyvästi käyttäjälle.

Ytimen välinen liitäntä voidaan toteuttaa saman piin sisällä, samalla piirilevyllä olevien sirujen välillä tai IP-yhteyden kautta. Synkronointi ytimien välillä hoidetaan automaattisesti käännöshetkellä, eikä se vaadi reaaliaikaisia ohjelmistotoimia.

Tiesulku L4/L5 autonomiseen ajamiseen ja generatiiviseen AI-päätelmään reunassa

Onnistunut ratkaisu sisältää myös ohjelmoitavuuden kentällä. Algoritmit kehittyvät nopeasti uusien ideoiden johdosta, jotka vanhenivat yhdessä yössä eilisen huipputason. Mahdollisuus päivittää algoritmi kentällä on huomattava etu.

Vaikka hyperscale-yritykset ovat koonneet valtavia laskentatiloja, joissa on lukuisia tehokkaimpia prosessoreita käsitelläkseen edistyneitä ohjelmistoalgoritmeja, lähestymistapa on käytännöllinen vain koulutuksessa, ei päätelmien tekemiseen reunalla.

Koulutus perustuu tyypillisesti 32-bittiseen tai 64-bittiseen liukulukuaritmetiikkaan, joka tuottaa suuria tietomääriä. Se ei vaadi tiukkaa latenssia ja sietää suurta virrankulutusta sekä huomattavia kustannuksia.

Reunojen päättely suoritetaan tyypillisesti 8-bittisellä liukulukuaritmetiikalla, joka tuottaa hieman vähemmän dataa, mutta vaatii tinkimätöntä latenssia, alhaista energiankulutusta ja alhaisia kustannuksia.

Energiankulutuksen vaikutus latenssiin ja tehokkuuteen

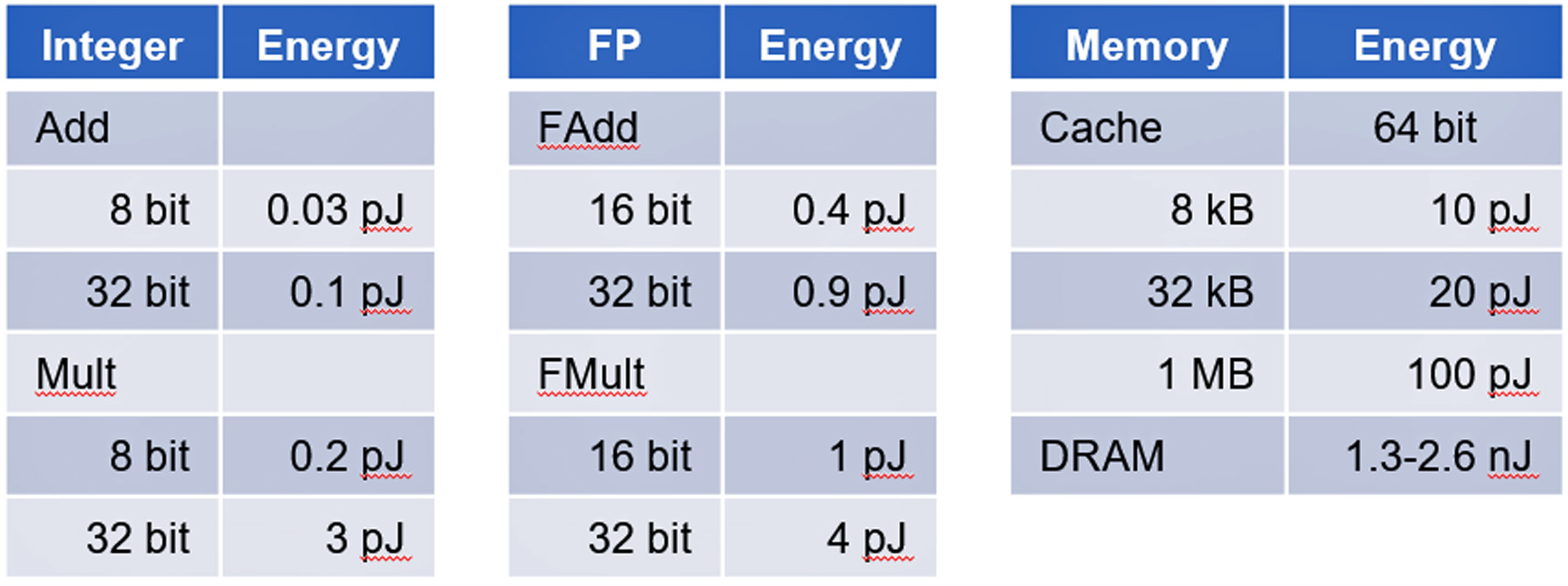

CMOS-piirilevyjen virrankulutusta hallitsee tiedonsiirto, ei tietojenkäsittely.

Professori Mark Horowitzin johtama Stanfordin yliopiston tutkimus osoitti, että muistin käytön virrankulutus kuluttaa suuruusluokkaa enemmän energiaa kuin digitaalisen logiikan peruslaskelmat. Katso taulukko II.

AD- ja GenAI-kiihdyttimet ovat parhaita esimerkkejä laitteista, joita hallitsee tiedonsiirto ja joka asettaa haasteen virrankulutuksen hillitsemiseen.

Yhteenveto

AD- ja GenAI-päätelmät asettavat ei-triviaaleja haasteita onnistuneiden toteutusten saavuttamiseksi. VSORA voi toimittaa kattavan laitteistoratkaisun ja tukiohjelmiston, joka täyttää kaikki kriittiset vaatimukset AD L4/L5:n ja GenAI:n kaltaisen GPT-4-kiihdytyksen käsittelemiseksi kaupallisesti kannattavin kustannuksin.

Lisätietoja VSORAsta ja sen Tyristä ja Jotunnista löytyy osoitteesta www.vsora.com.

Tietoja Lauro Rizzattista

Lauro Rizzatti on yritysneuvoja VSORA, innovatiivinen startup, joka tarjoaa pii-IP-ratkaisuja ja piisiruja, sekä tunnettu todentamiskonsultti ja laitteistoemuloinnin alan asiantuntija. Aiemmin hän työskenteli johdon, tuotemarkkinoinnin, teknisen markkinoinnin ja suunnittelun tehtävissä.

Lue myös:

Soitec suunnittelee puolijohdeteollisuuden tulevaisuutta

ISO 21434 Cybersecurity Aware SoC -kehitykseen

Ennakoiva huolto autojen toiminnallisen turvallisuuden kontekstissa

Jaa tämä viesti:

- SEO-pohjainen sisällön ja PR-jakelu. Vahvista jo tänään.

- PlatoData.Network Vertical Generatiivinen Ai. Vahvista itseäsi. Pääsy tästä.

- PlatoAiStream. Web3 Intelligence. Tietoa laajennettu. Pääsy tästä.

- PlatoESG. hiili, CleanTech, energia, ympäristö, Aurinko, Jätehuolto. Pääsy tästä.

- PlatonHealth. Biotekniikan ja kliinisten kokeiden älykkyys. Pääsy tästä.

- Lähde: https://semiwiki.com/automotive/336201-long-standing-roadblock-to-viable-l4-l5-autonomous-driving-and-generative-ai-inference-at-the-edge/

- :on

- :On

- :ei

- $ YLÖS

- 000

- 1

- 10

- 1800

- 1994

- 20

- 30

- 50

- 5G

- a

- kyky

- Meistä

- abstraktio

- kiihdyttää

- kiihtyvyys

- kiihdytin

- kiihdyttimiä

- pääsy

- Accessed

- Pääsy

- Saavuttaa

- päästään

- poikki

- säädökset

- todellinen

- Ad

- ADA:t

- lisätä

- osoite

- kehittynyt

- edistysaskeleet

- Etu

- neuvonantaja

- vaikuttaa

- AI

- algoritmi

- algoritmi

- algoritmit

- Kaikki

- mahdollistaa

- Myös

- määrä

- määrät

- an

- ja

- vastaus

- Kaikki

- sovellukset

- lähestymistapa

- arkkitehtuuri

- OVAT

- ALUE

- Art

- AS

- At

- huomio

- attribuutteja

- automaattisesti

- Automotive

- autonominen

- kaistanleveys

- perustua

- perustiedot

- Pohjimmiltaan

- BE

- tulevat

- ollut

- alle

- benchmark

- PARAS

- välillä

- miljardeja

- sekä

- liiketoiminta

- mutta

- by

- kätkö

- CAN

- ei voi

- kyvyt

- pääoma

- aiheuttaen

- solu

- haaste

- haasteet

- sirut

- luokat

- kello

- Ohjaamo

- koodi

- sortumisten

- kaupallisesti

- yhteisö

- Yritykset

- kilpailukykyinen

- monimutkainen

- monimutkainen

- kattava

- kompromissi

- laskelmat

- Laskea

- tietojenkäsittely

- liitäntä

- konsultti

- kulutus

- sisältää

- tausta

- Hinta

- kustannukset

- kytketty

- prosessori

- luotu

- kriittinen

- Nykyinen

- leikkaamisreuna

- sykli

- tiedot

- tietojenkäsittely

- toimittaa

- toimitettu

- Antaa

- tiheä

- riippuu

- on kuvattu

- Malli

- suunniteltu

- Suunnittelija

- yksityiskohdat

- Laitteet

- eri

- digitaalinen

- numeroa

- do

- ei

- dollaria

- ajanut

- ajo

- Pudota

- Drops

- innokkaasti

- reuna

- tehokkuus

- myöskään

- loppu

- energia

- Energian kulutus

- insinööri

- Tekniikka

- varmistaa

- innostus

- ESL

- olennainen

- vakiintunut

- EVER

- kehittää

- esimerkki

- Esimerkit

- teloitus

- asiantuntija

- ulkoinen

- perhe

- paljon

- maatilat

- palaute

- harvat

- ala

- Kuva

- Etunimi

- kelluva

- Jalanjälki

- varten

- eturintamassa

- löytyi

- Perustettu

- Ranskan

- alkaen

- täysin

- toiminnallinen

- tulevaisuutta

- synnyttää

- generatiivinen

- Generatiivinen AI

- Google Search

- suurempi

- kahva

- Palvelimet

- Olla

- he

- sankari

- auttaa

- hänen

- Korkea

- korkea suorituskyky

- suurin

- häntä

- Horowitz

- http

- HTTPS

- valtava

- Hybridi

- i

- ICS

- ideoita

- if

- ii

- täytäntöönpano

- toteutukset

- täytäntöön

- tärkeä

- määrätä

- in

- sisältää

- teollisuus

- Alan asiantuntija

- innovatiivinen

- esimerkki

- sen sijaan

- yhdistää

- tulee

- käyttöön

- keksi

- Investoida

- investoineet

- IP

- IT

- SEN

- jpg

- hyppyjä

- pito

- tunnettu

- Landschaft

- suuri

- Viive

- Led

- vähemmän

- Taso

- tasot

- pitää

- lastaus

- logiikka

- pitkäaikainen

- kauemmin

- ulkonäkö

- Matala

- tärkein

- huolto

- Tekeminen

- onnistui

- johto

- toimeksiantoja

- Merkitse

- Marketing

- massiivinen

- max-width

- Tavata

- Muistoja

- Muisti

- millisekuntia

- minimi

- Moderni

- raha

- lisää

- liike

- moninkertainen

- monien joukossa

- Uusi

- yön

- huomattava

- huomionarvoinen

- nyt

- vanhentunut

- of

- tarjoamalla

- on

- ONE

- vain

- Operations

- or

- tilata

- määräys

- Muut

- Muuta

- yli

- yön aikana

- liioitella

- patentoitu

- Peak

- varten

- osuus

- suorituskyky

- suoritettu

- näkökulma

- fyysinen

- foorumi

- Platon

- Platonin tietotieto

- PlatonData

- paljon

- Kohta

- kantoja

- mahdollisuus

- Kirje

- teho

- Käytännön

- aiemmin

- tärkein

- Ongelma

- prosessi

- jalostettu

- käsittely

- Suoritin

- prosessorit

- Tuotteet

- Opettaja

- ohjelmoitava

- Ohjelmointi

- Edistyminen

- kuljettaa

- laittaa

- kyselyt

- alue

- nopeasti

- Lue

- reaaliaikainen

- Todellisuus

- äskettäinen

- vähentää

- riippumatta

- rekisterit

- huomattava

- monistaa

- raportoitu

- edellyttää

- vaatimukset

- Vaatii

- vastaus

- sama

- SEA

- Haku

- sekuntia

- nähdä

- valinta

- puolijohde

- anturit

- useat

- Jaa:

- osakkeet

- shouldnt

- osoittivat

- Pii

- koska

- single

- pieni

- So

- Tuotteemme

- ratkaisu

- Ratkaisumme

- SOLVE

- jonkin verran

- jokseenkin

- lähde

- Tila

- nopeus

- käytetty

- Stanford

- Stanfordin yliopisto

- käynnistyksen

- Osavaltio

- huippu-

- Tähtien

- Yhä

- virtaviivainen

- tiukka

- rakenne

- tutkimus

- merkittävä

- onnistunut

- tuki

- Tuetut

- Tukea

- tahdistus

- järjestelmä

- taulukko

- Räätälöity

- Kohde

- kohdistaminen

- Tekninen

- Technologies

- kuin

- että

- -

- Tulevaisuus

- heidän

- Niitä

- Siellä.

- Nämä

- ne

- tätä

- kolmella

- Kautta

- suoritusteho

- tiukasti

- aika

- kertaa

- että

- tänään

- raita

- perinteinen

- liikenne

- koulutus

- avoimesti

- kaksi

- tyyppi

- tyypit

- tyypillinen

- tyypillisesti

- unique

- yksiköt

- CasinoUniverse

- yliopisto

- asti

- parantaa

- käyttökelpoinen

- käyttäjä

- käyttämällä

- pääomasijoittajat

- hanke

- riskipääomaa

- Vahvistus

- Vastaan

- kautta

- kannattava

- käytännössä

- volyymit

- odottaa

- Seinä

- oli

- Tapa..

- HYVIN

- kun

- vaikka

- leveä

- toiveet

- with

- sisällä

- kirjallinen

- vielä

- saannot

- zephyrnet