Asiantuntijat pöydässä: Semiconductor Engineering istuutui keskustelemaan muistin kehityksestä yhä heterogeenisemmissa järjestelmissä, ja Frank Ferro, ryhmäjohtaja, tuotehallinta kadenssi; Steven Woo, toinen ja arvostettu keksijä Rambus; Jongsin Yun, muistitekniikan asiantuntija klo Siemens EDA; Randy White, muistiratkaisujen ohjelmapäällikkö osoitteessa Näkönäyttö; ja Frank Schirrmeister, varatoimitusjohtaja, ratkaisut ja liiketoiminnan kehitys Arteris. Seuraavassa on otteita tästä keskustelusta. Tämän keskustelun ensimmäinen osa löytyy tätä.

![[L-R]: Frank Ferro, Cadence; Steven Woo, Rambus; Jongsin Yun, Siemens EDA; Randy White, Keysight; ja Frank Schirrmeister, Arteris.](https://platoaistream.com/wp-content/uploads/2024/01/rethinking-memory.png)

[L-R]: Frank Ferro, Cadence; Steven Woo, Rambus; Jongsin Yun, Siemens EDA; Randy White, Keysight; ja Frank Schirrmeister, Arteris

SE: Kun kamppailemme AI/ML:n ja tehotarpeiden kanssa, mitä kokoonpanoja on harkittava uudelleen? Näemmekö siirtymisen pois Von Neumann -arkkitehtuurista?

Vau: Järjestelmäarkkitehtuurien osalta alalla on meneillään kahtiajako. Perinteiset sovellukset, jotka ovat hallitsevia työhevosia, joita käytämme pilvessä x86-pohjaisilla palvelimilla, eivät katoa. On olemassa vuosikymmeniä ohjelmistoja, joita on rakennettu ja kehitetty ja jotka perustuvat siihen, että tämä arkkitehtuuri toimii hyvin. Sitä vastoin AI/ML on uusi luokka. Ihmiset ovat miettineet arkkitehtuurit uudelleen ja rakentaneet hyvin toimialuekohtaisia prosessoreita. Näemme, että noin kaksi kolmasosaa energiasta kuluu vain tiedon siirtämiseen prosessorin ja HBM-laitteen välillä, kun taas vain noin kolmasosa käytetään DRAM-ytimien bittien todelliseen käyttöön. Tiedonsiirto on nyt paljon haastavampaa ja kalliimpaa. Emme aio luopua muistista. Tarvitsemme sitä, koska tietojoukot kasvavat. Joten kysymys kuuluu: "Mikä on oikea tapa edetä?" Pinoamisesta on keskusteltu paljon. Jos ottaisimme sen muistin ja laittaisimme sen suoraan prosessorin päälle, se tekee kaksi asiaa puolestasi. Ensinnäkin kaistanleveyttä rajoittaa nykyään rantaviiva tai sirun kehä. Sinne I/O:t menevät. Mutta jos pinoat sen suoraan prosessorin päälle, voit nyt hyödyntää sirun koko alueen hajautettuihin yhteyksiin ja saada enemmän kaistanleveyttä itse muistiin ja se voi syöttää suoraan alas prosessori. Linkit lyhenevät paljon ja tehokkuus nousee luultavasti 5x 6x. Toiseksi, kaistanleveyden määrä, jonka voit saada, koska enemmän aluetaulukkoa voidaan yhdistää muistiin, kasvaa myös usean kokonaislukukertoimen verran. Näiden kahden asian tekeminen yhdessä voi tarjota enemmän kaistanleveyttä ja tehdä siitä tehokkaamman. Teollisuus kehittyy tarpeiden mukaan, ja se on ehdottomasti yksi tapa, jolla näemme muistijärjestelmien alkavan kehittyä tulevaisuudessa tehostamaan tehokkuutta ja tarjoamaan enemmän kaistanleveyttä.

Rauta: Kun aloin työskennellä HBM:n parissa noin vuonna 2016, jotkut edistyneemmistä asiakkaista kysyivät, voidaanko sitä pinota. He ovat etsineet DRAM-muistin pinoamista jo jonkin aikaa, koska sillä on selviä etuja. Fyysisestä kerroksesta PHY muuttuu periaatteessa merkityksettömäksi, mikä säästää paljon tehoa ja tehokkuutta. Mutta nyt sinulla on usean 100 watin prosessori, jonka päällä on muisti. Muisti ei kestä lämpöä. Se on luultavasti lämpöketjun heikoin lenkki, mikä luo uuden haasteen. Hyötyjä on, mutta heidän on silti keksittävä, kuinka käsitellä lämpöä. Nyt on enemmän kannustimia viedä tämäntyyppistä arkkitehtuuria eteenpäin, koska se todella säästää kokonaisuutena suorituskyvyn ja tehon suhteen ja parantaa laskentatehoa. Mutta on joitain fyysisiä suunnitteluhaasteita, jotka on käsiteltävä. Kuten Steve sanoi, näemme kaikenlaisia arkkitehtuureja, jotka ovat tulossa ulos. Olen täysin samaa mieltä siitä, että GPU/CPU-arkkitehtuurit eivät ole menossa minnekään, ne ovat edelleen hallitsevia. Samaan aikaan jokainen planeetan yritys yrittää keksiä parempaa hiirenloukkua tekoälynsä tekemiseen. Näemme sirussa olevan SRAM-muistin ja suuren kaistanleveyden muistin yhdistelmiä. LPDDR on nostanut päätään melkoisesti näinä päivinä sen suhteen, kuinka hyödyntää LPDDR:ää datakeskuksessa tehon takia. Olemme jopa nähneet, että GDDR:ää käytetään joissakin tekoälyn päättelysovelluksissa sekä kaikissa vanhoissa muistijärjestelmissä. He yrittävät nyt puristaa mahdollisimman monta DDR5:tä jalanjäljelle. Olen nähnyt jokaisen mieleesi tulevan arkkitehtuurin, olipa kyseessä DDR, HBM, GDDR tai jokin muu. Se riippuu prosessoriytimestäsi sen suhteen, mikä on kokonaisarvosi, ja kuinka voit murtautua tietyn arkkitehtuurin läpi. Muistijärjestelmä, joka toimii sen mukana, joten voit muokata suorittimesi ja muistiarkkitehtuurisi sen mukaan, mitä on saatavilla.

Ja a: Toinen ongelma on volatiliteetti. Jos tekoäly joutuu käsittelemään esimerkiksi IoT-pohjaisen tekoälyn suorittamisen välistä tehoväliä, tarvitsemme paljon virtaa pois ja päälle, ja kaiken tämän AI-koulutuksen tiedon täytyy pyöriä uudestaan ja uudestaan. Jos meillä on jonkinlaisia ratkaisuja, joissa voimme tallentaa nuo painot sirulle, jotta meidän ei tarvitse aina liikkua edestakaisin saman painon takia, se säästää paljon virtaa, etenkin IoT-pohjaisessa tekoälyssä. On olemassa toinen ratkaisu näiden tehotarpeiden auttamiseksi.

Schirrmeister: Minusta on kiehtovaa NoC:n näkökulmasta se, missä sinun on optimoitava nämä polut prosessorista, joka kulkee NoC:n läpi, päästään muistiliitäntään ohjaimen kanssa, joka mahdollisesti kulkee UCIe:n kautta siirtääkseen siru toiseen siruun, jossa on sitten muistia. se. Kyse ei ole siitä, että Von Neumann -arkkitehtuurit olisivat kuolleita. Mutta nyt on niin monia muunnelmia riippuen siitä, minkä työmäärän haluat laskea. Niitä on tarkasteltava muistin yhteydessä, ja muisti on vain yksi näkökohta. Mistä saat datan datapaikalta, miten se on järjestetty tässä DRAMissa? Käymme läpi kaikkia näitä asioita, kuten muistien suorituskyvyn analysointia ja sitten sen järjestelmäarkkitehtuurin optimointia. Se kannustaa paljon innovaatioita uusille arkkitehtuureille, joita en koskaan ajatellut, kun opiskelin yliopistossa Von Neumannista. Äärimmäisessä toisessa päässä sinulla on esimerkiksi verkkoja. Arkkitehtuurien välissä on nyt paljon enemmän harkittavaa, ja sitä ohjaavat muistin kaistanleveys, laskentaominaisuudet ja niin edelleen, eivätkä ne kasva samalla nopeudella.

Valkoinen: Suuntaus koskee hajautettua tai hajautettua laskentaa, mikä tarkoittaa, että arkkitehdilla on oltava enemmän työkaluja käytettävissään. Muistihierarkia on laajentunut. Mukana on semantiikkaa sekä CXL- ja erilaisia hybridimuisteja, jotka ovat saatavilla flashille ja DRAM-muistille. Palvelinkeskuksen rinnakkainen sovellus on autoteollisuus. Autoteollisuudessa tämä anturi oli aina laskettu ECU:illa (elektronisilla ohjausyksiköillä). Olen kiinnostunut siitä, miten se on kehittynyt datakeskukseksi. Nopeasti eteenpäin, ja tänään meillä on hajautettuja laskentasolmuja, joita kutsutaan toimialueen ohjauskoneiksi. Se on sama asia. Se yrittää käsitellä sitä, että ehkä teho ei ole niin suuri asia, koska tietokoneiden koko ei ole niin suuri, mutta latenssi on varmasti iso asia autoteollisuudessa. ADAS tarvitsee erittäin suuren kaistanleveyden, ja sinulla on erilaisia kompromisseja. Ja sitten sinulla on enemmän mekaanisia antureita, mutta samanlaisia rajoituksia datakeskuksessa. Sinulla on kylmävarasto, jonka ei tarvitse olla pieni latenssi, ja sitten sinulla on muita suuren kaistanleveyden sovelluksia. On kiehtovaa nähdä, kuinka paljon arkkitehdin työkalut ja vaihtoehdot ovat kehittyneet. Toimiala on tehnyt todella hyvää työtä vastatakseen, ja me kaikki tarjoamme erilaisia ratkaisuja, jotka syöttävät markkinoille.

SE: Miten muistin suunnittelutyökalut ovat kehittyneet?

Schirrmeister: Kun aloitin parilla ensimmäisellä sirullani 90-luvulla, eniten käytetty järjestelmätyökalu oli Excel. Siitä lähtien olen aina toivonut, että se voisi rikkoutua jossain vaiheessa järjestelmätasolla tekemiemme asioiden, muistin, kaistanleveyden analyysin ja niin edelleen vuoksi. Tämä vaikutti joukkueisiini melkoisesti. Tuolloin se oli erittäin edistyksellistä tavaraa. Mutta Randyn mukaan tiettyjä monimutkaisia asioita on nyt simuloitava sellaisella tarkkuudella, mikä ei aiemmin ollut mahdollista ilman laskentaa. Esimerkiksi DRAM-käytön tietyn latenssin olettaminen voi johtaa huonoihin arkkitehtuuripäätöksiin ja mahdollisesti virheelliseen tiedonsiirtoarkkitehtuurien suunnitteluun sirulle. Kääntöpuoli on myös totta. Jos oletat aina pahimman tapauksen, suunnittelet arkkitehtuurin yli. Kun työkalut suorittavat DRAM- ja suorituskyvyn analyysin ja kun ohjaimille on saatavilla oikeat mallit, arkkitehti voi simuloida kaiken. Tämä on kiehtova ympäristö. järjestelmätason työkalu saattaa todellakin toteutua, koska tiettyjä dynaamisia vaikutuksia et voi enää tehdä Excelissä, koska sinun on simuloitava ne pois – varsinkin kun käytät PHY-ominaisuuksia sisältävää die-to-die-käyttöliittymää ja linkität sitten ominaisuudet, kuten kaikki tarkistaminen, oliko kaikki oikein, ja mahdollisesti tietojen uudelleenlähetys. Jos simulaatioita ei tehdä, arkkitehtuuri ei ole optimaalinen.

Rauta: Ensimmäinen askel useimmissa arvioinneissamme on antaa heille muistitesti, jotta he voivat alkaa tarkastella DRAM-tehokkuutta. Se on valtava askel, vaikka teet niinkin yksinkertaisia asioita kuin paikallisten työkalujen suorittaminen DRAM-simulaatioiden tekemiseen, mutta sitten siirrytään täysimittaisiin simulaatioihin. Näemme enemmän asiakkaita, jotka pyytävät tällaista simulaatiota. Sen varmistaminen, että DRAM-tehokkuus on kasvanut 90-luvun huipulla, on erittäin tärkeä ensimmäinen askel kaikissa arvioinneissa.

Vau: Osa siitä, miksi näet täyden järjestelmän simulointityökalujen nousun, on se, että DRAM-muistit ovat muuttuneet paljon monimutkaisemmiksi. On erittäin vaikeaa olla nyt tasalla joissakin monimutkaisissa työkuormissa käyttämällä yksinkertaisia työkaluja, kuten Excel. Jos katsot 90-luvun DRAM-tietolehteä, ne olivat noin 40 sivua. Nyt niitä on satoja sivuja. Se kertoo vain laitteen monimutkaisuudesta suurten kaistanleveyksien poistamiseksi. Yhdistät tämän siihen tosiasiaan, että muisti on tällainen järjestelmän kustannuksissa sekä prosessorin suorituskykyyn liittyvä kaistanleveys ja latenssi. Se on myös suuri voimankuljettaja, joten sinun on nyt simuloitava paljon yksityiskohtaisemmalla tasolla. Työkaluvirran osalta järjestelmäarkkitehdit ymmärtävät, että muisti on valtava kuljettaja. Joten työkalujen on oltava kehittyneempiä ja niiden on liityttävä muihin työkaluihin erittäin hyvin, jotta järjestelmäarkkitehti saa parhaan globaalin kuvan siitä, mitä tapahtuu – erityisesti muistin vaikutuksista järjestelmään.

Ja a: Kun siirrymme tekoälyn aikakauteen, käytetään paljon moniytimiä järjestelmiä, mutta emme tiedä, mikä data menee minne. Se menee myös enemmän rinnakkain sirun kanssa. Muistin koko on paljon suurempi. Jos käytämme ChatGPT-tyyppistä tekoälyä, niin mallien tiedonkäsittely vaatii noin 350 Mt dataa, mikä on valtava määrä dataa pelkällä painolla ja varsinainen syöttö/tulostus on paljon suurempi. Vaaditun tiedon määrän kasvu tarkoittaa, että meillä on paljon todennäköisyysvaikutuksia, joita emme ole ennen nähneet. Se on erittäin haastava testi nähdä kaikki tähän suureen muistimäärään liittyvät virheet. Ja ECC:tä käytetään kaikkialla, jopa SRAMissa, joka ei perinteisesti käyttänyt ECC:tä, mutta nyt se on hyvin yleistä suurimmissa järjestelmissä. Kaiken tämän testaus on erittäin haastavaa, ja sitä on tuettava EDA-ratkaisuilla kaikkien näiden erilaisten olosuhteiden testaamiseksi.

SE: Mitä haasteita suunnittelutiimit kohtaavat päivittäin?

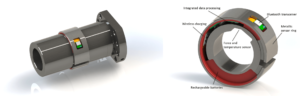

Valkoinen: Löydät minut laboratoriosta minä tahansa päivänä. Käärin hihat ja minulla on kädet likaiset, johtojen tökkiminen, juottaminen ja mitä muuta. Ajattelen paljon piin jälkeistä validointia. Puhuimme varhaisesta simulaatiosta ja die-työkaluista – BiST:stä ja sellaisista asioista. Loppujen lopuksi, ennen kuin lähetämme, haluamme tehdä jonkinlaisen järjestelmän validoinnin tai laitetason testejä. Puhuimme siitä, kuinka voit voittaa muistimuurin. Etsimme muistia, HBM:ää, sellaisia asioita. Jos tarkastelemme pakkausteknologian kehitystä, aloitimme lyijypakkauksista. Ne eivät olleet kovin hyviä signaalin eheydelle. Vuosikymmeniä myöhemmin siirryimme optimoituun signaalin eheyteen, kuten palloruudukkomatriisiin (BGA). Emme voineet käyttää sitä, mikä tarkoitti, että et voinut testata sitä. Joten keksimme tämän konseptin, jota kutsutaan laitevälittimeksi - BGA-interposeriksi - ja sen ansiosta pystyimme yhdistämään erityisen kiinnikkeen, joka reititti signaalit ulos. Sitten voisimme kytkeä sen testilaitteistoon. Nopeasti eteenpäin tähän päivään, ja nyt meillä on HBM ja sirut. Kuinka kiinnitän valaisimeni piivälityslaitteen väliin? Emme voi, ja se on taistelu. Se on haaste, joka pitää minut hereillä öisin. Kuinka teemme vikaanalyysejä kentällä OEM- tai järjestelmäasiakkaan kanssa, kun he eivät saa 90 %:n tehokkuutta. Linkissä on enemmän virheitä, niitä ei voi alustaa kunnolla, eikä koulutus toimi. Onko se järjestelmän eheysongelma?

Schirrmeister: Etkö tekisi tämän mieluummin kotoa käsin virtuaalisen käyttöliittymän avulla kuin kävelemään laboratorioon? Eikö vastaus ole enemmän analytiikkaa, jonka rakennat sirulle? Sirujen avulla integroimme kaiken entisestään. Juotosraudan saaminen sinne ei ole varsinainen vaihtoehto, joten sirulla on oltava analytiikka. Meillä on sama ongelma NoC:n kanssa. Ihmiset katsovat NoC:tä ja lähetät tiedot, ja sitten se on poissa. Tarvitsemme analytiikkaa, jotta ihmiset voivat tehdä virheenkorjauksia, ja se ulottuu valmistustasolle, jotta voit vihdoin työskennellä kotoa ja tehdä kaiken siruanalytiikan perusteella.

Rauta: Etenkin suuren kaistanleveyden muistilla et pääse fyysisesti sisään sinne. Kun lisensoimme PHY:n, meillä on myös tuote, joka sopii siihen, joten voit kiinnittää huomiota jokaiseen näistä 1,024 3 bitistä. Voit aloittaa DRAM-muistin lukemisen ja kirjoittamisen työkalusta, joten sinun ei tarvitse fyysisesti päästä sisään. Pidän interposer ideasta. Tuomme joitakin tappeja ulos välikappaleesta testauksen aikana, mitä et voi tehdä järjestelmässä. On todella haastavaa päästä näihin 2.5D-järjestelmiin. Jopa suunnittelutyökalujen kulun näkökulmasta näyttää siltä, että useimmat yritykset tekevät oman yksittäisen kulkunsa monille näille 2.5D-työkaluille. Olemme alkamassa koonnut standardoidumpaa tapaa rakentaa XNUMXD-järjestelmä signaalin eheydestä, tehosta ja koko virtauksesta.

Valkoinen: Kun asiat etenevät, toivon, että voimme silti säilyttää saman tarkkuustason. Olen UCIe-muototekijöiden noudattamisryhmässä. Tarkastelen, kuinka luonnehtia tunnettua hyvää kuoppaa, kultaista kuoppaa. Lopulta tämä vie paljon enemmän aikaa, mutta löydämme onnellisen tavan tarvitsemamme testauksen suorituskyvyn ja tarkkuuden sekä sisäänrakennetun joustavuuden välillä.

Schirrmeister: Jos tarkastelen siruja ja niiden käyttöönottoa avoimemmassa tuotantoympäristössä, niin testaus on yksi isoimmista haasteista sen saamisessa toimimaan. Jos olen iso yritys ja hallitsen sen kaikkia puolia, voin rajoittaa asioita asianmukaisesti, jotta testaus ja niin edelleen on mahdollista. Jos haluan noudattaa UCIe:n iskulausetta, jonka mukaan UCI on vain yhden kirjaimen päässä PCI:stä, ja kuvittelen tulevaisuuden, jossa UCIe-kokoonpanosta tulee valmistuksen näkökulmasta kuin PCI-paikat PC:ssä nykyään, niin sen testausnäkökohdat ovat todellakin. haastava. Meidän on löydettävä ratkaisu. Töitä on paljon.

Aiheeseen liittyvät artikkelit

Muistin tulevaisuus (Yllä olevan pyöritettävän osa 1)

Lämpö- ja tehoongelmien ratkaisemisesta CXL:n ja UCIe:n rooleihin tulevaisuus tarjoaa lukuisia muistimahdollisuuksia.

- SEO-pohjainen sisällön ja PR-jakelu. Vahvista jo tänään.

- PlatoData.Network Vertical Generatiivinen Ai. Vahvista itseäsi. Pääsy tästä.

- PlatoAiStream. Web3 Intelligence. Tietoa laajennettu. Pääsy tästä.

- PlatoESG. hiili, CleanTech, energia, ympäristö, Aurinko, Jätehuolto. Pääsy tästä.

- PlatonHealth. Biotekniikan ja kliinisten kokeiden älykkyys. Pääsy tästä.

- Lähde: https://semiengineering.com/rethinking-memory/

- :on

- :On

- :ei

- :missä

- $ YLÖS

- 1

- 2016

- 3d

- 40

- a

- Meistä

- edellä

- pääsy

- Pääsy

- tarkkuus

- todellinen

- todella

- ADA:t

- lisätä

- osoite

- Hyväksyminen

- kehittynyt

- Etu

- etuja

- uudelleen

- AI

- AI-koulutus

- AI / ML

- Kaikki

- sallittu

- mahdollistaa

- Myös

- aina

- määrä

- an

- analyysi

- Analytics

- ja

- Toinen

- vastaus

- Kaikki

- enää

- kaikkialla

- Hakemus

- sovellukset

- asianmukaisesti

- arkkitehdit

- arkkitehtuuri

- OVAT

- ALUE

- noin

- järjestetty

- Ryhmä

- AS

- pyytäminen

- ulkomuoto

- näkökohdat

- Kokoonpano

- olettaa

- At

- yrityksiä

- Automotive

- saatavissa

- pois

- takaisin

- Huono

- pallo

- kaistanleveys

- baari

- perustua

- Pohjimmiltaan

- perusta

- BE

- koska

- tulevat

- tulee

- ollut

- ennen

- ovat

- Hyödyt

- PARAS

- Paremmin

- välillä

- Iso

- suurempi

- Bitti

- Tauko

- tuoda

- rakentaa

- rakennettu

- liiketoiminta

- liiketoiminnan kehitys

- mutta

- by

- kadenssi

- nimeltään

- tuli

- CAN

- Voi saada

- kyvyt

- tapaus

- keskus

- tietty

- varmasti

- ketju

- haaste

- haasteet

- haastava

- ominaisuudet

- kuvata

- tarkkailun

- siru

- sirut

- luokka

- selkeä

- pilvi

- kylmä

- Kylmävarasto

- yhdistelmät

- Tulla

- tuleva

- Yhteinen

- Yritykset

- yritys

- monimutkainen

- monimutkaisuus

- noudattaminen

- monimutkainen

- Laskea

- tietokoneet

- tietojenkäsittely

- käsite

- olosuhteet

- kytkeä

- harkittu

- rajoitteet

- tausta

- kontrasti

- ohjaus

- ohjain

- Keskustelu

- Ydin

- korjata

- Hinta

- voisi

- Pari

- prosessori

- luo

- asiakas

- Asiakkaat

- tiedot

- Data Center

- aineistot

- päivä

- päivästä päivään

- päivää

- kuollut

- sopimus

- vuosikymmeninä

- päätökset

- ehdottomasti

- vaatii

- Riippuen

- riippuu

- Malli

- suunnittelu

- yksityiskohtainen

- Kehitys

- laite

- Kuolla

- eri

- vaikea

- suoraan

- Johtaja

- keskustelu

- hävittäminen

- hienostunut

- jaettu

- hajautettu laskenta

- do

- ei

- ei

- tekee

- verkkotunnuksen

- hallitseva

- tehty

- Dont

- alas

- ajanut

- kuljettaja

- aikana

- dynaaminen

- Varhainen

- vaikutukset

- tehokkuus

- tehokas

- Elektroninen

- loppu

- energia

- Tekniikka

- Koko

- ympäristö

- laitteet

- Aikakausi

- virheet

- erityisesti

- Eetteri (ETH)

- arviointi

- arvioinnit

- Jopa

- lopulta

- Joka

- kaikki

- kaikkialla

- evoluutio

- kehittää

- kehittynyt

- kehittyy

- esimerkki

- kunnostautua

- laajeni

- kallis

- ulottuu

- äärimmäinen

- erittäin

- katse

- Kasvot

- tosiasia

- tekijä

- Epäonnistuminen

- lumoava

- FAST

- mahdollinen

- kaveri

- tarkkuus

- ala

- Kuva

- Vihdoin

- Löytää

- Etunimi

- salama

- Joustavuus

- Kääntää

- virtaus

- seuraa

- Jalanjälki

- varten

- muoto

- eteenpäin

- Eteenpäin

- löytyi

- vilpitön

- alkaen

- koko

- edelleen

- tulevaisuutta

- saada

- saada

- Antaa

- tietty

- Global

- Go

- Goes

- menee

- Kultainen

- poissa

- hyvä

- hyvä työ

- sai

- ruudukko

- Ryhmä

- Kasvava

- HAD

- Käsittely

- käsissä

- onnellinen

- Olla

- ottaa

- pää

- auttaa

- hierarkia

- Korkea

- pitää

- Etusivu

- toivoa

- Miten

- Miten

- HTML

- HTTPS

- valtava

- Sadat

- Hybridi

- i

- ajatus

- if

- kuvitella

- vaikutti

- vaikuttavia

- tärkeä

- parantaa

- in

- kannustin

- mukana

- virheellisesti

- Kasvaa

- yhä useammin

- henkilökohtainen

- teollisuus

- tiedot

- Innovaatio

- sisällä

- yhdistää

- eheys

- toisiinsa

- liitäntä

- tulee

- johon

- kysymys

- kysymykset

- IT

- SEN

- itse

- Job

- vain

- Tietää

- tunnettu

- laboratorio

- suuri

- suurempi

- suurin

- Viive

- myöhemmin

- kerros

- johtaa

- oppiminen

- kirjain

- Taso

- Lisenssi

- pitää

- rajallinen

- LINK

- linkit

- paikallinen

- katso

- näköinen

- Erä

- erien

- Matala

- ylläpitää

- tehdä

- Tekeminen

- johto

- johtaja

- valmistus

- monet

- markkinat

- max-width

- ehkä

- me

- välineet

- tarkoitti

- mekaaninen

- keskikokoinen

- Muistoja

- Muisti

- ehkä

- mallit

- lisää

- eniten

- liikkua

- siirretty

- liike

- liikkuvat

- paljon

- my

- Tarve

- tarpeet

- ei ikinä

- Uusi

- yön

- solmut

- nyt

- numero

- of

- pois

- Vanha

- on

- ONE

- vain

- avata

- Mahdollisuudet

- Optimoida

- optimoitu

- optimoimalla

- Vaihtoehto

- Vaihtoehdot

- or

- tilata

- Muut

- Muuta

- ulos

- yleinen

- Voittaa

- oma

- paketit

- pakkaus

- sivut

- Parallel

- osa

- erityinen

- kulkea

- polku

- polut

- PC

- Ihmiset

- suorittaa

- suorituskyky

- näkökulma

- fyysinen

- fyysisesti

- mänty

- kone

- Platon

- Platonin tietotieto

- PlatonData

- Kohta

- mahdollinen

- mahdollisesti

- teho

- puheenjohtaja

- aiemmin

- todennäköisesti

- Ongelma

- Suoritin

- prosessorit

- Tuotteet

- tuotehallinta

- tuotanto

- Ohjelma

- asianmukainen

- asianmukaisesti

- toimittaa

- laittaa

- kysymys

- melko

- nostamalla

- hinta

- pikemminkin

- Lukeminen

- ihan oikeesti

- liittyvä

- luottaa

- tarvitaan

- Vaatii

- ratkaisee

- vastaamisen

- johtua

- Eroon

- oikein

- Nousta

- roolit

- rulla

- ajaa

- juoksu

- sama

- Säästä

- Säästöt

- sanonta

- Asteikko

- Toinen

- nähdä

- koska

- näyttää

- nähneet

- semantiikka

- puolijohde

- lähettää

- anturi

- anturit

- palvelimet

- useat

- arkkia

- siirtää

- lähettää

- puoli

- Sides

- Siemens

- signaali

- signaalit

- Pii

- samankaltainen

- Yksinkertainen

- simulointi

- simulaatiot

- koska

- single

- Koko

- lähtö

- So

- Tuotteemme

- ratkaisu

- Ratkaisumme

- jonkin verran

- hienostunut

- puhuu

- erityinen

- käytetty

- Puristaa

- pino

- pinottu

- pinoaminen

- standardoitu

- näkökulma

- Alkaa

- alkoi

- Aloita

- Vaihe

- Steve

- Steven

- Yhä

- Levytila

- verkkokaupasta

- taistelu

- niin

- Tuetut

- varma

- järjestelmä

- järjestelmät

- taulukko

- ottaa

- Puhua

- tiimit

- teknologi

- Elektroniikka

- ehdot

- testi

- Testaus

- testit

- kuin

- että

- -

- Tulevaisuus

- heidän

- Niitä

- sitten

- Siellä.

- lämpö-

- Nämä

- ne

- asia

- asiat

- ajatella

- kolmas

- tätä

- ne

- ajatus

- Kautta

- aika

- että

- tänään

- yhdessä

- työkalu

- työkalut

- ylin

- TÄYSIN

- kompromissit

- perinteinen

- perinteisesti

- koulutus

- kuljettaa

- Trend

- totta

- yrittää

- kaksi

- kaksi kolmasosaa

- tyyppi

- ymmärtää

- yksiköt

- yliopisto

- us

- käyttää

- käytetty

- käyttämällä

- validointi

- arvo

- vaihtelut

- eri

- hyvin

- pahe

- Varapresidentti

- Näytä

- Virtual

- of

- kävely

- Seinä

- haluta

- oli

- Tapa..

- we

- paino

- HYVIN

- olivat

- Mitä

- mikä tahansa

- kun

- onko

- joka

- vaikka

- valkoinen

- koko

- miksi

- tulee

- with

- ilman

- riiata

- Referenssit

- työtä kotoa

- työskentely

- pahin

- kirjoittaminen

- te

- Sinun

- zephyrnet