2010-luvun aikana Mooren lain edut alkoivat hajota. Mooren lain mukaan transistorin tiheys kaksinkertaistuu joka toinen vuosi, laskennan kustannukset pienenevät vastaavalla 50 prosentilla. Muutos Mooren laissa johtuu lisääntyneestä suunnittelun monimutkaisuudesta transistorirakenteen kehityksestä tasomaisista laitteista Finfeteihin. Finfetit tarvitsevat useita kuviointia litografiaa varten saavuttaakseen laitteiden mitat alle 20 nm:n solmuihin.

Tämän vuosikymmenen alussa tietojenkäsittelytarpeet ovat kasvaneet räjähdysmäisesti, mikä johtuu pääasiassa tietokeskusten lisääntymisestä sekä tuotetun ja käsiteltävän datan määrästä. Itse asiassa tekoälyn (AI) ja koneoppimisen (ML) kaltaisten tekniikoiden käyttöönottoa käytetään nykyään jatkuvasti kasvavan tiedon käsittelyyn, ja se on johtanut siihen, että palvelimet ovat lisänneet merkittävästi laskentakapasiteettiaan.

Palvelimet ovat lisänneet paljon enemmän CPU-ytimiä, ovat integroineet suurempia GPU:ita, joita käytetään yksinomaan ML:ssä, joita ei enää käytetä grafiikkaan, ja niihin on upotettu mukautettuja ASIC AI -kiihdyttimiä tai täydentäviä, FPGA-pohjaisia tekoälyprosessointeja. Varhaiset AI-sirusuunnittelut toteutettiin käyttämällä suurempia monoliittisia SoC:ita, joista osa saavutti hiusristikkon asettaman kokorajan, noin 700 mm2.

Tässä vaiheessa hajottaminen pienempään SoC:hen sekä erilaisiin laskenta- ja IO-siruihin näyttää olevan oikea ratkaisu. Useat sirujen valmistajat, kuten Intel, AMD tai Xilinx, ovat valinneet tämän vaihtoehdon tuotantoon tuleville tuotteille. The Linley Groupin erinomaisessa valkoisessa kirjassa "Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small" osoitettiin, että tämä vaihtoehto johtaa parempiin kustannuksiin verrattuna monoliittisiin SoC:eihin, koska suurempien tuottovaikutus on.

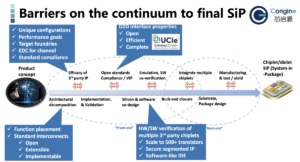

Tämän suuntauksen suurin vaikutus IP-toimittajiin liittyy lähinnä yhteenliittämistoimintoihin, joita käytetään SoC:iden ja sirujen linkittämiseen. Tässä vaiheessa (Q3 2021) on käytössä useita protokollia, ja teollisuus yrittää rakentaa muodollisia standardeja monille niistä.

Nykyiset johtavat D2D-standardit sisältävät i) Advanced Interface Bus (AIB, AIB2), jonka alun perin määritteli Intel ja joka on nyt tarjonnut rojaltivapaata käyttöä, ii) High Bandwidth Memory (HBM), jossa DRAM-muistit on pinottu päällekkäin piivälityslaitteen päälle. ja ne on yhdistetty TSV:iden avulla. iii) Avoin verkkotunnuskohtainen arkkitehtuuri (ODSA) -alaryhmä, toimialaryhmä, on määritellyt kaksi muuta rajapintaa, Bunch of Wires (BoW) ja OpenHBI.

Heterogeeninen sirusuunnittelu mahdollistaa kohdistamisen eri sovelluksiin tai markkinasegmentteihin muokkaamalla tai lisäämällä vain asiaankuuluvia siruja ja pitämällä muun järjestelmän ennallaan. Uusia kehityshankkeita voitaisiin tuoda markkinoille nopeammin huomattavasti pienemmillä investoinneilla, koska uudelleensuunnittelu vaikuttaa vain sirujen sijoittamiseen käytettävään pakkausalustaan.

Esimerkiksi laskentapiiri voidaan suunnitella uudelleen TSMC 5 nm:stä TSMC 3 nm:ksi integroidaksesi suuremman L1-välimuistin tai tehokkaamman suorittimen ytimet, samalla kun muu järjestelmä pysyy muuttumattomana. Spektrin vastakkaisessa päässä vain SerDes-sirut voidaan suunnitella uudelleen nopeampia nopeuksia varten uusissa prosessisolmuissa, jotka tarjoavat enemmän IO-kaistanleveyttä paremman markkina-aseman saavuttamiseksi.

Intel PVC on täydellinen esimerkki heterogeenisestä integraatiosta (eri toiminnalliset sirut, prosessorit, kytkimet jne.), jota voisimme kutsua vertikaaliseksi integraatioksi, kun sama siruvalmistaja omistaa eri sirukomponentit (paitsi muistilaitteita).

Siruvalmistaja, joka kehittää SoC:ita huippuluokan sovelluksiin, kuten HPC:hen, datakeskukseen, tekoälyyn tai verkkoon, on todennäköisesti varhainen omaksuja piirilevyarkkitehtuureille. Tietyt toiminnot, kuten SRAM-muistit suuremmalle L3-välimuistille, tai AI-kiihdyttimiä, joko Ethernet-, PCIe- tai CXL-standardeja, tulisi olla ensimmäinen rajapinta ehdokas piirilevysuunnittelussa.

Kun nämä varhaiset käyttäjät ovat osoittaneet heterogeenisten sirujen pätevyyden hyödyntäen useita erilaisia liiketoimintamalleja, ja ilmeisesti valmistuksen toteutettavuuden testausta ja pakkaamista varten, se luo ekosysteemin, joka on kriittinen tämän uuden teknologian tukemiseksi. Tässä vaiheessa voimme odottaa laajempaa käyttöönottoa markkinoilla, ei vain korkean suorituskyvyn sovelluksissa.

Voisimme kuvitella, että heterogeeniset tuotteet voivat mennä pidemmälle, jos siruvalmistaja tuo markkinoille erilaisista siruista koostuvan järjestelmän, joka kohdistuu laskenta- ja IO-toiminnallisuuksiin. Tämä lähestymistapa tekee konvergenssista D2D-protokollan suhteen pakollisen, koska IP-toimittaja, joka tarjoaa siruja talon sisäisellä D2D-protokollalla, ei ole houkutteleva alalle.

Analogia tähän on 2000-luvun SoC-rakennus, jossa puolijohdeyritykset siirtyvät integroimaan erilaisia suunnittelu-IP:itä, jotka tulevat eri lähteistä. 2000-luvun IP-toimittajista tulee väistämättä 2020-luvun sirujen myyjiä. Tietyille toiminnoille, kuten edistyneille SerDeille tai monimutkaisille protokollille, kuten PCIe, Ethernet tai CXL, IP-toimittajilla on paras tietotaito toteuttaa se piillä.

Monimutkaisen suunnittelu-IP:n kohdalla toimittajien on vahvistettava pii-IP, vaikka simulaatiotarkistus olisi suoritettu ennen toimitusta asiakkaille, suorituskyvyn takaamiseksi. Digitaalisessa IP:ssä toiminto voidaan toteuttaa FPGA:ssa, koska se on nopeampaa ja paljon halvempaa kuin testisirun valmistaminen. Sekoitetun signaalin IP:lle, kuten SerDes-pohjaiselle PHY:lle, toimittajat valitsevat Test Chip (TC) -vaihtoehdon, jolloin piin avulla he voivat karakterisoida IP-osoitteen piissä ennen toimittamista asiakkaalle.

Vaikka siru ei ole pelkkä TC, koska se testataan ja pätevöidään laajasti ennen käyttöä kentällä, toimittajan on tehtävä paljon vähemmän työtä tuotantosirun kehittämiseksi. Toisin sanoen IP-toimittajalla on parhaat mahdollisuudet vapauttaa nopeasti omasta IP-osoitteestaan rakennettu siru ja tarjota paras mahdollinen TTM ja minimoida riskit.

Heterogeenisen integraation liiketoimintamalli suosii sitä, että asianomaiset IP-toimittajat valmistavat erilaisia siruja (esim. ARM ARM-pohjaisille CPU-siruille, Si-Five Risc-V-pohjaisille laskentasiruille ja Alphawave nopeille SerDes-siruille). he ovat Design IP:n omistajia.

Tämä ei estä sirujen valmistajia suunnittelemasta omia siruja ja hankkimasta kompleksisuunnittelun IP-osoitteita ainutlaatuisten arkkitehtuuriensa suojaamiseksi tai kotitekoisten yhteyksien toteuttamiseksi. Samoin kuin SoC Design IP 2000-luvulla, sirujen osto-tai tee-päätös painotetaan ydinosaamisen suojan ja erottumattomien toimintojen hankinnan välillä.

Olemme nähneet, että historiallinen ja nykypäivän Design IP -liiketoiminnan kasvu 2000-luvulta lähtien on pysynyt yllä jatkuvalla ulkoisten hankintojen käyttöönotolla. Molemmat mallit toimivat rinnakkain (itse tai IP-toimittajan suunnittelema siru), mutta historia on osoittanut, että ostopäätös lopulta tekee päätöksen.

Alalla vallitsee nyt yksimielisyys siitä, että hullunkurinen keskittyminen Mooren lain saavuttamiseen ei päde enää edistyneen teknologian solmuille, esim. 7nm ja alle. Siruintegraatiota tapahtuu edelleen, ja jokaisessa uudessa teknologiasolmussa lisätään enemmän transistoreja neliömillimetriä kohden. Kuitenkin myös transistorin hinta kasvaa joka uudella solmulla.

Chiplet-tekniikka on keskeinen aloite, jolla pyritään lisäämään tärkeimmän SoC:n integraatiota samalla kun käytetään vanhempia solmuja muihin toimintoihin. Tämä hybridistrategia vähentää sekä kustannuksia että suunnitteluriskiä, jotka liittyvät muun Design IP:n integroimiseen suoraan pääkäyttöjärjestelmään.

IPnest uskoo, että tällä trendillä on kaksi pääasiallista vaikutusta rajapinta-IP-liiketoimintaan, joista toinen on D2D IP -tuottojen voimakas kasvu pian (2021-2025), ja toinen on heterogeenisten sirumarkkinoiden luominen täydentämään huippuluokan piitä. IP-markkinat.

Näiden markkinoiden odotetaan koostuvan monimutkaisista protokollatoiminnoista, kuten PCIe, CXL tai Ethernet. IP-toimittajat, jotka toimittavat I/O-sovituksiin (USB, HDMI, DP, MIPI jne.) integroidun IP-liittymän, voivat päättää toimittaa sen sijaan I/O-siruja.

Muut IP-luokat, joihin tämä vallankumous vaikuttaa, ovat SRAM-muistin kääntäjien IP-toimittajat L3-välimuistille. Luonnostaan välimuistin koon odotetaan vaihtelevan prosessorin mukaan. Siitä huolimatta L3-välimuistisirun suunnittelu voi olla tapa IP-toimittajalle lisätä Design IP -tuloja tarjoamalla uutta tuotetyyppiä.

Myös NVM IP -luokkaan voi olla positiivinen vaikutus, koska NVM IP:tä ei enää ole integroitu edistyneille prosessisolmuille suunniteltuihin SoC:ihin. Se olisi tapa NVM IP -toimittajille luoda uutta liiketoimintaa tarjoamalla siruja.

Uskomme, että FPGA- ja AI-kiihdytinpiirit ovat uusi tulonlähde ASSP-sirujen valmistajille, mutta uskomme, että niitä ei voida luokitella tiukasti IP-toimittajiksi.

Jos Interface IP -toimittajat ovat merkittäviä toimijoita tässä piivallankumouksessa, myös edistyneimmille solmuille, kuten TSMC:lle ja Samsungille, keskittyvät piivalimot ovat avainasemassa. Emme usko, että valimot suunnittelevat siruja, mutta ne voisivat tehdä päätöksen tukea IP-toimittajia ja saada heidät suunnittelemaan siruja käytettäviksi 3nm:n SoC:iden kanssa, kuten he tekevät nykyään, kun he tukevat edistyneitä IP-toimittajia markkinoimaan huippuluokan SerDe-laitteitaan. kova IP 7nm ja 5nm.

Intel on hiljattain siirtynyt 3rd puoluevalimoiden odotetaan myös hyödyntävän kolmansien osapuolien IP-osoitteita sekä puolijohteiden raskassarjan heterogeenisten sirujen käyttöönottoa. Tässä tapauksessa ei ole epäilystäkään siitä, että Microsoftin, Amazonin ja Googlen kaltaiset hyperskalaarit ottavat käyttöön myös siruarkkitehtuurit… jos ne eivät edeltä Inteliä sirujen käyttöönotossa.

By Eric Esteve (PhD.) Analyytikko, Omistaja IPnest

Jaa tämä viesti: Lähde: https://semiwiki.com/semiconductor-services/ipnest/303790-chiplet-are-you-ready-for-next-semiconductor-revolution/

- 2021

- kiihdytin

- kiihdyttimiä

- Hyväksyminen

- Advanced Technology

- AI

- Salliminen

- Amazon

- AMD

- analyytikko

- sovellukset

- arkkitehtuuri

- ARM

- tekoäly

- Tekoäly (AI)

- ASIC

- PARAS

- rakentaa

- Rakentaminen

- Nippu

- bussi

- liiketoiminta

- liiketoimintamalli

- Ostetaan

- soittaa

- Koko

- muuttaa

- siru

- sirut

- tuleva

- Yritykset

- Laskea

- tietojenkäsittely

- Yhteisymmärrys

- kustannukset

- Asiakkaat

- tiedot

- tuottaa

- Malli

- kehittää

- Laitteet

- digitaalinen

- Varhainen

- varhaisessa vaiheessa

- ekosysteemi

- jne.

- evoluutio

- Etunimi

- Keskittää

- FPGA

- Ilmainen

- toiminto

- GPU

- Ryhmä

- Kasvava

- Kasvu

- Korkea

- historia

- Talo

- HTTPS

- Hybridi

- Vaikutus

- Kasvaa

- teollisuus

- aloite

- integraatio

- Intel

- Älykkyys

- investointi

- IP

- IT

- pito

- avain

- käynnistää

- Laki

- johtava

- oppiminen

- Led

- Vaikutusvalta

- LINK

- koneoppiminen

- merkittävä

- valmistaja

- Tekeminen

- valmistus

- markkinat

- Microsoft

- ML

- malli

- verkostoituminen

- uusi tuote

- solmut

- kampanja

- tarjoamalla

- avata

- Vaihtoehto

- Muut

- omistaja

- pakkaus

- Paperi

- suorituskyky

- Tuotteet

- tuotanto

- Tuotteemme

- suojella

- suojaus

- Hinnat

- uudistamiseksi

- REST

- Riski

- ajaa

- Samsung

- puolijohde

- Lähetys

- simulointi

- Koko

- standardit

- Strategia

- tuki

- Vaihtaa

- järjestelmä

- Kohde

- tekniikat

- Elektroniikka

- testi

- ylin

- us

- usb

- myyjät

- Vahvistus

- valkoinen paperi

- sanoja

- Referenssit

- vuotta

- tuotto