Aiemmin bloggain aiheesta IC- ja ASIC-toiminnan tarkastus, joten tänään on aika täydentää se FPGA-toimintojen varmistuksen tilalla. Wilson Research Group on laatinut FPGA-raportin joka toinen vuosi vuodesta 2018 lähtien, joten tämä on kolmas kerta, kun se keskittyy tähän suunnittelusegmenttiin. 5.8 miljardin dollarin FPGA-markkinat ovat suuret, ja niiden ennustetaan kasvavan 8.1 miljardiin dollariin vuoteen 2025 mennessä. FPGA:t otettiin käyttöön vuonna 1984 rajoitetulla porttikapasiteetilla, ja ne ovat nyt kasvaneet sisältämään miljoonia portteja, prosessoreita ja standardoituja dataprotokollia.

Pienen volyymin sovellukset hyötyvät FPGA-laitteiden NRE:stä, ja insinöörit voivat nopeasti prototyyppiä suunnitelmansa tarkistamalla ja validoimalla nopeasti. FPGA:t sisältävät nyt prosessoreita, kuten: Xilinx Zynq UltraSCALE, Intel Stratix, Microchip SmartFusion. Toimintavarmennustutkimukseen osallistuneesta 980:sta FPGA- ja ohjelmoitava SoC FPGA -suunnittelutyylit ovat suosituimpia.

Koska FPGA:iden koko on kasvanut viime aikoina, virheetön tuotantojulkaisun mahdollisuus on pudonnut vain 17 prosenttiin, mikä on vielä huonompi kuin 30 % IC- ja ASIC-projekteista oikean ensimmäisen piin kohdalla. On selvää, että tarvitsemme parempaa toiminnallista varmennusta monimutkaisille FPGA-järjestelmille.

Tuotannossa löydetyt bugityypit jakautuvat useisiin luokkiin:

- 53 % – looginen tai toiminnallinen

- 31 % – laiteohjelmisto

- 29 % – Kello

- 28 % – Ajoitus, polku liian hidas

- 21 % – Ajoitus, polku liian nopea

- 18 % – Sekasignaaliliitäntä

- 9 % – Turvaominaisuus

- 8 % – Suojausominaisuus

Tarkasteltaessa suurinta vikaluokkaa, logiikkaa tai toiminnallista, on viisi perimmäistä syytä.

FGPA-projektit eivät pääsääntöisesti valmistuneet ajoissa, mikä taas johtui järjestelmien suuresta koosta, logiikan monimutkaisuudesta ja jopa käytettävistä varmennusmenetelmistä.

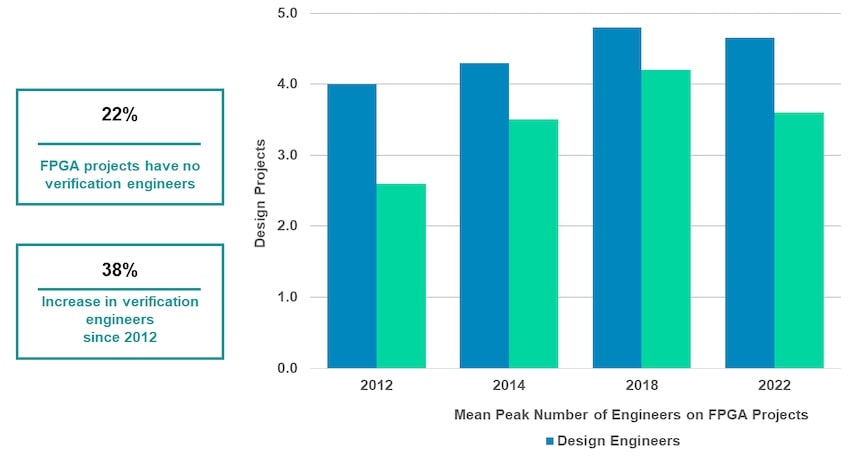

FPGA-tiimin insinööreillä voi olla eri titteleitä, kuten suunnitteluinsinööri tai todentaja, mutta 22 prosentissa projekteista ei ollut varmennusinsinöörejä – mikä tarkoittaa, että suunnitteluinsinöörit tekivät kaksinkertaisen tehtävänsä ja vahvistivat oman IP-osoitteensa. Viimeisten 10 vuoden aikana FPGA-projektin varmistusinsinöörien määrä on kasvanut 38 %, joten se on edistystä kohti virheetöntä tuotantoa.

FPGA-projektien varmistusinsinöörit käyttivät suurimman osan ajastaan virheenkorjaustehtäviin 47 prosentilla:

- 47 % – virheenkorjaus

- 19 % – Testin luominen ja simuloinnin suorittaminen

- 17 % – Testbench-kehitys

- 11 % – Testin suunnittelu

- 6 % – muut

Sulautettujen prosessorien määrä on kasvanut tasaisesti ajan myötä, joten 65 prosentissa FPGA-malleista on nyt yksi tai useampi prosessoriydin, mikä lisää varmennusten määrää laitteiston ja ohjelmiston rajapintojen välillä; ja siruverkkojen hallinta.

Yhä suosittu RISC-V-prosessori on upotettu 22 %:iin FPGA:ista, ja tekoälykiihdyttimiä käytetään 23 %:ssa projekteista. FPGA:ssa käytetään keskimäärin 3-4 kelloaluetta, ja ne vaativat porttitason ajoitussimulaatioita varmentamiseen sekä staattisten Clock Domain Crossing (CDC) -työkalujen käytön vahvistamiseen.

Suojausominaisuudet on lisätty 49 prosenttiin FPGA-malleista arkaluontoisten tietojen säilyttämiseksi, ja 42 % FPGA-projekteista noudattaa turvallisuuskriittisiä standardeja tai ohjeita. SemiWikissä olemme usein kirjoittaneet blogia aiheesta ISO 26262 ja TO-254 standardit. Functional Safety (FuSa) -suunnittelutyöt vievät 25–50 % projektin kokonaisajasta.

Kolme parasta vahvistuskieliä ovat VHDL, SystemVerilog ja Verilog; mutta huomaa myös viimeaikaiset hyppyt Python- ja C/C++-kielissä.

Suosituimmat FPGA-menetelmät ja testipenkkiperuskirjastot ovat: Accellera UVM, OSVVM ja UVVM. Python-pohjainen cocotb lisättiin jopa uutena kategoriana vuodelle 2022.

Väitekieliä johtavat SystemVerilog Assertions (SVA) 45 prosentilla, jota seuraa Accellera Open Verification Library (OVL) 13 prosentilla ja PSL 11 prosentilla. FPGA-malleissa voidaan yhdistää VHDL RTL-suunnittelua varten sekä SVA väitteisiin.

Muodollinen omaisuuden tarkistus lisääntyy FPGA-projektien keskuudessa, varsinkin kun EDA-toimittajat ovat ottaneet käyttöön enemmän automaattisia muodollisia sovelluksia.

Simulaatioon perustuvat todentamismenetelmät viimeisten 10 vuoden aikana osoittavat jatkuvaa käyttöönottoa, jotka on listattu merkityksellisyyden järjestyksessä: koodin kattavuus, toiminnallinen kattavuus, väitteet, rajoitettu satunnainen.

Yhteenveto

Vuonna 17 tuotantoon päässyt FPGA-projektien alhainen 2022 % bugiton luku oli minusta yllättävin luku, sillä laitteen palauttaminen tai ohjelmointi kentällä on kallista ja aikaa vievää korjata. Vahvemman toiminnallisen varmennustavan pitäisi johtaa siihen, että tuotantoon pääsee vähemmän virheitä, ja tutkimuksen osallistujien jakaminen kahteen ryhmään osoittaa hyödyn.

Lue koko teksti 18-sivuinen valkoinen paperi täällä.

Liittyvät blogit

Jaa tämä viesti:

- SEO-pohjainen sisällön ja PR-jakelu. Vahvista jo tänään.

- Platoblockchain. Web3 Metaverse Intelligence. Tietoa laajennettu. Pääsy tästä.

- Lähde: https://semiwiki.com/eda/324651-the-state-of-fpga-functional-verification/

- 1

- 10

- 2018

- 2022

- a

- Meistä

- kiihdyttimiä

- lisä-

- noudattaa

- Hyväksyminen

- AI

- keskuudessa

- määrä

- ja

- sovellukset

- lähestymistapa

- lähestymistavat

- sovellukset

- ASIC

- automaattisesti

- keskimäärin

- ovat

- hyödyttää

- Paremmin

- välillä

- Miljardi

- Vika

- Bugs

- Koko

- luokat

- Kategoria

- Aiheuttaa

- aiheutti

- syyt

- CDC

- mahdollisuus

- tarkkailun

- selvästi

- kello

- koodi

- yhdistää

- täydellinen

- monimutkainen

- monimutkaisuus

- kattavuus

- Luominen

- kriittinen

- tiedot

- Malli

- mallit

- laite

- Laitteet

- DID

- selvä

- verkkotunnuksen

- verkkotunnuksia

- putosi

- vaivaa

- ponnisteluja

- upotettu

- insinööri

- Engineers

- erityisesti

- Jopa

- Joka

- kallis

- Epäonnistuminen

- Pudota

- Ominaisuudet

- ala

- Etunimi

- keskityttiin

- seurannut

- muodollinen

- löytyi

- FPGA

- alkaen

- toiminnallinen

- Gates

- Ryhmä

- Ryhmän

- Kasvaa

- Kasvava

- täysikasvuinen

- suuntaviivat

- Palvelimet

- pitää

- HTML

- HTTPS

- in

- sisältää

- Kasvaa

- kasvoi

- lisää

- Intel

- rajapinnat

- käyttöön

- IP

- IT

- hyppyjä

- kielet

- suurempi

- suurin

- johtaa

- Led

- kirjastot

- Kirjasto

- rajallinen

- lueteltu

- Matala

- tehty

- toimitusjohtaja

- markkinat

- max-width

- merkitys

- menetelmiä

- menetelmät

- miljoonia

- lisää

- eniten

- Suosituin

- Tarve

- verkot

- Uusi

- numero

- ONE

- avata

- tilata

- yleinen

- oma

- Paperi

- osallistujat

- Ohi

- polku

- Platon

- Platonin tietotieto

- PlatonData

- plus

- Suosittu

- Kirje

- Suoritin

- prosessorit

- tuotanto

- Edistyminen

- projekti

- hankkeet

- omaisuus

- protokollat

- prototyyppi

- Python

- nopeasti

- satunnainen

- äskettäinen

- äskettäin

- vapauta

- Merkitys

- raportti

- edellyttää

- tutkimus

- tutkimusryhmä

- luja

- juuri

- kierros

- juoksu

- Turvallisuus

- turvallisuus

- segmentti

- sensible

- useat

- shouldnt

- näyttää

- Näytä

- Siemens

- Pii

- koska

- melkoinen

- Koko

- So

- Tuotteemme

- nopeus

- käytetty

- standardit

- alkoi

- Osavaltio

- tasainen

- tutkimus

- yllättävä

- järjestelmät

- ottaa

- tehtävät

- joukkue-

- tekniikat

- testi

- -

- Valtion

- heidän

- kolmas

- kolmella

- aika

- ajoitus

- otsikot

- että

- tänään

- liian

- työkalut

- ylin

- kohti

- tyypit

- käyttää

- myyjät

- Vahvistus

- todennettu

- tarkastaa

- kautta

- tilavuus

- joka

- valkoinen

- valkoinen paperi

- Wilson

- vuotta

- zephyrnet