طراحان آی سی آنالوگ می توانند زمان و تلاش زیادی را صرف استفاده مجدد از روش های تکراری قدیمی، آشنا و دستی برای طراحی مدار کنند، فقط به این دلیل که همیشه این روش انجام می شده است. بهینهسازی مدار یک رویکرد EDA است که میتواند به طور خودکار تمام ترانزیستورهای یک سلول را با اجرای شبیهسازیهای SPICE در گوشههای PVT و تغییرات فرآیند اندازهگیری کند تا نیازهای طراحی سیگنال آنالوگ و مختلط را برآورده کند. امیدوار کننده به نظر می رسد، درست است؟

بنابراین من باید از کدام بهینه ساز مدار استفاده کنم؟

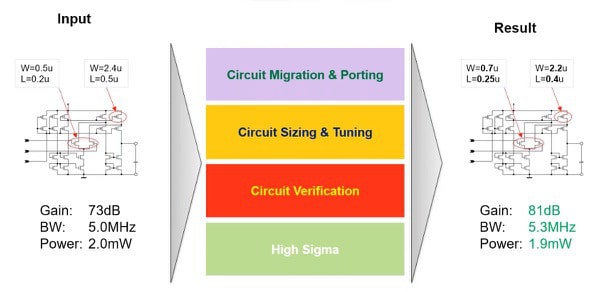

برای پاسخ به این سوال یک وبینار در راه است که توسط میزبانی می شود MunEDA، یک شرکت EDA در سال 2001 شروع به کار کرد و همه چیز در مورد بهینه ساز مدار آنها نامگذاری شده است شرور. ورودی ها یک لیست شبکه SPICE به همراه الزامات طراحی هستند، مانند: بهره، پهنای باند و مصرف انرژی. خروجی ها یک لیست شبکه با اندازه هستند که الزامات طراحی را برآورده می کند یا از آن فراتر می رود.

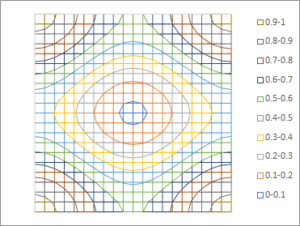

سس مخفی با WiCkeD این است که چگونه یک مدل یادگیری ماشینی (ML) ایجاد می کند تا طراحی آزمایشات (DOE) را برای محاسبه بدترین گوشه PVT، یافتن حساسیت های هندسی ترانزیستور و حتی محاسبه تغییرات روی تراشه (OCV) بسازد. ) حساسیت ها این رویکرد یک مدل ML غیر خطی و با ابعاد بالا را از داده های شبیه سازی شده ایجاد و به روز می کند.

داشتن یک مدل ML ابزار را قادر میسازد تا چالش بهینهسازی را حل کند، سپس با اجرای شبیهسازی SPICE، تأیید نهایی را انجام دهد. تا زمانی که همه الزامات برآورده شوند، تکرارهای خودکار وجود دارد. اکنون این بسیار سریعتر از روش های تکرار دستی قدیمی به نظر می رسد. آموزش مدل ML کاملاً خودکار و کاملاً کارآمد است.

طراحان مدار همچنین یاد خواهند گرفت:

- کجا از بهینه سازی مدار استفاده کنیم

- چه نوع مدارهایی برای بهینه سازی مناسب هستند

- بهینه سازی مدار چقدر برای جریان طراحی به ارمغان می آورد

مهندسان در STMicroelectronics از بهینه سازی مدار در WiCkeD استفاده کرده اند و MunEDA در مورد نتایج خاص آنها در صرفه جویی در زمان و بهبود در برآوردن نیازها صحبت می کند. شرکت تقویت کننده قدرت Inplay Technologies نتایج بهینه سازی مدار را از کنفرانس DAC 2018 نشان داد.

جزئیات وبینار

مشاهده وبینار در 11 آوریل، ساعت 10 صبح به وقت محلی توسط ثبت نام آنلاین.

وبلاگهای مرتبط

اشتراک گذاری این پست از طریق:- محتوای مبتنی بر SEO و توزیع روابط عمومی. امروز تقویت شوید.

- پلاتوبلاک چین. Web3 Metaverse Intelligence. دانش تقویت شده دسترسی به اینجا.

- منبع: https://semiwiki.com/eda/326047-webinar-enhance-productivity-with-machine-learning-in-the-analog-front-end-design-flow/

- :است

- $UP

- 2001

- 2018

- a

- درباره ما

- در میان

- معرفی

- همیشه

- و

- پاسخ

- روش

- آوریل

- هستند

- At

- خودکار

- اتوماتیک

- بطور خودکار

- به عقب

- پهنای باند

- زیرا

- به ارمغان می آورد

- می سازد

- by

- محاسبه

- CAN

- به چالش

- تراشه

- آینده

- شرکت

- کنفرانس

- در نظر بگیرید

- مصرف

- گوشه

- گوشه ها

- ایجاد

- داده ها

- طرح

- طراحان

- DOE

- موثر

- تلاش

- را قادر می سازد

- حتی

- تجاوز

- آشنا

- سریعتر

- نهایی

- پیدا کردن

- جریان

- برای

- از جانب

- افزایش

- هندسه

- خوب

- آیا

- میزبانی

- چگونه

- HTTPS

- i

- ارتقاء

- in

- IT

- تکرار

- تکرار

- JPG

- یاد گرفتن

- یادگیری

- پسندیدن

- دستگاه

- فراگیری ماشین

- کتابچه راهنمای

- حداکثر عرض

- دیدار

- نشست

- ملاقات

- روش

- ML

- مدل

- تحت عنوان

- of

- قدیمی

- on

- بهینه سازی

- افلاطون

- هوش داده افلاطون

- PlatoData

- پست

- قدرت

- روند

- بهره وری

- امید بخش

- سوال

- مورد نیاز

- نتایج

- دویدن

- در حال اجرا

- پس انداز

- راز

- باید

- شبیه سازی

- اندازه

- خاص

- خرج کردن

- ادویه

- آغاز شده

- مذاکرات

- فن آوری

- که

- La

- شان

- زمان

- به

- هم

- ابزار

- آموزش

- انواع

- به روز رسانی

- استفاده کنید

- ارزش

- تایید

- از طريق

- مسیر..

- وبینار

- که

- اراده

- با

- زفیرنت