طراحان مسیرهای زیادی برای تمایز راه حل های RISC-V دارند. یک مسیر به سفارشی سازی ها و برنامه های افزودنی هسته RISC-V بر اساس مشخصات راه اندازی می شود. دیگری بر انتخاب و مونتاژ بلوک های IP در طراحی کامل سیستم روی تراشه (SoC) حول یک یا چند هسته RISC-V تمرکز دارد. سومی در حال ظهور است: اتصال هسته های RISC-V و سایر بلوک های IP با یک شبکه روی تراشه (NoC) به جای ساختار گذرگاه ساده. و این فقط در سطح بالایی نیست - جفت شدن هسته های RISC-V با NoC به بسیاری از چالش های طراحی SoC پاسخ می دهد که در آن داده ها باید به طور موثر در هر حجم کاری با استفاده از هر پروتکل روی تراشه جریان داشته باشند.

سطوح عملکرد در حال تغییر با طرح های اتصال پیشرفته

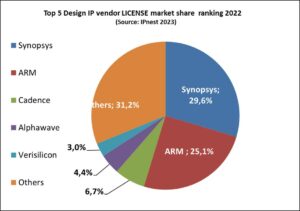

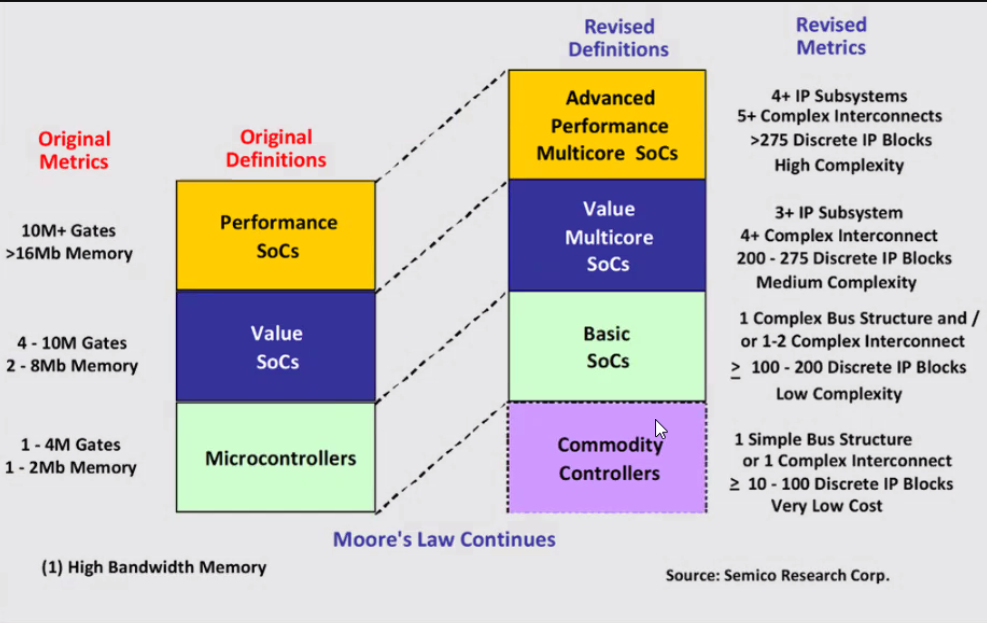

شمارش ساده گیت ها، هسته ها و بلوک های جانبی دیگر پتانسیل عملکرد یک طراحی SoC را توصیف نمی کند. طبق تحقیقات Semico، طرحهای اتصال در حال حاضر خطوط بین سطوح عملکرد SoC را مشخص میکنند، و یک لایه جدید باز شده است که در آن اتصالات از ساختارهای اتوبوس ساده به طرحهای پیچیدهتر تغییر میکنند.

تعریف بهروزشده Semico سه نیرو را در کار تشخیص میدهد: فراگیر بودن طرحهای چند هستهای، نوار بالاتر برای آنچه طراحی پیچیده در نظر گرفته میشود، و متعاقباً خط محو بین «میکروکنترلر» و «SoC». در آخرین دیدگاه Semico، مفهوم گیت به عنوان یک متریک ناپدید میشود، زیرا یک هسته پردازنده مدرن میتواند گیتهای زیادی را با خود بکشد. پیچیدگی تابعی از اتصالات است که با زیرسیستم ها و بلوک های IP متنوع متفاوت است.

سطوح عملکرد SoC، تصویر توسط Semico Research Corp.

جایی که یک گذرگاه ساده، احتمالاً بخشی با یک هسته پردازشگر واحد و تجهیزات جانبی با چرخه کاری کم که به طور مداوم برای گذرگاه رقابت نمی کنند، کار می کند، Semico یک ردیف کنترل کننده کالا را می بیند. هر چیزی بالاتر از آن تبدیل به یک SoC می شود، احتمالاً با حداقل برخی از تجهیزات جانبی که برای پهنای باند روی تراشه و توجه هسته (های) پردازنده مبارزه می کنند. سطوح بالاتر SoC دارای چندین هسته و چندین زیرسیستم IP هستند که هر کدام دارای فناوری اتصال تنظیم شده هستند.

NoCها پروتکل ها و زیرسیستم های بیشتری را انتخاب می کنند

RISC-V با ظاهر شدن هستههای قدرتمندتر، بدون کاربرد کمتر در انتهای پایینتر مقیاس Semico، به سرعت این سطوح عملکرد را بالا برده است. با این حال، طراحان RISC-V ممکن است تجربه کمتری در طرحهای اتصال پیچیده که در سطوح بالاتر دیده میشوند، داشته باشند. Frank Schirrmeister، معاون راه حل ها و توسعه کسب و کار برای Arteris می گوید: «TileLink ممکن است اولین فکر برای اتصال RISC-V باشد، اما استفاده از آن در سناریوهای پیچیده تر می تواند دشوار باشد.

ابرقدرت NoC توانایی آن در اتصال زیرسیستمها با استفاده از پروتکلهای مختلف است و طراحان SoC احتمالاً با چندین پروتکل با پیچیدگی متوسط مواجه میشوند. AXI زمین بازی را برای اتصالات بلوک IP ساده تراز کرد. راهحلهای چند هستهای با بلوکهای پردازش مشترک، انسجام حافظه پنهان را طلب میکنند که باعث ایجاد پروتکل CHI میشود. اشتراکگذاری حافظه ورودی/خروجی به شکلگیری اتصال سریعتر CXL کمک کرد. Schirrmeister ادامه میدهد: «وقتی زمان بهینهسازی محاسبات و حمل و نقل با زیرسیستمها و پروتکلهای مختلف میرسد، یک NoC راهحل بهتری است.

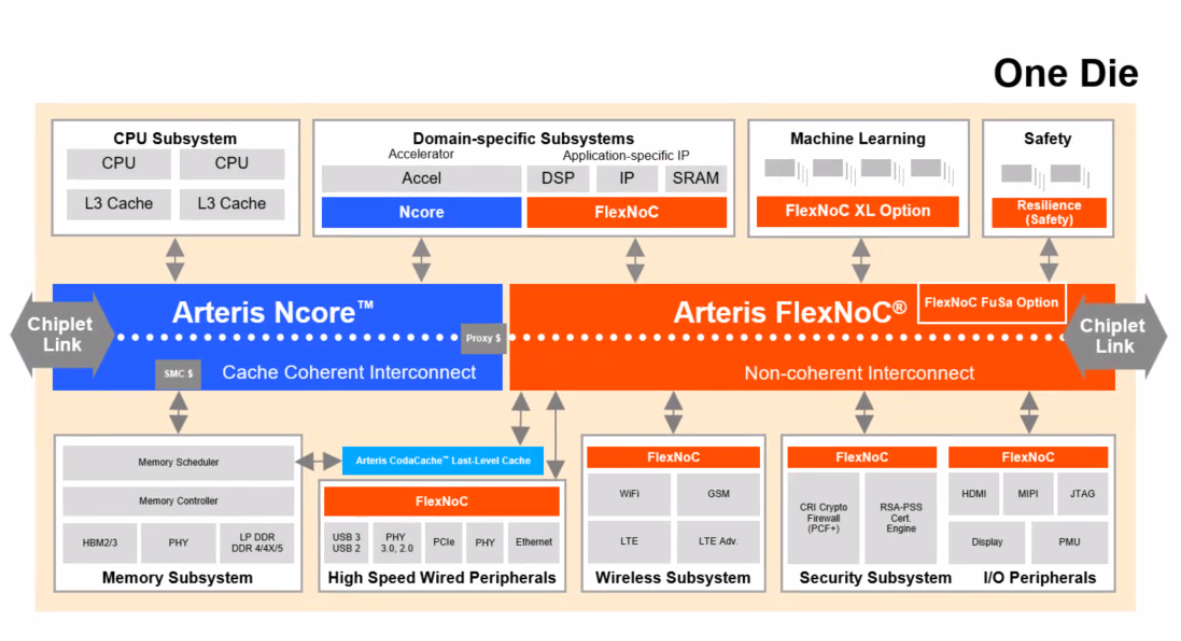

جفت شدن هسته های RISC-V با NoCها چگونه می تواند باشد؟ مشتری Arteris Tenstorrent نگاهی اجمالی به احتمالات ارائه می دهد. تمرکز اخیر آنها بر ایجاد یک چیپلت قابل استفاده مجدد است که هستههای RISC-V، IP شتابدهنده یادگیری ماشینی و تجهیزات جانبی استاندارد موجود در بسیاری از برنامههای هوش مصنوعی لبه را ترکیب میکند. در مقیاس، یک پیادهسازی تک دای میتواند شبیه نمودار زیر باشد، با استفاده از اتصال داخلی کش-همدوس Arteris Ncore و چندین بخش از اتصال غیر منسجم Arteris FlexNoC.

تصویر با حسن نیت ارائه شده است

یک کنترلر حافظه هوشمند (SMC) یک اتصال حافظه با کارایی بالا و درجه سرور را در برنامه های کاربردی با حافظه فشرده فراهم می کند. "پیوند تراشه" بدون نام می تواند UCIe باشد، یک مشخصات نسبتاً جدید که برای ادغام دقیق تر چیپلت ها بهینه شده است. هنگامی که زیرسیستم های جدید به هم متصل می شوند، تطبیق بخشی از NoC قابل مدیریت تر از پاره کردن کل ساختار تراشه است.

جفت شدن هسته های RISC-V با NoCها ریسک و زمان ورود به بازار را کاهش می دهد

اگر این نمودار پیچیده به نظر میرسد، شاید اکثر برنامههای RISC-V در حال حاضر آنقدر پیچیده نیستند، این را در نظر بگیرید: چیپلتها در حال حاضر ادغام را بسیار بالاتر میبرند. بخش پیشرفته RISC-V چند هستهای امروزی با افزایش سرعت نوآوری، SoC ارزش سال آینده خواهد بود.

ابزارهای توسعه Arteris Ncore و Arteris FlexNoC RTL را برای پیاده سازی خروجی می دهند و چندین مزیت را ارائه می دهند. تخمین فیزیکی NoC در یک گردش کار EDA ساده است. تنظیمات پارامتر NoC، مانند تعداد مراحل خط لوله، در ابزار EDA نیز با چند کلیک فاصله دارد. تغییرات ذکر شده در بالا برای افزودن یک پروتکل زیرسیستم نیز به آسانی انجام می شود. Schirrmeister میگوید: «در بالاترین سطح، کاربران بلافاصله به تخصص NoC ما دسترسی پیدا میکنند. در پایین ترین سطح، استفاده از ابزارهای ما برای موفقیت در مرحله اول آسان است و مسیر رشد را برای پروژه های آینده بلندپروازانه تر با اتصالات پیچیده فراهم می کند.

جفت شدن هستههای RISC-V با NoCها، خطر ورود یک بلوک IP دیگر به طراحی و ایجاد موجی از طراحی مجدد اتصالات درون تراشه را کاهش میدهد. همچنین زمان ورود به بازار را برای طراحیهای پیچیده SoC در مقایسه با ساختارهای اتصال خود انجام دهید کاهش میدهد. ما در اینجا درباره مزایای دیگر NoCها مانند پهنای باند و مدیریت توان صحبت نکردهایم، اما مورد NoCها در طراحیهای RISC-V تنها با در نظر گرفتن ترکیب پروتکلهای متنوع قوی است.

از وب سایت آرتریس دیدن کنید برای اطلاعات بیشتر در مورد NoCs و سایر محصولات

اشتراک گذاری این پست از طریق:

- محتوای مبتنی بر SEO و توزیع روابط عمومی. امروز تقویت شوید.

- PlatoData.Network Vertical Generative Ai. به خودت قدرت بده دسترسی به اینجا.

- PlatoAiStream. هوش وب 3 دانش تقویت شده دسترسی به اینجا.

- PlatoESG. کربن ، CleanTech، انرژی، محیط، خورشیدی، مدیریت پسماند دسترسی به اینجا.

- PlatoHealth. هوش بیوتکنولوژی و آزمایشات بالینی. دسترسی به اینجا.

- منبع: https://semiwiki.com/ip/arteris/336086-pairing-risc-v-cores-with-nocs-ties-soc-protocols-together/

- : دارد

- :است

- :نه

- :جایی که

- $UP

- a

- توانایی

- بالاتر

- شتاب

- دسترسی

- انجام

- مطابق

- در میان

- اضافه کردن

- تنظیمات

- پیشرفته

- مزایای

- AI

- قبلا

- همچنین

- جاه طلب

- an

- و

- دیگر

- پاسخ

- هر

- هر چیزی

- ظاهر شدن

- برنامه های کاربردی

- هستند

- دور و بر

- AS

- At

- توجه

- دور

- پهنای باند

- بار

- BE

- شود

- مزایای

- بهتر

- میان

- مسدود کردن

- بلاک ها

- اتوبوس

- کسب و کار

- توسعه تجاری

- اما

- CAN

- مورد

- چالش ها

- تغییر دادن

- متغیر

- تراشه

- ترکیب

- کالا

- مقایسه

- کامل

- پیچیده

- پیچیدگی

- محاسبه

- اتصال

- ارتباط

- اتصالات

- در نظر بگیرید

- در نظر گرفته

- با توجه به

- ادامه

- به طور مداوم

- کنترل کننده

- هسته

- پارسیان

- میتوانست

- با احتساب

- ایجاد

- مشتری

- داده ها

- تعريف كردن

- تعریف

- تقاضا

- طرح

- طراحان

- طرح

- پروژه

- ابزارهای توسعه

- مختلف

- مشکل

- بحث کردیم

- مختلف

- do

- رانندگی

- هر

- ساده

- لبه

- موثر

- ظهور

- سنگ سنباده

- پایان

- وارد شدن

- تمام

- حتی

- تجربه

- تخصص

- ضمیمهها

- سریعتر

- کمی از

- رشته

- مبارزه با

- نام خانوادگی

- جریان

- تمرکز

- تمرکز

- پیروی

- برای

- نیروهای

- یافت

- رک

- از جانب

- تابع

- آینده

- افزایش

- گیتس

- دادن

- نظر اجمالی

- اعطا شده

- رشد

- آیا

- کمک کرد

- اینجا کلیک نمایید

- زیاد

- عملکرد بالا

- بالاتر

- اما

- HTTPS

- تصویر

- فوری

- پیاده سازی

- in

- اطلاعات

- ابداع

- در عوض

- ادغام

- به هم پیوستگی

- به هم متصل می شود

- به

- IP

- IT

- ITS

- تنها

- آخرین

- راه اندازی

- کمترین

- کمتر

- پسندیدن

- احتمالا

- لاین

- خطوط

- دیگر

- نگاه کنيد

- شبیه

- مطالب

- کم

- کاهش

- مدیریت

- بسیاری

- حداکثر عرض

- ممکن است..

- شاید

- حافظه

- ذکر شده

- متری

- مخلوط

- متوسط

- مدرن

- تغییرات

- بیش

- اکثر

- نقل مکان کرد

- بسیار

- چندگانه

- باید

- جدید

- بعد

- نه

- ایده

- اکنون

- عدد

- of

- on

- ONE

- باز

- بهینه

- or

- دیگر

- ما

- تولید

- سرعت

- جفت کردن

- پارامتر

- بخش

- مسیر

- برای

- کارایی

- پیرامونی

- لوازم جانبی

- فیزیکی

- انتخاب کنید

- کلاهبرداری

- خط لوله

- افلاطون

- هوش داده افلاطون

- PlatoData

- بازی

- بازی

- فرصت

- پست

- پتانسیل

- قدرت

- قوی

- پردازنده

- محصولات

- پروژه ها

- پروتکل

- پروتکل

- ارائه

- فراهم می کند

- ارائه

- به سرعت

- به راحتی

- اخیر

- به رسمیت می شناسد

- طراحی مجدد کردن

- را کاهش می دهد

- نسبتا

- تحقیق

- قابل استفاده مجدد

- راست

- موج دار شدن

- طلوع

- خطر

- دویدن

- s

- می گوید:

- مقیاس

- سناریوها

- طرح ها

- بخش

- مشاهده گردید

- می بیند

- بخش ها

- انتخاب

- چند

- شکل

- اشتراک

- ساده

- پس از

- تنها

- هوشمند

- راه حل

- مزایا

- برخی از

- مصنوعی

- مشخصات

- مراحل

- استاندارد

- ساده

- قوی

- ساختار

- ساختار

- متعاقب

- موفقیت

- چنین

- ابرقدرت

- پیشرفته

- نسبت به

- که

- La

- شان

- اینها

- سوم

- این

- فکر

- سه

- ردیف

- روابط

- محکم تر

- زمان

- به

- امروز

- با هم

- ابزار

- حمل و نقل

- راه اندازی

- بی نام

- به روز شده

- استفاده کنید

- کاربران

- با استفاده از

- ارزش

- مختلف

- متفاوت است

- از طريق

- چشم انداز

- vp

- we

- سایت اینترنتی

- چی

- چه شده است

- چه زمانی

- اراده

- با

- مهاجرت کاری

- گردش کار

- زفیرنت