Auf dem Weg zu leistungsfähigeren, schnelleren, kleineren und stromsparenderen Systemen verschaffte das Mooresche Gesetz der Software mehr als 30 Jahre lang freie Fahrt, allein auf der Weiterentwicklung von Halbleiterprozessen. Compute-Hardware lieferte jedes Jahr verbesserte Leistungs-/Bereichs-/Leistungsmetriken, sodass die Software komplexer werden und mehr Leistungsfähigkeit ohne Nachteile bieten konnte. Dann wurden die einfachen Siege weniger einfach. Fortgeschrittenere Prozesse lieferten weiterhin höhere Gate-Anzahlen pro Flächeneinheit, doch die Leistungs- und Leistungssteigerungen ließen allmählich nach. Da unsere Erwartungen an Innovationen nicht nachgelassen haben, sind Fortschritte in der Hardware-Architektur wichtiger geworden, um die Lücke zu schließen.

Treiber zur Erhöhung der Kernanzahl

Ein früher Schritt in diese Richtung nutzte Multi-Core-CPUs, um den Gesamtdurchsatz durch Threading oder Virtualisierung einer Mischung gleichzeitiger Aufgaben über mehrere Kerne hinweg zu beschleunigen und den Stromverbrauch nach Bedarf durch Leerlauf oder Herunterfahren inaktiver Kerne zu reduzieren. Multi-Core ist heute Standard und ein Trend zu Many-Core (noch mehr CPUs auf einem Chip) ist bereits bei Serverinstanzoptionen erkennbar, die auf Cloud-Plattformen von AWS, Azure, Alibaba und anderen verfügbar sind.

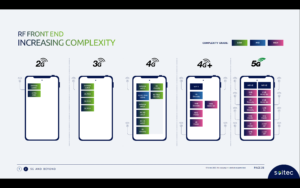

Multi-/Many-Core-Architekturen sind ein Fortschritt, aber die Parallelität durch CPU-Cluster ist grobkörnig und hat dank des Amdahl-Gesetzes ihre eigenen Leistungs- und Leistungsgrenzen. Die Architekturen wurden heterogener und es kamen Beschleuniger für Bild, Audio und andere spezielle Anforderungen hinzu. KI-Beschleuniger haben auch die feinkörnige Parallelität vorangetrieben und sind auf systolische Arrays und andere domänenspezifische Techniken umgestiegen. Das funktionierte ziemlich gut, bis ChatGPT mit 175 Milliarden Parametern erschien und sich GPT-3 zu GPT-4 mit 100 Billionen Parametern weiterentwickelte – Größenordnungen komplexer als heutige KI-Systeme –, was noch speziellere Beschleunigungsfunktionen innerhalb von KI-Beschleunigern erzwang.

An einer anderen Front werden Multisensorsysteme in Automobilanwendungen jetzt in einzelne SoCs integriert, um das Umweltbewusstsein und die PPA zu verbessern. Hier hängen neue Ebenen der Autonomie im Automobilbereich von der Zusammenführung der Eingaben mehrerer Sensortypen in einem einzigen Gerät in Subsystemen ab, die sich um das Zweifache, das Vierfache oder das Achtfache replizieren.

Laut Michał Siwinski (CMO bei Arteris) deuten Stichproben aus mehr als einem Monat Gesprächen mit mehreren Designteams über ein breites Anwendungsspektrum darauf hin, dass diese Teams aktiv auf eine höhere Kernanzahl zurückgreifen, um Leistungs-, Leistungs- und Leistungsziele zu erreichen. Er sagt mir, dass sie auch eine Beschleunigung dieses Trends sehen. Prozessfortschritte helfen immer noch bei der Anzahl der SoC-Gates, aber die Verantwortung für die Erfüllung der Leistungs- und Leistungsziele liegt nun fest in den Händen der Architekten.

Mehr Kerne, mehr Verbindungen

Mehr Kerne auf einem Chip bedeuten mehr Datenverbindungen zwischen diesen Kernen. Innerhalb eines Beschleunigers zwischen benachbarten Verarbeitungselementen, zum lokalen Cache, zu Beschleunigern für Sparse-Matrix und andere spezielle Verarbeitung. Fügen Sie hierarchische Konnektivität zwischen Beschleunigerkacheln und Bussen auf Systemebene hinzu. Fügen Sie Konnektivität für On-Chip-Gewichtsspeicherung, Dekomprimierung, Broadcast, Erfassung und Neukomprimierung hinzu. Fügen Sie HBM-Konnektivität für den Arbeitscache hinzu. Fügen Sie bei Bedarf eine Fusionsmaschine hinzu.

Der CPU-basierte Steuerungscluster muss mit jedem dieser replizierten Subsysteme und allen üblichen Funktionen verbunden sein – Codecs, Speicherverwaltung, Sicherheitsinsel und Root of Trust (falls zutreffend), UCIe bei einer Multi-Chiplet-Implementierung, PCIe für E/A mit hoher Bandbreite und Ethernet oder Glasfaser für die Vernetzung.

Das sind viele Zusammenhänge mit direkten Konsequenzen für die Marktfähigkeit der Produkte. Bei Prozessen unter 16 nm trägt die NoC-Infrastruktur mittlerweile 10–12 % zur Fläche bei. Noch wichtiger ist, dass es als Kommunikationsautobahn zwischen Kernen erhebliche Auswirkungen auf Leistung und Leistung haben kann. Es besteht die reale Gefahr, dass eine suboptimale Implementierung die erwartete Architekturleistung und Leistungsgewinne zunichte macht oder, noch schlimmer, dazu führt, dass zahlreiche Redesign-Schleifen konvergieren. Dennoch hängt die Suche nach einer guten Implementierung in einem komplexen SoC-Grundriss immer noch von langsamen Trial-and-Error-Optimierungen in bereits engen Designzeitplänen ab. Wir müssen den Sprung zum physikalisch bewussten NoC-Design wagen, um die volle Leistung und Leistungsunterstützung durch komplexe NoC-Hierarchien zu gewährleisten, und wir müssen diese Optimierungen schneller durchführen.

Physikalisch bewusste NoC-Designs halten Moores Gesetz auf Kurs

Das Mooresche Gesetz ist vielleicht nicht tot, aber Fortschritte in Leistung und Leistung sind heute eher auf die Architektur und die NoC-Verbindung als auf den Prozess zurückzuführen. Die Architektur treibt mehr Beschleunigerkerne, mehr Beschleuniger innerhalb von Beschleunigern und mehr Subsystemreplikation auf dem Chip voran. Alle erhöhen die Komplexität der On-Chip-Verbindung. Da die Anzahl der Kerne bei Designs zunimmt und auf Prozessgeometrien bei 16 nm und darunter umgestellt wird, können die zahlreichen NoC-Verbindungen, die das SoC und seine Subsysteme überspannen, das volle Potenzial dieser komplexen Designs nur dann unterstützen, wenn sie optimal unter Berücksichtigung physischer und zeitlicher Einschränkungen implementiert werden – durch ein physisch bewusstes Netzwerk On-Chip-Design.

Wenn Sie sich auch über diese Trends Sorgen machen, möchten Sie vielleicht mehr über die Arteris FlexNoC 5 IP-Technologie erfahren KLICKEN SIE HIER.

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- Platoblockkette. Web3-Metaverse-Intelligenz. Wissen verstärkt. Hier zugreifen.

- Quelle: https://semiwiki.com/artificial-intelligence/326727-interconnect-under-the-spotlight-as-core-counts-accelerate/

- :Ist

- $UP

- 100

- a

- Über uns

- beschleunigen

- beschleunigend

- Beschleunigung

- Beschleuniger

- Beschleuniger

- über

- aktiv

- advanced

- Vorschüsse

- gegen

- AI

- KI-Systeme

- Alibaba

- Alle

- Zulassen

- bereits

- und

- erschienen

- Anwendungen

- angemessen

- Architektur

- SIND

- Bereich

- AS

- At

- Audio-

- Automobilindustrie

- verfügbar

- Bewusstsein

- AWS

- Azure

- Bandbreite

- BE

- werden

- unten

- zwischen

- Milliarde

- Sendung

- Busse

- by

- Cache-Speicher

- CAN

- fähig

- ChatGPT

- Chip

- Cloud

- Cluster

- Business Development

- wie die

- Kommunikation

- Komplex

- Komplexität

- Berechnen

- Wettbewerber

- Vernetz Dich

- Verbindungen

- Konnektivität

- Folgen

- Einschränkungen

- weiter

- Smartgeräte App

- konvergieren

- Kernbereich

- CPU

- ACHTUNG

- technische Daten

- tot

- Übergeben

- geliefert

- hängt

- Design

- Designs

- Gerät

- anders

- Direkt

- Richtung

- Diskussionen

- nach unten

- Nachteile

- jeder

- Früh

- Elemente

- Motor

- Arbeitsumfeld

- Sogar

- Jedes

- Evolution

- sich entwickelnden

- Erweitern Sie die Funktionalität der

- Erwartungen

- erwartet

- beschleunigt

- Eigenschaften

- Suche nach

- fest

- Aussichten für

- vorwärts

- Frei

- für

- Materials des

- voller

- Funktionen

- Verschmelzung

- Gewinne

- Ziele

- gut

- Garantie

- Handling

- Hände

- Hardware

- Haben

- Hilfe

- hier

- High

- höher

- Autobahn

- HTTPS

- Image

- Impact der HXNUMXO Observatorien

- Implementierung

- umgesetzt

- wichtig

- verbessert

- in

- inaktiv

- Erhöhung

- zunehmend

- Infrastruktur

- Innovation

- Instanz

- Integration

- IP

- Insel

- IT

- SEINE

- springen

- Recht

- LERNEN

- Niveau

- Cholesterinspiegel

- Grenzen

- aus einer regionalen

- Los

- um

- Management

- März

- Matrix

- max-width

- Triff

- Treffen

- Memory

- Metrik

- könnte

- Monat

- mehr

- schlauer bewegen

- ziehen um

- mehrere

- Need

- erforderlich

- Bedürfnisse

- Netzwerk

- Vernetzung

- Neu

- und viele

- of

- on

- Optionen

- Bestellungen

- Andere

- Anders

- besitzen

- Parameter

- Leistung

- physikalisch

- Physisch

- Plattformen

- Plato

- Datenintelligenz von Plato

- PlatoData

- Post

- Potenzial

- Werkzeuge

- Powering

- ziemlich

- Prozessdefinierung

- anpassen

- Verarbeitung

- Produkt

- rein

- geschoben

- Schieben

- Angebot

- lieber

- echt

- Reduzierung

- repliziert

- Replikation

- Verantwortung

- Folge

- Biken

- Wurzel

- Sicherheit

- Halbleiter

- signifikant

- da

- Single

- locker

- langsam

- kleinere

- So

- Software

- spärliche Matrix

- spezialisiert

- Scheinwerfer

- Standard

- begonnen

- Schritt

- Immer noch

- Stoppen

- Lagerung

- Schlägt vor

- Support

- System

- Systeme und Techniken

- und Aufgaben

- Teams

- Techniken

- Technologie

- erzählt

- zur Verbesserung der Gesundheitsgerechtigkeit

- Das

- Diese

- Durch

- Durchsatz

- zeitliche Koordinierung

- zu

- heute

- heutigen

- Gesamt

- Trend

- Trends

- Billion

- Vertrauen

- Drehung

- Typen

- für

- Einheit

- Gewicht

- GUT

- welche

- breit

- Große Auswahl

- werden wir

- Gewinnt

- mit

- .

- arbeiten,

- Jahr

- Jahr

- Zephyrnet