Chiplets beginnen sich auf das Chip-Design auszuwirken, auch wenn sie noch nicht zum Mainstream gehören und es keinen kommerziellen Markt für diese Art von gehärtetem geistigem Eigentum gibt.

Es gibt laufende Diskussionen über das Silizium-Lebenszyklusmanagement, die beste Möglichkeit zur Charakterisierung und Verbindung dieser Geräte und den Umgang mit Problemen wie ungleichmäßiger Alterung und thermischer Fehlanpassung. Darüber hinaus werden große Anstrengungen unternommen, um die Beobachtbarkeit zu verbessern Chiplets Dies ist besonders wichtig, da diese Geräte in sicherheits- und unternehmenskritischen Anwendungen eingesetzt werden.

All diese Probleme müssen gelöst werden, um eine breite Akzeptanz zu ermöglichen, und die Chipindustrie hat erkannt, dass die Verlangsamung des Mooreschen Gesetzes in Kombination mit festen Retikelgrößen Änderungen in der Art und Weise erfordern wird, wie Chips entworfen, hergestellt und verpackt werden. Es ist physikalisch unmöglich, alle für viele Anwendungen erforderlichen Funktionen in einem einzigen SoC unterzubringen, und das Ziel besteht nun darin, einen geordneten, vorhersehbaren und wiederholbaren Ansatz zur Disaggregation vieler dieser Komponenten zu finden. Theoretisch wird dies eine einfachere Anpassung von Geräten ermöglichen, die Markteinführung beschleunigen und eine teure Skalierung von Komponenten vermeiden, die dies nicht erfordern, wie etwa analoge Funktionen.

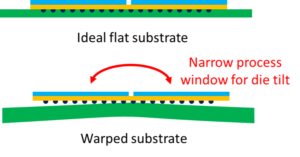

Um dieses Ziel zu erreichen, müssen jedoch einige komplexe und heikle Probleme gelöst werden. Zum einen wird es eine viel bessere Beobachtbarkeit, Überwachung und Analyse dessen erfordern, was in einem Paket enthalten ist. Das Konzept, mehrere Chips in einem Gehäuse unterzubringen, reicht bis in die 1990er Jahre zurück Multi-Chip-ModuleBei Chiplets sind die Dies normalerweise kleiner und dünner, und die Dynamik, wie sie charakterisiert, getestet und beobachtet werden, hat sich erheblich verändert.

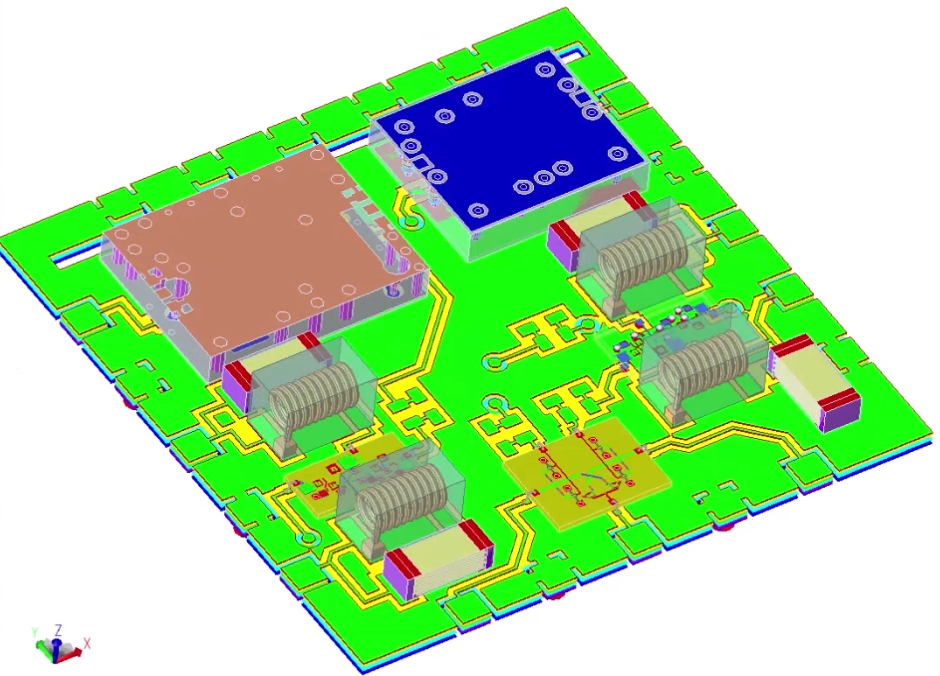

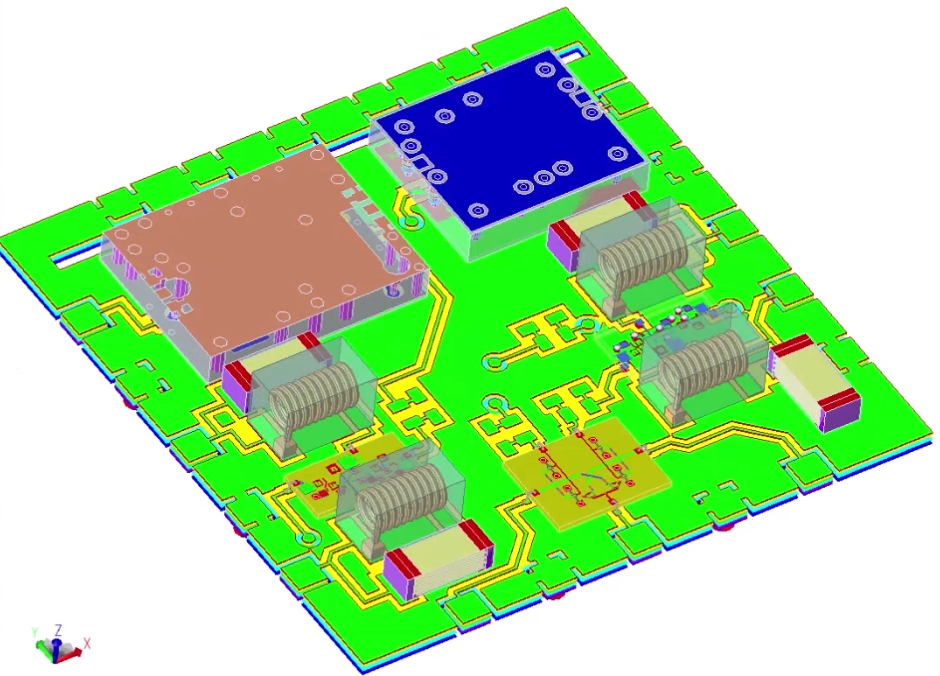

„In der Vergangenheit haben wir diese Multi-Chip-Module genannt, die heute in der drahtlosen Welt sehr beliebt sind“, sagte Nilesh Kamdar, Leiter des HF-/Mikrowellen-Portfolios bei Keysight. „Man nimmt ein beliebiges Smartphone in die Hand und der drahtlose Teil des Smartphones ist ein Front-End-Modul, das aus 20 bis 30 zusammengedrückten Chips auf kleinem Raum besteht, der kleiner als ein Fingernagel ist. Das passiert in der Branche schon seit mindestens einem Jahrzehnt, wenn nicht sogar länger. Auch mehrere Luft- und Raumfahrtprobleme sowie andere Hochfrequenzprobleme erforderten diese Art der Integration, weshalb wir dies in der Vergangenheit getan haben.“

Abb. 1. Multi-Chip-HF-Modullayout im PathWave ADS von Keysight. Quelle: Keysight

Der große Wandel, der jetzt im Gange ist, beinhaltet eine viel breitere Anwendung dieses Ansatzes sowie Verbesserungen im Chiplet-Design und Standardmethoden zum Anschließen, Testen und Messen dessen, was in den Chiplets selbst und im fortschrittlichen Gehäuse, das sie umgibt, geschieht.

„Die Automobilindustrie ist ein großartiges Beispiel dafür, was sich verändert“, sagte Kamdar. „Auf einer kürzlichen Konferenz sprach ein Vizepräsident eines großen OEM darüber, dass es nicht möglich sei, ein Rechenzentrum auf den Rücksitz eines Autos zu packen, denn das sei heute die Voraussetzung für ein autonomes Fahrzeug. Wenn Sie mehr Integration betreiben – und wenn Sie das Board irgendwie verschwinden lassen und alles zusammenquetschen – können wir das vielleicht vertikal auf den Rücksitz eines Autos quetschen. Es gibt viele ähnliche Anwendungsfälle. Der Strombedarf für Chiplets könnte geringer sein, wenn man physische Rechenzentren in Betracht zieht. Es gibt viele Vorteile, und das ist es, was Chiplets heute antreibt.“

Diese Änderungen sind jedoch täuschend komplex, und die Branche muss in dieser Hinsicht möglicherweise noch einmal zur Schule gehen. „Der Bau von Chiplets im großen Maßstab ist ein so anderes Modell, dass wir alle unsere Fähigkeiten neu bewerten müssen“, sagte er. „Wir müssen neu bewerten, wie Organisationen aufgebaut sind und wie Architektur funktioniert. Wir müssen die Rolle eines Systemdesigners neu bewerten. Möglicherweise haben sie die Dinge anders betrachtet und gesagt: „Ich bin Systemdesigner.“ Ich entwerfe die Spezifikationen für die Systeme. Ich zerlege es in kleinere Komponenten, einzelne ICs und verteile die Spezifikationen. Ich gehe weg und komme sechs Monate später zurück und schaue, wie es allen ergangen ist.“ Vielleicht ist das gar nicht möglich. Möglicherweise gibt es mehrere Systemdesigner, die entlang der Kette vorhanden sein müssen. Das sind die Art von Gesprächen, die stattfinden müssen. Bei den größten Playern der Branche finden diese Gespräche bereits statt, aber nicht überall.“

Die Anzahl potenzieller Interaktionen im Kontext eines Multi-Chiplet-Designs ist erheblich und in vielen Fällen designspezifisch. „Wenn Sie an Multi-Die glauben, wenn Sie an Chiplets glauben, müssen Sie glauben, dass dies das gesamte [Design- und Integrations-]Problem nur verschärfen wird“, sagte Shekhar Kapoor, Senior Director für Produktlinienmanagement bei Synopsys EDA-Gruppe. „Chiplets werden aus vielen Orten und aus vielen Quellen kommen. Es wird eine große Auswahl geben, viele Möglichkeiten für jeden. Das größte Problem sind die aktuellen Gepflogenheiten rund um all das. Große Unternehmen tun dies auf maßgeschneiderte und maßgeschneiderte Weise. Aber wenn man bei der Standardisierung weitreichend vorgeht, woher weiß man dann, dass ein Chiplet in die Umgebung, in das Produkt, das man bauen möchte, passt?“

Trotz der Fokussierung auf Standards wie UCIe und Bunch of Wires gibt es immer noch Nuancen hinsichtlich der Charakterisierung der einzelnen Chiplets im Kontext eines Systems. „Woher wissen Sie wirklich, welches Profil es hat? Hier wird noch mehr Überwachung ins Spiel kommen, was fast wie eine Signatur ist“, sagte Kapoor. „Sie können es lesen und wissen, ob es ideal für Ihre Umgebung ist. Angesichts der Tatsache, dass sich die Branche in Richtung einer stärkeren Chiplet-Aktivierung bewegt, wird dies eine zentrale Überlegung sein. Es werden mehr Anforderungen entstehen, mehr Standards werden entstehen, dann kann man sehen, ob etwas passt oder nicht.“

Es gibt auch andere Herausforderungen zu meistern.

„Bei Chiplets sind alle Hochgeschwindigkeitssignale im Gehäuse enthalten, daher ist die Beobachtbarkeit viel schwieriger“, sagte Sue Hung Fung, Produktlinien-Marketingmanagerin für UCIe bei Kadenz. „Dies kann durch Link-Fehlerprüfungen, Augenscans, BiST usw. erfolgen, um zu einem bekannt guten Chip (Known Good Die, KGD) zu gelangen. Darauf basieren alle Testmethoden. Darüber hinaus wäre es wertvoll, über gute Monitore für den Zustand der Verbindung zu verfügen, und es gibt neue und unterschiedliche Vorschläge von verschiedenen Anbietern.“

Der Schlüssel besteht darin, die Signalqualität im Kontext der übrigen Komponenten in einem Paket zu überwachen, was umso schwieriger wird, je mehr Funktionen in Chiplets aufgeteilt werden.

„Können wir deren Signale und Qualität während der Datenübertragung überwachen? Vor dem Missionsmodus werden Trainingstechniken durchgeführt, um die Robustheit der Datenübertragung zu verbessern“, bemerkte Hung Fung. „Eine erneute Schulung ist nicht erwünscht, da sie zu Datenunterbrechungen führen kann. Wir müssen in der Lage sein, jede Spur kontinuierlich zu überwachen und zu melden und alle Ereignisse zu erkennen, die zu Störungen führen könnten, bevor es zu einer Störung kommt. Die Verhinderung von Systemausfällen und die Reparatur dieser Ausfälle umfassen die Neuzuordnung von Redundanzspuren oder andere Reparaturmethoden, um geringfügig ausgefallene Spuren zu erkennen. Training und kontinuierliche Überwachung dieser internen Chiplet-Signale sind die Herausforderungen für die Analyse des Linkverhaltens.“

Arbeitsgruppen für UCIe versuchen, einen Teil dieser Beobachtbarkeit zu standardisieren, um ein offenes Link-Ökosystem zu schaffen. Aber auch das Hinzufügen von Beobachtbarkeit und Überwachung kann je nach vertikalem Segment stark variieren.

Randy Fish, Leiter des Produktlinienmanagements der Synopsys EDA Group, erklärte, dass fast alle Lösungen maßgeschneidert seien, da es keinen Standardansatz und nur wenige kommerzielle Anbieter für Observability-Lösungen gebe. „Wenn man in eines der führenden Halbfinals kommt, machen sie etwas“, sagte er. „Die Frage ist, ob es Funktionen rund um Multi-Chips gibt, die uns zur Standardisierung zwingen, um eine kohärente oder kohärente Infrastruktur für Überwachung und Fehlerbehebung zu haben – im Grunde genommen, um zu sehen, was vor sich geht, insbesondere wenn man mehrere Chips von mehreren Lieferanten erhält.“ Einige der Multi-Chip-Lösungen kommen in die Automobilindustrie und dort kümmern sie sich um Dinge wie Alterung und was mit diesen Chips passiert. Und wie wir wissen, handelt es sich um fortgeschrittene Knoten. Es ist nicht so, dass es sechs ausgereifte, zehn Jahre alte Technologien gibt. Dies sind fortgeschrittene Knoten, die keine lange Geschichte haben. Aus diesem Grund gibt es eine Reihe von Faktoren, die dies erzwingen.“

Chiplets bringen auch einige interessante Kontraste mit sich. Kamdar von Keysight bemerkte, dass einer der Diskussionsteilnehmer während einer kürzlichen CEO-Runde sagte, dass Chiplets eine einzigartige Dichotomie hätten. „Einerseits könnte jedes Chiplet ein unabhängiges IP sein, das Sie von einem IP-Anbieter beziehen und relativ kostengünstig und relativ einfach in Ihr System integrieren können. Der gesamte Stapel, den Sie aufbauen möchten, zwingt Sie jedoch plötzlich dazu, alles zu wissen. Früher hätte man einfach sagen können: „Ich brauche sechs Dinge.“ Ich kaufe fünf Stück von der Stange bei einem IP-Anbieter und sie werden herausfinden, was sie brauchen. Ich werde mich auf eines konzentrieren.‘ Aber jetzt gelingt Ihnen das vielleicht nicht mehr. Möglicherweise müssen Sie tatsächlich wissen, wie alle sechs Schritte ausgeführt werden, und herausfinden, wie das alles geschieht, da die Komplexität des Problems gerade zugenommen hat. Dies könnte die Branche dazu zwingen, dies zunächst nur den Großen zu überlassen. Es kann viel länger dauern, bis die kleineren Anbieter in diesem Umfeld erfolgreich sein können.“

Dennoch bedarf es mehr als eines Unternehmens, um die Chiplet-Integration und -Einführung zu beschleunigen.

„Keysight nahm am TSMC-Symposium teil, bei dem es sich um eine eher öffentliche Veranstaltung handelt, und im Anschluss gab es einen Workshop nur mit den Partnern, die Teil der 3D Fabric Alliance sind“, sagte Kamdar. „TSMC begann und endete den ganzen Tag damit, darüber zu sprechen, wie wir alle gemeinsam daran arbeiten müssen, was von anderen Teilnehmern, darunter AMD und Qualcomm, bestätigt wurde. Sprecher beider Unternehmen sagten, kein einziges EDA-Unternehmen wisse, wie man das Chiplet-Problem allein lösen könne. Die gesamte Branche muss zusammenarbeiten.“

Technische Herausforderungen

Ein weiteres wichtiges Anliegen bei Chiplets ist die Wärmeableitung. Dies ist Teil der Charakterisierung, hängt aber auch stark von Anwendungsfällen, Verpackungsoptionen und der gesamten System-in-Package-Architektur ab.

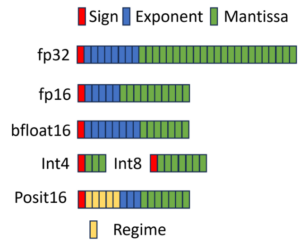

„Bei Chiplets ist die Marginalität im Design bei optimalem PPA (mit Ausrichtung auf aggressives PJ/Bit und Beachfront-Dichte) gering, was bei der Entwicklung von Chiplet-PHYs von entscheidender Bedeutung ist“, sagte Rishi Chugh, Vizepräsident für Produktmarketing der IP Group bei Cadence. „Zuverlässigkeit ist der Schlüssel, ebenso wie die Beobachtbarkeit, um die KGD zu überprüfen und sie zu kommerziellem Betriebserfolg zu führen. Datenintegritätsschemata wie CRC (Cyclic Redundancy Check), Augenscan, BiST und Überwachungsschaltkreise sind im Design für Robustheit implementiert, und das Design muss mit Fehlermechanismen überversorgt sein, um sicherzustellen, dass die Datenleitung belastbar ist.“

Ein ganzes Kapitel innerhalb des UCIe-Protokolls ist der Initialisierung und dem Training im Zusammenhang mit dem UCIe-Protokoll gewidmet, das den Beobachtbarkeitsaspekt des Protokolls abdeckt, fügte Chugh hinzu.

Darüber hinaus gibt es Debatten darüber, ob die eigentlichen Grundlagen des Hinzufügens von Beobachtbarkeit zu einem System der schwierigste Teil sind oder ob die Änderung des Denkens rund um diese Konzepte schwieriger ist.

„Im Gegensatz zu anderen Dingen ist es eigentlich gar nicht so kompliziert, weil es ‚nur‘ ein weiterer Block ist, mit dem man sich verbinden kann. Es gibt Beobachtungen und wir haben die Möglichkeit, Dinge zu verfolgen“, sagte Frank Schirrmeister, Vice President Solutions and Business Development bei Arteris-IP. „Benutzer fordern bereits Dinge wie die Betrachtung der Register aus einer Softwareperspektive. Die Herausforderung besteht nun darin, diese Register im NoC verfügbar zu machen. Aus NoC-Sicht gibt es die Protokolle selbst wie CHI, ACE, AMBA, OCP oder andere, und das sind die Mechanismen der Sprache – wie sie sprechen und wie sie interagieren. Innerhalb des NoC passieren bei den komplexeren Protokollen Dinge über mehrere Zyklen hinweg, man muss also auf Antworten warten und Dinge in die Pipeline bringen.“

Dies ähnelt der spekulativen Ausführung in Prozessoren. „Wir reden über diese Gutschriften, wie lange muss ich auf eine Antwort warten und so weiter“, erklärte Schirrmeister. „Das sind alles Teile der Protokolle. Im NoC müssen Sie Fragen wie die Tiefe der Puffer verstehen. Wann warte ich eigentlich auf Daten? Es ist teilweise Leistung. Anschließend können Sie zur Beobachtbarkeit eine Verbindung zu den Daten herstellen, und die Sensoren nutzen möglicherweise ihr eigenes Netzwerk, je nachdem, wie Sie es konfigurieren möchten. Bei On-Chip-Monitoren müssen Sie entscheiden, ob Sie diese beispielsweise auf einen speziellen Observability-Bus legen. Es gibt immer eine Diskussion darüber, wie viel Debug ich eigentlich habe? Letzten Endes handelt es sich „nur“ um eine weitere Verbindung dieser Komponenten, und Sie müssen entscheiden, wie Sie sie aus dem Chip exportieren möchten usw. Wie viel Sie auf dem Chip speichern, hängt davon ab, wie viel Siliziumfläche ich dafür auszugeben bereit bin?“

Das ist besonders wichtig, wenn man Chiplets zusammenfügt. „Wie stelle ich sicher, dass ich genügend Platz für diese Recheneinheit habe, die nur wie Daten aussieht und der unmittelbaren Funktion eigentlich keinen Mehrwert verleiht?“ fragt Gajinder Panesar, Chefarchitekt bei Picocom. „Außerdem bin ich vielleicht kein Überwachungsexperte, aber ich weiß, dass ich es brauche. Ich brauche also etwas, das sagt: „Drücken Sie einfach diesen Knopf.“ Sie haben eine Umgebung, wir gestalten sie und „dies“ passiert. Im Idealfall sollten wir das Verhalten der CPU-Leistung beobachten und dann bestimmte Aspekte des Kerns dynamisch optimieren, um eine bessere Leistung zu erzielen.“

Eines der Dinge, die noch entwickelt werden müssen, ist die dynamische Steuerung der Geräte und die Anpassungen, die im Laufe ihrer Lebensdauer vorgenommen werden können.

„Sagen wir, wir haben alle Möglichkeiten, alles im Voraus zu modellieren“, sagte Lee Harrison, Direktor für Produktmarketing bei der Tessent-Gruppe bei Siemens Digital Industries Software. „Wir haben alle Monitore eingebaut, um die systeminternen Aufgaben zu erledigen, aber das schließt den Kreis. Bei den neueren Geometrien gibt es noch einiges zu lernen, um wirklich zu optimieren, wie wir die verschiedenen Parameter des Geräts optimieren können, um diese Zuverlässigkeit zu erhöhen. Das Stück, das diesen Kreis zum Lebenssystem schließt, ist ein enormer Wert. Dennoch gibt es noch viel zu tun.

Verantwortungsrollen ändern

Kommerzielle Chiplets stellen ein weiteres heikles Problem dar: Wer ist verantwortlich, wenn etwas Unerwartetes beobachtet wird oder schief geht?

„Wenn ich ein Chiphersteller bin, mache ich den Chip und durchlaufe möglicherweise einen OSAT zum Testen“, sagte Paul Karazuba, Vizepräsident für Marketing bei Expedera. „Ich nutze ASE vielleicht als Verpackungsunternehmen, aber ich verkaufe es unter meinem Namen und meiner Garantie. Interessant wird es, wenn wir Chiplets haben. Bei all unseren Besprechungen zum Thema Chiplets wird immer die Frage aufgeworfen, wer wofür verantwortlich sein wird. Nehmen wir an, ich sollte einen KI-Chiplet herstellen und ihn in ein System verkaufen und mit den Chiplets von sechs anderen Unternehmen verpacken. Welches Unternehmen übernimmt die Garantie? Welches Unternehmen wird den Service dafür durchführen? Es gibt derzeit keinen wirklichen Konsens.“

Die Arbeitsidee sei, dass das Unternehmen verantwortlich sei, dessen Name auf der Außenseite des Pakets steht, sagte Karazuba. „Dieses Unternehmen wird wahrscheinlich dasjenige sein, das letztendlich die Verantwortung für den Service für seine Kunden trägt, aber es bringt eine weitere Serviceebene mit sich, die Chiplet-Hersteller bereitstellen müssen, und das wird interessant sein.“ Die Angst besteht darin, dass um das Jahr 2000 das Intel-Microsoft-Dell-Dreieck entstand, in dem alle mit dem Finger aufeinander zeigten. Das ist derzeit eine unausgesprochene Angst in der Branche.“

Und vielleicht ist es nicht eines der Chiplets. Was passiert, wenn ein Substrat oder eine physische Verbindung defekt ist?

„Aus Testsicht kann ein Chiplet völlig einwandfrei funktionieren“, sagte Karazuba. „Aber wie versteht der Chiplet-Hersteller im Vergleich zum Hersteller von Multichip-Modulen, wenn es ein physisches Verbindungsproblem gibt? Es wird interessant sein. Der einzige Weg, diese Probleme zu lösen, wird Versuch und Irrtum sein. Als Halbleiterhersteller können wir so viele rechtliche Verträge entwerfen, wie wir wollen, aber wir befinden uns hier in Neuland und müssen die Dinge anpassen. Die Supportmodelle müssen angepasst werden, um der neuen Realität Rechnung zu tragen, dass monolithisches Silizium kein primäres Vehikel für den Halbleiterverkauf ist.“

Kapoor von Synopsys hat bereits Auswirkungen auf das Ökosystem. „Ökosysteme hat es schon immer gegeben, aber Ihr aktives Ökosystem, wo auch immer Sie sich befinden, war vielleicht der nächste Kreis darum herum. Wenn Sie sich mit Design befassen, kümmern Sie sich nur um die Designregeln der Gießerei und das Designregelhandbuch. Das ändert sich, wenn man über die Chiplets spricht. Auch beim Design denken Sie jetzt noch mehr über Tests nach als je zuvor. Du sprichst mit Vorteilhafteste machen Teradyne. Auch wenn Sie nur ein Designer sind, müssen Sie herausfinden, was Sie aus ATPG-Sicht einbauen müssen und wie es getestet werden soll. Die relevante Ökosystemgröße nimmt zu.“

Dennoch bleibt der Branche keine andere Wahl, als diese Probleme zu lösen. „Wir haben über den Chiplet-Markt gesprochen. Sie können einen Würfel herausziehen und ihn bereithalten. Davon sind wir noch weit entfernt, aber die Schritte werden immer klarer, was wir erreichen müssen. Konnektivität ist von grundlegender Bedeutung. UCIe-Standards sind ein Muss, und damit einhergehend sind die Protokolle und Regeln aus Konnektivitätssicht, die Sie festlegen müssen. Als nächstes kämen sehr klar definierte Modelle. Die Herausforderungen, über die wir sprechen, werden insbesondere von der Thermik und der Leistung beeinflusst. Dafür gibt es bereits einige Standards, und wir werden von der Konnektivität zum charakterisierten Modell übergehen, damit wir es zuverlässiger nutzen können. Dann brauchen wir eine Art Signatur, anhand derer wir unter dem Gesichtspunkt der Testbarkeit sehen können, wie sich die Lebensdauer und die Art und Weise, wie sich alle sterben, unterschiedlich verändern werden.“

Die Eingaben hierfür werden von Chip- und Systemmonitoren kommen, die ebenfalls auf Standards basieren müssen.

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoAiStream. Web3-Datenintelligenz. Wissen verstärkt. Hier zugreifen.

- Die Zukunft prägen mit Adryenn Ashley. Hier zugreifen.

- Kaufen und verkaufen Sie Anteile an PRE-IPO-Unternehmen mit PREIPO®. Hier zugreifen.

- Quelle: https://semiengineering.com/chiplet-planning-kicks-into-high-gear/

- :hast

- :Ist

- :nicht

- :Wo

- $UP

- 1

- 20

- 30

- 3d

- a

- Fähigkeit

- Fähig

- Über uns

- beschleunigen

- Erreichen

- aktiv

- präsentieren

- berührt das Schneidwerkzeug

- hinzufügen

- hinzugefügt

- Hinzufügen

- Zusatz

- Bereinigt

- Anpassungen

- Adoption

- Siehe Werbung

- advanced

- Luft- und Raumfahrt

- aggressiv

- Hautalterung

- AI

- Alle

- Allianz

- erlauben

- bereits

- ebenfalls

- immer

- am

- AMD

- Betrag

- an

- Analyse

- Analyse

- machen

- Ein anderer

- jedem

- Anwendung

- Anwendungen

- Ansatz

- Architektur

- SIND

- um

- AS

- Aussehen

- Aspekte

- damit verbundenen

- At

- Automobilindustrie

- Autonom

- autonomes Fahrzeug

- verfügbar

- vermeiden

- ein Weg

- Zurück

- basierend

- Grundsätzlich gilt

- BE

- weil

- wird

- Werden

- war

- Bevor

- Anfang

- Sein

- Glauben

- Vorteile

- BESTE

- Besser

- Big

- Größte

- Bit

- Blockieren

- Tafel

- beide

- Break

- Brings

- breit

- breiteres

- bauen

- erbaut

- Haufen

- Bus

- Geschäft

- Geschäftsentwicklung

- aber

- Taste im nun erscheinenden Bestätigungsfenster nun wieder los.

- Kaufe

- by

- Kadenz

- namens

- CAN

- Fähigkeiten

- Auto

- österreichische Unternehmen

- Häuser

- Fälle

- Verursachen

- Center

- Centers

- CEO

- sicher

- Kette

- challenges

- Herausforderungen

- herausfordernd

- Übernehmen

- geändert

- Änderungen

- Ändern

- Kapitel

- charakterisieren

- dadurch gekennzeichnet

- aus der Ferne überprüfen

- Schecks

- Chef

- Chip

- Pommes frites

- Wahl

- Entscheidungen

- Kreis

- klarer

- Schließt

- Schließen

- KOHÄRENT

- zusammenhängend

- kombiniert

- wie die

- kommt

- Kommen

- kommerziell

- Unternehmen

- Unternehmen

- Komplex

- Komplexität

- kompliziert

- Komponenten

- konzept

- Konzepte

- Hautpflegeprobleme

- betroffen

- Konferenz

- Vernetz Dich

- Sie

- Konnektivität

- Konsens

- Geht davon

- Berücksichtigung

- Kontext

- kontinuierlich

- ständig

- Verträge

- Kontrast

- Kontraste

- Smartgeräte App

- Gespräche

- Kernbereich

- Kosten

- könnte

- deckt

- CPU

- CRC

- Credits

- wichtig

- Strom

- Kunden

- maßgeschneiderte

- Zyklen

- technische Daten

- Data Center

- Rechenzentren

- Datum

- Tag

- Deal

- Debatten.

- Jahrzehnte

- entscheidet

- gewidmet

- tief

- definiert

- Dichte

- abhängig

- Abhängig

- Design

- entworfen

- Designer

- Designer

- Entwerfen

- erwünscht

- entwickelt

- Entwicklung

- Gerät

- Geräte

- DID

- Sterben

- anders

- schwer

- digital

- Direktor

- verschwinden

- Diskussion

- Diskussionen

- verteilen

- do

- die

- Dabei

- erledigt

- Nicht

- nach unten

- Fahren

- im

- dynamisch

- dynamisch

- Dynamik

- jeder

- leicht

- Ökosystem

- Ecosystems

- Anstrengung

- entstehen

- ermöglichen

- Aktivierung

- Ende

- genug

- gewährleisten

- Ganz

- Einheit

- Arbeitsumfeld

- Fehler

- insbesondere

- etablieren

- Sommer

- etc

- Sogar

- Event

- Veranstaltungen

- ÜBERHAUPT

- jedermann

- alles

- Beispiel

- Ausführung

- existieren

- existiert

- teuer

- Experte

- erklärt

- exportieren

- erweitern

- Auge

- Stoff

- Faktoren

- andernfalls

- Scheitern

- weit

- Fashion

- Angst

- wenige

- Feige

- Abbildung

- Fische

- passen

- fixiert

- Setzen Sie mit Achtsamkeit

- Aussichten für

- Zwingen

- Streitkräfte

- weiter

- Giesserei

- für

- Materials des

- Funktion

- Funktionen

- fundamental

- Grundlagen

- Ausrüstung

- bekommen

- bekommen

- gegeben

- Go

- Kundenziele

- Goes

- gehen

- gut

- groß

- sehr

- Gruppe an

- Gruppen

- Pflege

- passieren

- Los

- das passiert

- Haben

- mit

- he

- Gesundheit

- hier

- GUTE

- Hochfrequenz

- hoch

- Geschichte

- Häuser

- Ultraschall

- Hilfe

- aber

- HTTPS

- riesig

- i

- ICS

- Idee

- ideal

- if

- unmittelbar

- Impact der HXNUMXO Observatorien

- wirkt

- umgesetzt

- wichtig

- unmöglich

- zu unterstützen,

- Verbesserungen

- in

- Dazu gehören

- Einschließlich

- zunehmend

- unabhängig

- Krankengymnastik

- Branchen

- Energiegewinnung

- Infrastruktur

- anfänglich

- Eingänge

- integrieren

- Integration

- Integrität

- interagieren

- Interaktionen

- interessant

- intern

- in

- einführen

- IP

- Problem

- Probleme

- IT

- SEINE

- nur

- Kapoor

- Wesentliche

- Kicks

- Art

- Wissen

- bekannt

- Spur

- Sprache

- grosse

- später

- Recht

- Schicht

- Layout

- führen

- führenden

- lernen

- am wenigsten

- Lee

- Rechtlich

- Niveau

- Lebenszyklus

- Lebensdauer

- Lebensdauer

- Gefällt mir

- Line

- LINK

- Lang

- länger

- suchen

- Los

- Sneaker

- gemacht

- Mainstream

- Dur

- um

- Hersteller

- Makers

- Making

- Management

- Manager

- manuell

- hergestellt

- viele

- Markt

- Marketing

- Marktplatz

- reifen

- max-width

- Kann..

- messen

- Mechanismen

- Tagungen

- Methoden

- könnte

- Ziel

- Model

- Modell

- für

- Modulen

- Module

- Überwachen

- Überwachung

- Monitore

- Monolithisch

- Monat

- mehr

- ziehen um

- viel

- mehrere

- sollen

- my

- Name

- Need

- Bedürfnisse

- Netzwerk

- Neu

- weiter

- nicht

- Fiber Node

- bekannt

- jetzt an

- Anzahl

- beobachten

- of

- WOW!

- on

- EINEM

- laufend

- einzige

- XNUMXh geöffnet

- Betriebs-

- optimal

- Optimieren

- Optionen

- or

- Auftrag

- Organisationen

- Andere

- Andere Teilnehmer

- Anders

- UNSERE

- aussen

- übrig

- Gesamt-

- Überwinden

- besitzen

- Paket

- verpackt

- Verpackung

- Tafel

- Parameter

- Teil

- Teilnehmer

- besondere

- besonders

- Teile

- passt

- Alexander

- Leistung

- Perspektive

- physikalisch

- Physisch

- wählen

- ein Bild

- Stück

- Stücke

- Pipeline

- Länder/Regionen

- Planung

- Plato

- Datenintelligenz von Plato

- PlatoData

- Points

- Perspektive

- Beliebt

- Mappe

- möglich

- Potenzial

- Werkzeuge

- Vorhersagbar

- Präsident

- Presse

- abwehr

- vorher

- primär

- Vor

- wahrscheinlich

- Aufgabenstellung:

- Probleme

- Prozessoren

- Produkt

- Profil

- Vorschläge

- Protokoll

- Protokolle

- die

- Öffentlichkeit

- setzen

- Putting

- Qualcomm

- Qualität

- Frage

- geschafft

- Lesen Sie mehr

- bereit

- echt

- Immobilien

- Realität

- wirklich

- Grund

- kürzlich

- anerkannt

- reflektieren

- Reflexionen

- registriert

- verhältnismäßig

- relevant

- Zuverlässigkeit

- Knorpel zu reparieren,

- wiederholbar

- berichten

- erfordern

- falls angefordert

- Voraussetzungen:

- federnde

- Antwort

- Antworten

- Verantwortung

- für ihren Verlust verantwortlich.

- REST

- Recht

- Robustheit

- Rollen

- Regel

- Ohne eine erfahrene Medienplanung zur Festlegung von Regeln und Strategien beschleunigt der programmatische Medieneinkauf einfach die Rate der verschwenderischen Ausgaben.

- Said

- Salz

- sagen

- sagt

- Skalieren

- Skalierung

- Scan

- Regelungen

- Schule

- Bildschirm

- sehen

- gesehen

- Segment

- verkaufen

- in XNUMX Minuten

- Halbleiter

- Senior

- Sensoren

- kompensieren

- mehrere

- Regal

- verschieben

- sollte

- gezeigt

- Seite

- Signal

- Signale

- signifikant

- bedeutend

- Silizium

- ähnlich

- Single

- SIX

- Halbjahr

- Größe

- Größen

- Fähigkeiten

- Verlangsamung

- klein

- kleinere

- Smartphone

- So

- Software

- Lösungen

- LÖSEN

- Auflösung

- einige

- etwas

- Quelle

- Quellen

- Raumfahrt

- Lautsprecher

- besondere

- Spezifikation

- spekulativ

- Geschwindigkeit

- verbringen

- Squeeze

- Stapel

- Standard

- Normen

- begonnen

- Shritte

- Immer noch

- speichern

- Erfolg

- erfolgreich

- so

- verklagen

- Lieferanten

- Support

- Symposium

- System

- Systeme und Techniken

- Nehmen

- nimmt

- Reden

- sprechen

- Targeting

- Techniken

- Technologies

- AGB

- Test

- Testen

- als

- zur Verbesserung der Gesundheitsgerechtigkeit

- Das

- ihr

- Sie

- sich

- dann

- Theorie

- Dort.

- Thermal-

- Diese

- vom Nutzer definierten

- Ding

- Denken

- fehlen uns die Worte.

- diejenigen

- obwohl?

- Durch

- Zeit

- zu

- heute

- gemeinsam

- gegenüber

- Spur

- Ausbildung

- privaten Transfer

- Versuch

- Versuch und Irrtum

- TSMC

- typisch

- verstehen

- Unterwegs

- Unerwartet

- einzigartiges

- us

- -

- benutzt

- wertvoll

- Wert

- verschiedene

- Fahrzeug

- Verkäufer

- Anbieter

- Gegen

- vertikal

- vertikal

- sehr

- Vizepräsident:in

- Anzeigen

- warten

- Warten

- wollen

- wurde

- Fluten

- Weg..

- Wege

- we

- GUT

- ging

- Was

- Was ist

- wann

- ob

- welche

- während

- WHO

- ganze

- deren

- weit verbreitet

- werden wir

- bereit

- kabellos

- mit

- .

- Arbeiten

- zusammenarbeiten

- arbeiten,

- Werkstatt

- weltweit wie ausgehandelt und gekauft ausgeführt wird.

- würde

- Falsch

- noch

- U

- Ihr

- Zephyrnet