RISC-V-Prozessoren, die bis vor einigen Jahren als Hilfsprozessoren für bestimmte Funktionen galten, scheinen Unterstützung für eine ganz andere Art von Rolle zu erhalten – High Performance Computing.

Dies befindet sich noch in der Diskussionsphase. Es bleiben Fragen zum Software-Ökosystem oder zur Zuverlässigkeit der Chips, Boards und Systeme. Und es gibt sowohl geschäftliche als auch technische Probleme, wobei die geschäftlichen Probleme am schwierigsten sind. Aber es spricht für die Dynamik der RISC-V Architektur, die aufgrund ihrer offenen ISA einen massiven Anstieg der Akzeptanz und des Experimentierens erlebt hat. Das wiederum gibt der Industrie die Freiheit, damit innovativ zu sein.

„Es ist nicht die ISA (Instruction Set Architecture) an sich, die so attraktiv ist“, sagte Rupert Baines, Chief Marketing Officer bei Codasip. „Es ist das, was man darum herum baut. Daher sind die Arbeitsgruppen rund um Sicherheit und die Veröffentlichung von Best Practices und Richtlinien und Referenzarchitekturen wichtig. Open Titan, die Open-Source-Wurzel des Vertrauens, ist wichtig, weil es sich um eine gut gemachte Referenzarchitektur handelt. Die Leute können es sich ansehen und das Rad nicht neu erfinden und vielleicht einen Fehler machen.“

Die große Frage ist nun, wie weit diese Architektur in neue Richtungen getrieben werden kann. Die Chipindustrie ist fest in die Ära der domänenspezifischen Datenverarbeitung eingetreten, in der Prozessoren hochgradig auf bestimmte Aufgaben zugeschnitten werden können und dann andere feste Architekturen für diese Aufgaben übertreffen. Aber das kann auch die Portierung von Software problematischer machen, wenn diese Software für diese benutzerdefinierten Kerne optimiert werden muss.

Für RISC-V könnten High Performance Computing und Supercomputing einen riesigen Sprung nach vorne darstellen. Ein Supercomputer ist definiert als ein Computer mit einem hohen Leistungsniveau im Vergleich zu einem Allzweckcomputer. Dies sind in der Regel Gleitkommamaschinen mit Vektorerweiterungen, und der aktuelle Marktführer, Frontier, kann mit etwa 1.1 exaFLOPs auf dem LINPACK-Benchmark arbeiten. Es verfügt über 8,730,112 Prozessorkerne basierend auf x86 ISA.

Dennoch hat sich der Bedarf an solchen Giganten weiterentwickelt, da andere Alternativen allgemein verfügbar werden. Früher war ein HPC ein kundenspezifischer Allzweckcomputer. Heute steht jedem, der Cluster von Hochgeschwindigkeitsservern bereitstellt, die entweder vor Ort oder in der Cloud gehostet werden, eine sehr ähnliche Funktion zur Verfügung.

Ob RISC-V hier ein mögliches Spiel hat, muss aus verschiedenen Blickwinkeln untersucht werden. Wer braucht einen Supercomputer auf Basis der RISC-V-Architektur und wer ist bereit, dafür zu bezahlen? Verfügen der RISC-V ISA und die Erweiterungen über alle notwendigen Fähigkeiten, um einen Supercomputer zu erstellen? Hat jemand einen Kern mit geeigneter Leistung erstellt? Ist die gesamte erforderliche Software vorhanden?

In Arms Fußstapfen treten

Bis vor kurzem basierten die meisten Supercomputer auf Intels x86-Architektur. Arm wollte seine Penetration in High Performance Computing verbessern und hatte die grundlegende Hardwareunterstützung um 2016 bereit.

„Als die ersten Arm-Supercomputer-Programme initiiert wurden, war Arm noch nicht bereit in dem Sinne, dass das gesamte Ökosystem vorhanden war oder dass alle Probleme gelöst worden waren“, sagt Rob Aitken, a Synopsys Gefährte. „Es war eher so, dass irgendjemand irgendwo gesagt hat, dass es nah genug ist, dass ich bereit bin, das Risiko einzugehen. Ich bin bereit, es zu versuchen. Ich würde sagen, dass RISC-V entweder an oder sehr nahe an dem Punkt ist, an dem jemand bereit sein wird, ein Risiko einzugehen und etwas für einen Supercomputer zu bauen.“

Am 22. Juni 2020 wurde der japanische Fugaku-Supercomputer, der von Fujitsus 48-Kern-A64FX-SoC angetrieben wird, der erste Arm-betriebene Supercomputer, der zumindest vorübergehend den Spitzenplatz als schnellster Computer der Welt einnahm. Eine Liste der leistungsstärksten Hochleistungsrechner finden Sie auf der TOP500 Liste.

Leistung ist nicht die einzige Überlegung. „Um ein erfolgreicher HPC-fähiger Prozessor zu sein, müssen Leistung, Effizienz und Sicherheit bereitgestellt und gleichzeitig ein Ökosystem von Anwendungen und wichtige führende Serverstandards unterstützt werden“, sagt David Lecomber, Senior Director of HPC and Tools für Waffen Geschäftsbereich Infrastruktur. „Wenn es um Designflexibilität geht, um dies zu erstellen, ist es wichtig, diese Flexibilität dort bereitzustellen, wo sie dem Entwickler am besten dient. Beispielsweise ist eine stabile und konsistente ISA für kommerzielle HPC-Entwickler von entscheidender Bedeutung, aber die Flexibilität, Speichersubsysteme Ihrer Wahl (DDR5, HBM, CXL-Attached) oder Beschleuniger (On-Die oder PCIe/CXL-Attached) zu entwerfen, ist leistungsstark .“

Was bedeutet am schnellsten?

Die Leistungsmetriken haben sich in den letzten Jahren für die Branche verändert. Während die absolute Leistung immer noch an erster Stelle steht, werden Systeme oft durch die Leistung eingeschränkt, und das führt zu Architekturen, die für bestimmte Aufgaben optimiert sind. Es wirft aber auch Fragen zur Leistungsmessung auf, denn wahrscheinlich ist keine Maschine bei jeder Aufgabe die Schnellste.

Seit Jahren verwendet die Branche den LINPACK-Benchmark, der jedoch zunehmend kontrovers diskutiert wird und keine einfache Antwort liefert. Ein Ansatz besteht darin, den Benchmark zu erweitern, und dies wird als HPC-Challenge-Benchmark-Suite bezeichnet. Einer der Urheber, Jack Dongarra, Professor für Informatik an der University of Tennessee (ausführlicher Lebenslauf ist hier), wurde von der US-Regierung beauftragt, daran zu arbeiten. Aber die Lösung eines Problems schafft ein anderes. Der Benchmark liefert keine einzige Zahl mehr, was Vergleiche erschwert.

Leistung ist aus anderen Gründen schwer zu messen. Durchsatz und Latenz werden oft gegeneinander ausgespielt, und das nicht nur bei Supercomputern. So kann ein System eine Antwort schneller produzieren, aber das andere kann eine Reihe von Antworten in kürzerer Zeit produzieren, selbst wenn Sie etwas länger auf die erste Antwort warten müssen.

Da Anwendungen jetzt auf mehr als 1 Million Kerne in der kommerziellen Cloud skaliert werden können, ist der Aufbau eines HPC für die Größe kein Problem mehr. Es ist an der Zeit, Ergebnisse zu erzielen, und das gilt insbesondere für Aufgaben, die möglichst zeitnahe Ergebnisse erfordern. Das bedeutet, dass HPC wahrscheinlich weiterhin für Aufgaben wie den Finanzhandel verwendet wird, bei denen das Schlagen Ihres Gegners auch nur mit dem geringsten Vorsprung bedeutet, dass Sie gewinnen und er verliert – manchmal geht es um riesige Geldsummen.

Ausgleich des Systems

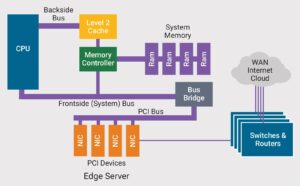

Beim Bau eines Computers müssen viele Faktoren richtig ausbalanciert sein. „Wenn man sich HPC ansieht, konzentriert man sich oft auf Dinge wie Taktraten, Anzahl der Kerne, Skalierbarkeit der Kerne mit der dazugehörigen Verbindung“, sagt Frank Schirrmeister, Vice President of Solutions and Business Development bei Arteris-IP. „Aber Speicherbandbreite, Energieeffizienz und die Möglichkeit, eigene Vektorbefehle hinzuzufügen, sind ebenso wichtig.“

Es muss als Datenflussproblem betrachtet werden. „Die Daten beginnen irgendwo, sie müssen aus dem Speicher in einen Prozessor geladen, von einem Prozessor oder Beschleuniger bearbeitet und dann wieder in den Speicher gestellt werden“, sagt Aitken von Synopsys. „Es ist dieser ganze Weg, wo die Engpässe bestehen. Der „Uncore“ ist ein wichtiger Teil davon, das Gedächtnissystem ist ein wichtiger Teil davon. Sie müssen bei der Lösung einer bestimmten Aufgabe erkennen, wo die Engpässe in der Systemarchitektur liegen. Dies ist unabhängig von der CPU. Im Unternehmensbereich untersucht die Welt dies für RISC-V und arbeitet daran, aber es ist noch nicht unbedingt soweit.“

In vielen Fällen findet die eigentliche Innovation im Uncore statt. „Wenn Sie sich einen Cluster ansehen, sind viele Prozessoren miteinander verbunden“, sagt Schirrmeister von Arteris. „Hier müssen Sie die Skalierbarkeit der Kerne berücksichtigen, und das bedeutet, die Kerne und die Verbindung gemeinsam zu optimieren. RISC-V gibt Ihnen die Freiheit, auf diesem Niveau innovativ zu sein, wahrscheinlich etwas besser als einige der Standardlizenzen. Aber es ist eine Menge Arbeit, und es ist sicherlich nicht trivial. Und es ist Teil des Geheimrezepts, wie dieser Cluster funktionieren wird, wenn er integriert ist.“

Viele Aufgaben, wie KI/ML, werden heutzutage von benutzerdefinierten Beschleunigern unterstützt, und die Allzweckkerne tun möglicherweise kaum mehr als Planungs- und Koordinationsaufgaben. „Sie müssen eine domänenspezifische Beschleunigung durchführen oder verschiedene Beschleuniger verwenden, um die wachsende Rechenleistung zu bewältigen, die in diesen Rechenzentren benötigt wird“, sagt Travis Lanier, Vizepräsident bei Ventana. „Das wird man mit generischen CPUs nicht schaffen.“

Andere stimmen zu. „Kernleistung ist ein wesentlicher Faktor“, sagt Arms Lecomber. „Eine HPC-fähige CPU benötigt eine gute Vektorleistung und Speicherbandbreite pro Kern. Schließlich, aber ebenso entscheidend, müssen HPC-fähige CPUs Effizienz liefern. Entwickler benötigen Programmiereffizienz, um die maximale Leistung aus verfügbaren Kernen und Beschleunigern herauszuholen. Die Energieeffizienz auf Rack-Ebene und im Rechenzentrum wird zu einem einschränkenden Design- und Betriebsfaktor.“

Wie Silizium abschneidet, hängt nicht nur von der ISA oder gar der RTL ab. „Wenn Sie sich irgendein geistiges Eigentum ansehen, liegt sein Erfolg oft an den Verbindungen zu den physischen Werkzeugen, dem physischen Bewusstsein der Dinge“, sagt Schirrmeister. „Selbst für unseren Teil erfordert die Verbindung, die ein Teil des Systems ist, eine Co-Optimierung der IP mit dem Implementierungsfluss, um die richtige Leistung und Leistung zu erzielen. Dasselbe gilt für RISC-V, um es HPC-fähig zu machen. Es ist nicht so einfach, aber es gab Ankündigungen für Prozessoren, die direkt gegen einige der anderen Kerne im Rechenzentrum zu gehen scheinen.“

Die Leistung hängt nicht nur von der Hardware ab. Es kann lange dauern, Software für eine bestimmte Hardware zu portieren und zu optimieren, und dafür ist das richtige Ökosystem erforderlich. „Arm war sehr schlau bei der Vorbereitung des Ökosystems“, fügt Schirrmeister hinzu. „Ökosysteme konzentrieren sich auf unterschiedliche Architekturen wie x86, ArmV9 und jetzt RISC-V. Es hat immer eine Weile gedauert, bis diese Ökosysteme bereit waren und alles unterstützt wurde. Das alles braucht Zeit, um das zu entwickeln und zu stabilisieren. Ich würde sagen, es ist wahrscheinlich noch am Anfang von RISC-V. Ja, die Dynamik ist groß und wir kommen potenziell viel schneller ans Ziel als in der Vergangenheit. RISC-V profitiert von dem, was mit Arm vor sich ging, weil man daraus lernen kann, was es brauchte, um in der Tür Fuß zu fassen.“

Unterstützung der Industrie

Es gibt eindeutig noch viel zu tun, um RISC-V für HPC bereit zu machen. Um die Diskussion und die notwendige Arbeit zu erleichtern, hat das RISC-V-Konsortium eine Special Interest Group on High Performance Computing (SIG-HPC). Die Ziele dieser Gruppe bestehen darin, die Anforderungen der HPC-Community zu erfüllen und die RISC-V ISA auszurichten. Laut ihrer Website begannen sie mit einer Definition des Umfangs, und die Interessen der SIG-HPC wurden in eine Rangfolge gebracht, um Ergebnisse mit hoher Wirkung zu liefern, von der Entdeckung und Lückenanalyse bis zur Implementierung. Um dies zu erreichen, waren zwei Dinge erforderlich – einen Weg finden, um wettbewerbsfähig zu werden, und diesen Weg erweitern, um die Community mit neuen Funktionen und Fähigkeiten anzuführen.

Es tut sich auch viel in der Branche, die zeigt, wohin sich einige Unternehmen bewegen. Intel hat stark in das Barcelona Supercomputing Centre investiert. Es kündigte eine Investition von 400 Millionen Euro in ein neues Labor an, das der Entwicklung von RISC-V-Prozessoren und Supercomputing gewidmet ist. Jeff McVeigh, Vice President und General Manager der Supercomputing Group von Intel, sagte jedoch in einer zugehörigen Pressemitteilung, dass „RISC-V für HPC noch viele Jahre entfernt ist“.

Ihr Ziel ist es, innerhalb von fünf Jahren Systeme der Zettascale-Klasse zu bauen, die um Größenordnungen schneller sind als die heutigen Supercomputer.

Ein weiterer Entwickler von Hochleistungsprozessoren, MIPS, gab im vergangenen Jahr bekannt, dass er auf die Entwicklung von Prozessoren mit RISC-V umgestiegen sei. MIPS gab die Verfügbarkeit seines ersten Kerns auf Basis von RISC-V ISA bekannt, der derzeit für Anwendungen wie Fahrerassistenzsysteme und autonomes Fahren lizenziert wird. Aber MIPS sagt, dass Prozessorkerne auch für Rechenzentren, Speicher und Hochleistungsrechnen verwendet werden könnten.

Wie bei der Softwareentwicklung ist man mit 90 % erst halb fertig. Wie Tom Cargill von Bell Labs einmal berühmt sagte: „Die ersten 90 % des Codes machen die ersten 90 % der Entwicklungszeit aus. Die restlichen 10 % des Codes machen die anderen 90 % der Entwicklungszeit aus.“

Verbunden

RISC-V entkoppelte Vektorverarbeitungseinheit (VPU) für HPC

„Vitruvius+: An Area-Efficient RISC-V De Coupled Vector Coprocessor for High Performance Computing Applications“, veröffentlicht von Forschern am Barcelona Supercomputing Center.

RISC-V zielt auf Rechenzentren ab

Mit zunehmender Reife des Ökosystems gewinnt die Open-Source-Architektur bei komplexeren Designs zunehmend an Bedeutung.

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- Platoblockkette. Web3-Metaverse-Intelligenz. Wissen verstärkt. Hier zugreifen.

- Quelle: https://semiengineering.com/is-risc-v-ready-for-supercomputing/

- 1

- 2016

- 2020

- a

- Fähigkeit

- Fähig

- Über Uns

- Absolute

- Beschleunigung

- Beschleuniger

- Beschleuniger

- erreichen

- Nach

- Trading Konten

- Adresse

- Fügt

- Adoption

- gegen

- AI / ML

- Alle

- Alternativen

- immer

- Analyse

- und

- angekündigt

- Ankündigungen

- Ein anderer

- beantworten

- Antworten

- jemand

- erscheinen

- Anwendungen

- Ansatz

- Architektur

- ARM

- um

- Hilfe

- damit verbundenen

- attraktiv

- Automobilindustrie

- Autonom

- Verfügbarkeit

- verfügbar

- Bewusstsein

- Zurück

- Bandbreite

- Barcelona

- basierend

- basic

- weil

- werden

- Werden

- Ungetüme

- Sein

- Bell

- Benchmark

- Vorteile

- BESTE

- Best Practices

- Besser

- Big

- Bit

- bauen

- Building

- Geschäft

- Geschäftsentwicklung

- Fähigkeiten

- Cargill

- Fälle

- Center

- zentriert

- Centers

- Zentrum

- sicherlich

- challenges

- Ändern

- Chef

- Chip

- Pommes frites

- Wahl

- Uhr

- Menu

- Cloud

- Cluster

- Code

- kommerziell

- community

- Unternehmen

- verglichen

- wettbewerbsfähig

- Komplex

- Berechnung

- Computer

- Computerwissenschaften

- Computer

- Computing

- Verbindungen

- Geht davon

- Berücksichtigung

- betrachtet

- konsistent

- Konsortium

- fortsetzen

- umstritten

- Koordination

- Kernbereich

- könnte

- CPU

- erstellen

- erstellt

- schafft

- kritischem

- Strom

- Zur Zeit

- Original

- technische Daten

- Data Center

- Rechenzentren

- Christian

- Tage

- gewidmet

- definiert

- Übergeben

- Lieferanten

- abhängig

- Bereitstellen

- Design

- Designs

- entwickeln

- Entwickler:in / Unternehmen

- Entwickler

- Entwicklung

- Entwicklung

- anders

- schwer

- Direkt

- Direktor

- Entdeckung

- Diskussion

- Dabei

- Von

- Fahrer

- Fahren

- jeder

- Früh

- Ökosystem

- Ecosystems

- Effizienz

- entweder

- genug

- eingegeben

- Unternehmen

- vollständig

- gleichermaßen

- Era

- insbesondere

- Sogar

- Jedes

- jedermann

- alles

- sich entwickelnden

- Beispiel

- Erweitern Sie die Funktionalität der

- erweitern

- Erweiterungen

- umfangreiche

- Extrakt

- erleichtern

- Faktoren

- prächtig

- beschleunigt

- schnellsten

- Eigenschaften

- Kerl

- wenige

- Endlich

- Revolution

- fest

- Vorname

- fixiert

- Flexibilität

- Fluss

- konzentriert

- vorwärts

- gefunden

- Freiheit

- für

- Grenze

- Funktionen

- gewinnen

- Zocken

- Lücke

- Allgemeines

- allgemeiner Zweck

- bekommen

- bekommen

- Riese

- gegeben

- gibt

- Ziele

- gehen

- gut

- der Regierung

- Gruppe an

- Gruppen

- persönlichem Wachstum

- Richtlinien

- Griff

- das passiert

- Hardware

- Überschrift

- schwer

- Hilfe

- hier

- GUTE

- Hochleistungsrechnen

- Hohe Leistungsfähigkeit

- hoch

- gehostet

- Ultraschall

- Hilfe

- aber

- hpc

- HTTPS

- identifizieren

- Implementierung

- wichtig

- zu unterstützen,

- in

- zunehmend

- unabhängig

- Energiegewinnung

- Infrastruktur

- wir innovieren

- Innovation

- Anleitung

- integriert

- Intel

- verbunden

- Interesse

- Interessen

- investiert

- Investition

- IP

- Problem

- Probleme

- IT

- selbst

- Jack

- Japans

- Wesentliche

- Labor

- Labs

- Nachname

- Letztes Jahr

- Latency

- führen

- Führer

- LERNEN

- Niveau

- Zugelassen

- Lizenzen

- wahrscheinlich

- Line

- Liste

- wenig

- Lang

- lange Zeit

- länger

- aussehen

- sah

- suchen

- verlieren

- Los

- Maschine

- Maschinen

- um

- MACHT

- Manager

- viele

- Marge

- Marketing

- massiv

- reift

- Mittel

- messen

- Memory

- Metrik

- könnte

- Million

- Fehler

- Schwung

- Geld

- mehr

- vor allem warme

- Notwendig

- notwendig,

- Need

- erforderlich

- Bedürfnisse

- Neu

- Neue Funktionen

- Anzahl

- Ziel

- Offizier

- EINEM

- XNUMXh geöffnet

- Open-Source-

- betreiben

- Betriebs-

- Optimieren

- optimiert

- Auftrag

- Bestellungen

- Urheber

- Andere

- Übertreffen

- besitzen

- Teil

- passt

- Weg

- AUFMERKSAMKEIT

- Personen

- Leistung

- führt

- physikalisch

- Stück

- Ort

- Plato

- Datenintelligenz von Plato

- PlatoData

- Play

- Points

- möglich

- möglicherweise

- Werkzeuge

- angetriebene

- größte treibende

- Praktiken

- bereit

- Präsident

- Presse

- Pressemitteilung

- wahrscheinlich

- Aufgabenstellung:

- Probleme

- Verarbeitung

- Prozessor

- Prozessoren

- produziert

- Professor

- Programmierung

- Programme

- richtig

- die

- Bereitstellung

- veröffentlicht

- Publishing

- geschoben

- setzen

- Frage

- Fragen

- wirft

- bereit

- echt

- Echtzeit

- Gründe

- kürzlich

- Referenzen

- bezeichnet

- bezogene

- Release

- zuverlässig

- bleiben

- verbleibenden

- vertreten

- erfordern

- Voraussetzungen:

- erfordert

- Forscher

- Die Ergebnisse

- Risiko

- Rollen

- Wurzel

- Said

- gleich

- sagt

- Skalierbarkeit

- Skalieren

- Wissenschaft

- Umfang

- Die Geheime

- Sicherheitdienst

- Senior

- Sinn

- Modellreihe

- dient

- kompensieren

- mehrere

- erklären

- Silizium

- ähnlich

- Einfacher

- Single

- Größe

- smart

- So

- Software

- Software-Entwicklung

- Lösungen

- Auflösung

- einige

- etwas

- irgendwo

- Raumfahrt

- spricht

- besondere

- spezifisch

- Geschwindigkeiten

- Spot

- stabilisieren

- stabil

- Stufe

- Standard

- Normen

- begonnen

- beginnt

- Immer noch

- Lagerung

- Erfolg

- erfolgreich

- so

- geeignet

- Suite

- Supercomputer

- Supercomputer

- Supercomputing

- Support

- Unterstützte

- Supreme

- Schwall

- schaltet

- System

- Systeme und Techniken

- Tabelle

- zugeschnitten

- Nehmen

- nimmt

- Ziele

- Aufgabe

- und Aufgaben

- Technische

- Das

- die Welt

- ihr

- Ding

- Durchsatz

- Zeit

- Titan

- zu

- heute

- Werkzeuge

- Top

- Zugkraft

- Trading

- was immer dies auch sein sollte.

- Vertrauen

- WENDE

- typisch

- uns

- US-Regierung

- Einheit

- Universität

- -

- verschiedene

- riesig

- Vizepräsident:in

- warten

- wollte

- Webseite

- Was

- Rad

- ob

- welche

- während

- WHO

- weit

- Wikipedia

- werden wir

- bereit

- gewinnen

- .

- Arbeiten

- gearbeitet

- arbeiten,

- Arbeitsgruppen

- weltweit wie ausgehandelt und gekauft ausgeführt wird.

- weltweit

- würde

- Jahr

- Jahr

- Ihr

- Zephyrnet