Um die Ausbreitung systematischer Fehler im heutigen Prozess vom Entwurf bis zur Fertigung von Halbleitern zu verhindern, sind viele Validierungs-, Analyse- und Optimierungsschritte erforderlich. Zu den an diesem Prozess beteiligten Werkzeugen können Design Rule Checking (DRC), optische Proximity Correction (OPC)-Verifizierung, Maskenschreiben und Waferdruck-Messtechnik/-Inspektion (zur Messung des Prozesses), Wafer-Druckmesstechnik/-inspektion und physische Fehleranalyse zur Fehlerbestätigung gehören Diagnose. Der Informationsaustausch und die Co-Optimierung zwischen diesen Schritten ist ein komplexer Prozess mit vielen Feed-Forward- und Feedback-Schleifen. Die Kommunikation wird häufig durch „Mauern“ zwischen verschiedenen Teilen der Prozesstechnologie behindert, was die Innovation verlangsamt. Auf der jüngsten SPIE-Konferenz hielt Siemens EDA eine Grundsatzrede, in der eine Reihe von Ansätzen zur Überwindung dieser Hürden vorgeschlagen wurde, um den Chip-Design- und Fertigungsprozess zu verbessern. Lesen Sie weiter und erfahren Sie, wie Siemens durch die Ausweitung der Co-Optimierung von Designtechnologien Innovationsbarrieren abbauen will.

Über die Keynote

SPIE ist die internationale Gesellschaft für Optik und Photonik. Die Gründung der Organisation geht auf das Jahr 1955 zurück und ihre Konferenz hat sich zu einer führenden Veranstaltung für fortgeschrittene Design- und Fertigungsthemen entwickelt. Auf der diesjährigen Veranstaltung hielt Siemens die Keynote, die Gegenstand dieses Beitrags ist. Es gab viele Mitwirkende an der Präsentation, darunter Le Hong, Fan Jiang, Yuansheng Ma, Srividya Jayaram, Joe Kwan, Siemens EDA (USA); Doohwan Kwak, Siemens EDA (Republik Korea); Sankaranarayanan Paninjath Ayyappan, Siemens EDA (Indien). Der Titel des Vortrags war Ausweitung der Co-Optimierung der Designtechnologie von der Technologieeinführung bis hin zu HVM.

Der Vortrag war Teil einer Sitzung zum Thema Design Technology Co-Optimization (DTCO). Dieses Konzept ist nicht neu, aber Siemens untersuchte seine Anwendung in einem breiteren Bereich des Prozesses, vom Design bis zur Großserienfertigung (HVM). Die vorgestellten Ideen und Ergebnisse haben erhebliche Auswirkungen. Lass uns genauer hinschauen.

Was wurde präsentiert

Zunächst wurde ein Blick auf den aktuellen Stand der DTCO-Nutzung in wichtigen Teilen des Ökosystems gegeben. Aus gestalterischer Sicht verfügen viele fortschrittliche Fabless-Unternehmen über ein DFM-Team, das die Grenzen eines musterbasierten Ansatzes erkennt. Was wirklich benötigt wird, ist eine neue Technologie, die das Yield-Learning ohne Abhängigkeit von der Gießerei ermöglicht.

Die Gießereien verwenden auf Brute-Force-Mustern basierende maschinelle Lernansätze, die kostspielig, aber nicht vollständig effektiv sind. Sie streben außerdem nach einer effizienten Informationsgewinnung aus den riesigen Fertigungsdaten, die sie erstellen. Gerätehersteller und EDA-Anbieter arbeiten enger zusammen und entwickeln effizientere Lösungen für maschinelles Lernen.

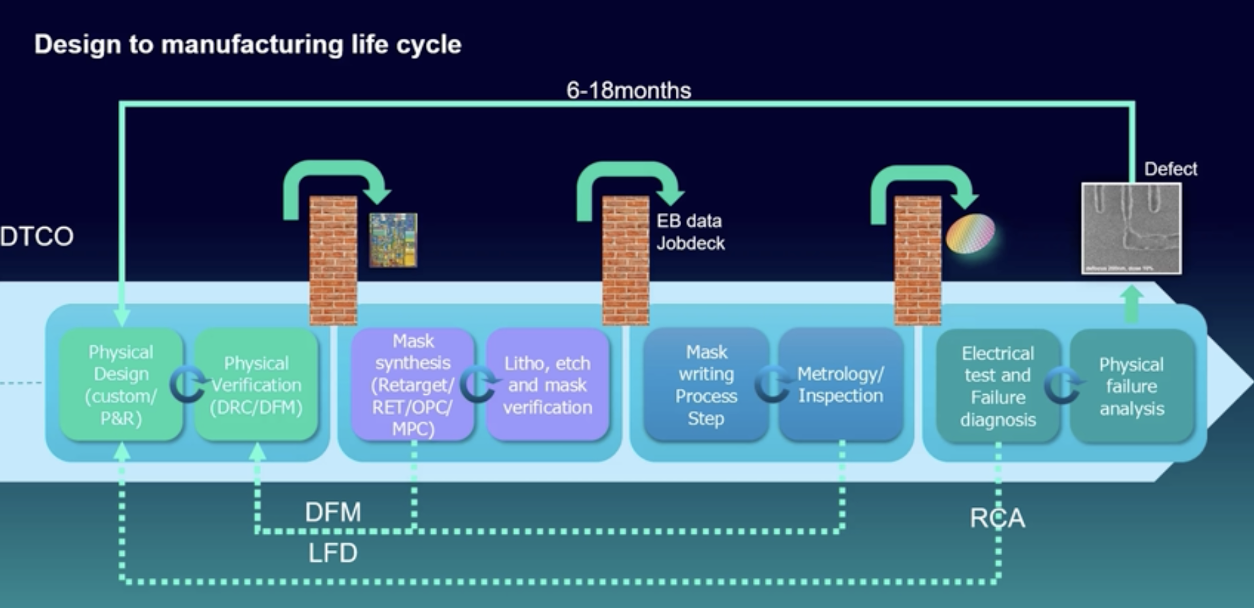

Etwas zurückhaltend wurde darauf hingewiesen, dass zwischen der Entwurfs- und der Herstellungsphase des Prozesses Mauern bestehen. Fabless-Unternehmen erstellen das Design, führen DRC und Design for Manufacturing (DFM) durch und übermitteln es dann über die Mauer an das OPC/RET-Team innerhalb der Gießerei oder des IDM. Beim Design werden Aufgaben wie OPC und Verifizierung erledigt, und dann werden die Daten zum Maskenschreiben und zur Messtechnik/Inspektion über eine andere Wand geworfen. Die letzte Wand dient der Fertigung. Hier werden elektrische Tests und Fehleranalysen durchgeführt. Bis die Grundursache des Fehlers gefunden ist, sind 6 bis 18 Monate vergangen. Das ist eine sehr lange Feedbackschleife. Die Grafik oben in diesem Beitrag zeigt diesen Prozess.

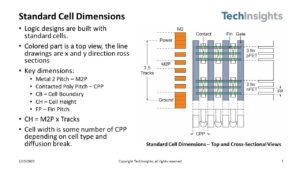

DTCO versucht, die Mauern einzureißen, aber die verfügbaren Methoden sind unvollständig. Traditionelle DTCO beginnt sehr früh in der Prozessentwicklung. Ausgehend von einem Skalierungsbedarf wird eine Standardzelle definiert und Synthese, Ort und Route durchgeführt, um grundlegende Muster zu erstellen und die Leistung und Leistung zu messen. Das SRAM-Yerving wird ebenfalls durchgeführt und die Daten werden auf das Standardzellendesign zurückgeführt.

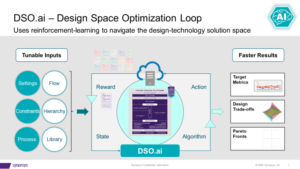

Bei der SPIE-Keynote wurde eine Möglichkeit vorgestellt, dieses Co-Optimierungskonzept auf den gesamten Prozess vom Design bis zur Fertigung auszuweiten. Der Ansatz besteht darin, durch die Schaffung eines Informationskanals einen einfacheren Informationsfluss vom Entwurf bis zum endgültigen Prozess und der physikalischen Analyse zu ermöglichen.

Das klingt zwar einfach, ist es aber nicht. Viele Herausforderungen wurden mit konkreten Lösungsansätzen zur Lösung der Probleme besprochen. Beispielsweise können frühe Designs mit Layout-Synthesegeneratoren erstellt werden, um den Prozess während der Prozessentwicklung an reale Designprobleme anzupassen. Dies kann viele der Überraschungen lindern, die derzeit mit frühen Prozess-Tapeouts einhergehen.

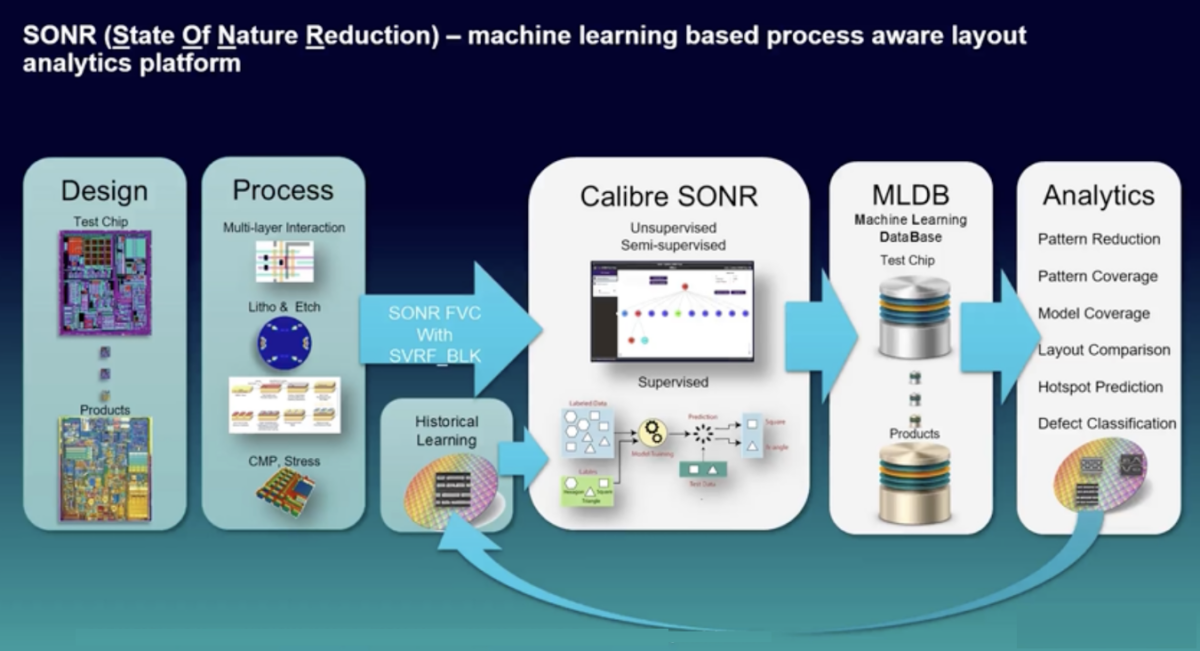

Eine weitere Herausforderung ist der Umgang mit riesigen Datenmengen. Durch den Einsatz neuer hochentwickelter Komprimierungstechniken ist eine 30-fache Verbesserung möglich. Dies verbessert die Datenverarbeitung und Analyseaufgaben erheblich. Ein Konzept namens erklärbare KI kann helfen, die Ursachen von Problemen viel schneller zu finden. Die Möglichkeit, KI-Modelle später im Herstellungsprozess neu zu trainieren, ohne frühere Ergebnisse ungültig zu machen, ist ein weiterer Bereich mit Verbesserungspotenzial. Auch im Bereich der Datenanalyse gibt es Techniken zum Umgang mit „unausgeglichenen Daten“. Beispielsweise kann in 100,000,000 Mustern ein Hotspot gefunden werden.

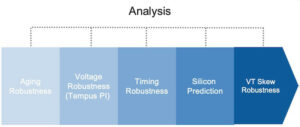

Wenn man all dies zusammennimmt, kann ein wesentlich effizienterer End-to-End-Designablauf entstehen, wie in der Abbildung unten dargestellt.

Um mehr zu lernen

Die Wirkung der in dieser Keynote-Präsentation vorgestellten Ansätze ist erheblich. Du kannst Sehen Sie sich hier die Präsentation an und greifen Sie auf ein Whitepaper zum Prozess zu. Es gibt viele nützliche Informationen zu gewinnen. Und so will Siemens Innovationsbarrieren abbauen, indem es die Co-Optimierung von Designtechnologien ausweitet.

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiwiki.com/events/339386-spie-2023-buzz-siemens-aims-to-break-down-innovation-barriers-by-extending-design-technology-co-optimization/

- :hast

- :Ist

- :nicht

- $UP

- 000

- 100

- 2023

- a

- Fähigkeit

- Zugang

- über

- Adresse

- advanced

- AI

- KI-Modelle

- Ziel

- Alle

- lindern

- ebenfalls

- an

- Analyse

- und

- Ein anderer

- Anwendung

- Ansatz

- Ansätze

- SIND

- Bereich

- AS

- At

- Versuche

- verfügbar

- Zurück

- Barrieren

- basic

- BE

- werden

- war

- unten

- zwischen

- Bit

- Break

- breiteres

- aber

- by

- namens

- CAN

- Verursachen

- Ursachen

- Zelle

- challenges

- Herausforderungen

- Kanal

- Überprüfung

- Chip

- näher

- CO

- wie die

- Kommen

- Kommunikation

- Unternehmen

- uneingeschränkt

- Komplex

- konzept

- Beton

- Konferenz

- Schichtannahme

- mitwirkende

- teuer werden

- erstellen

- erstellt

- Erstellen

- Strom

- Aktuellen Zustand

- Zur Zeit

- technische Daten

- Datenanalyse

- Datum

- Deal

- definiert

- Abhängigkeit

- Design

- Designs

- Details

- entwickelt

- Entwicklung

- Diagnose

- diskutiert

- erledigt

- nach unten

- drc

- Früher

- Früh

- einfacher

- Ökosystem

- Effektiv

- effizient

- ermöglichen

- End-to-End

- Ganz

- Ausrüstung

- Event

- Beispiel

- Austausch-

- erweitern

- Verlängerung

- konfrontiert

- erleichtern

- Scheitern

- Fan

- beschleunigt

- Feedback

- Abbildung

- Finale

- Finden Sie

- Fluss

- Aussichten für

- gefunden

- Giesserei

- für

- gewonnen

- Spur

- Generatoren

- Grafik

- Handling

- Haben

- Hilfe

- hier

- Hong

- HEISS

- Ultraschall

- HTTPS

- Ideen

- Impact der HXNUMXO Observatorien

- Auswirkungen

- zu unterstützen,

- Verbesserung

- verbessert

- in

- das

- Einschließlich

- Indien

- Information

- Innovation

- International

- beteiligt

- beinhaltet

- Probleme

- IT

- SEINE

- joe

- Wesentliche

- Keynote

- Korea

- später

- starten

- Layout

- LERNEN

- lernen

- Grenzen

- Lang

- aussehen

- sah

- Los

- Maschine

- Maschinelles Lernen

- Herstellung

- viele

- Maske"

- massiv

- max-width

- Kann..

- messen

- Methodologien

- Bergbau

- Mildern

- für

- Monat

- mehr

- effizienter

- viel

- Need

- erforderlich

- Neu

- of

- vorgenommen,

- on

- EINEM

- Optik

- Optik und Photonik

- Optimierung

- or

- Organisation

- skizzierte

- übrig

- Papier

- Teil

- Teile

- Bestanden

- Muster

- ausführen

- Leistung

- durchgeführt

- Perspektive

- physikalisch

- Ort

- Plattform

- Plato

- Datenintelligenz von Plato

- PlatoData

- möglich

- Post

- Werkzeuge

- Premier

- presentation

- vorgeführt

- Probleme

- Prozessdefinierung

- Fortpflanzung

- vorgeschlage

- ganz

- Lesen Sie mehr

- echt

- wirklich

- kürzlich

- Republik

- erfordert

- Die Ergebnisse

- Wurzel

- Straße

- Regel

- Skalierung

- Umfang

- sehen

- Sehen

- auf der Suche nach

- Halbleiter

- Modellreihe

- Sitzung

- gezeigt

- Siemens

- signifikant

- Verlangsamung

- Gesellschaft

- Lösungen

- anspruchsvoll

- Spot

- Standard

- Beginnen Sie

- beginnt

- Bundesstaat

- Staaten

- Shritte

- wesentlich

- so

- Überraschungen

- Synthese

- synthetisch

- Nehmen

- Reden

- und Aufgaben

- Team

- Techniken

- Technologie

- Test

- zur Verbesserung der Gesundheitsgerechtigkeit

- Das

- dann

- Dort.

- Diese

- vom Nutzer definierten

- fehlen uns die Worte.

- Zeit

- Titel

- zu

- heutigen

- gemeinsam

- Werkzeuge

- Top

- Thema

- Themen

- werfen

- geworfen

- traditionell

- Vereinigt

- USA

- Anwendungsbereich

- nützliche Informationen

- Verwendung von

- Bestätigung

- verschiedene

- Anbieter

- Verification

- sehr

- Volumen

- Pinnwand

- wurde

- Weg..

- waren

- Was

- Was ist

- welche

- Weiß

- WHITE PAPER

- werden wir

- mit

- .

- ohne

- arbeiten,

- Schreiben

- Ausbeute

- nachgiebig

- U

- Zephyrnet